|

|

PDF DS32ELX0421 Data sheet ( Hoja de datos )

| Número de pieza | DS32ELX0421 | |

| Descripción | Serializer | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DS32ELX0421 (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

PRELIMINARY

May 9, 2008

DS32EL0421, DS32ELX0421

125 – 312.5 MHz Serializer with DDR LVDS Parallel LVDS

Interface

General Description

The DS32EL0421/DS32ELX0421 is a 125 MHz to 312.5 MHz

(DDR) serializer for high-speed serial transmission over FR-4

printed circuit board backplanes, balanced cables, and optical

fiber. This easy-to-use chipset integrates advanced signal

and clock conditioning functions, with an FPGA friendly inter-

www.DataSheefta4cUe..com

The DS32EL0421/DS32ELX0421 serializes up to 5 parallel

input LVDS channels to create a maximum data payload of

3.125 Gbps. If the integrated DC-balance encoding is en-

abled, the maximum data payload achievable is 2.5 Gbps.

The DS32EL0421/DS32ELX0421 serializers feature remote

sense capability to automatically detect and negotiate link

status with its companion DS32EL0124/DS32ELX0124 de-

serializers without requiring an additional feedback path.

The parallel LVDS interface reduces FPGA I/O pins, board

trace count and alleviates EMI issues, when compared to tra-

ditional single-ended wide bus interfaces.

The DS32EL0421/DS32ELX0421 is programmable through

a SMBus interface as well as through control pins.

Target Applications

■ Imaging: Industrial, Medical Security, Printers

■ Displays: LED walls, Commercial

■ Video Transport

■ Communication Systems

■ Test and Measurement

■ Industrial Bus

Features

■ 5-bit LVDS parallel data interface

■ Programmable transmit de-emphasis

■ Configurable output levels (VOD)

■ Selectable DC-balanced encoder

■ Selectable data scrambler

■ Remote Sense for automatic detection and negotiation of

link status

■ On chip LC VCOs

■ Redundant serial output (ELX device only)

■ Data valid signaling to assist with synchronization of

multiple receivers

■ Supports AC- and DC-coupled signaling

■ Integrated CML and LVDS terminations

■ Configurable PLL loop bandwidth

■ Programmable output termination (50Ω or 75Ω).

■ Built-in test pattern generator

■ Loss of lock and error reporting

■ Configurable via SMBus

■ 48-pin LLP package with exposed DAP

Key Specifications

■ 1.25 to 3.125 Gbps serial data rate

■ 125 to 312.5 MHz DDR parallel clock

■ -40° to +85°C temperature range

■ >8 kV ESD (HBM) protection

■ Low Intrinsic Jitter — 35ps at 3.125 Gbps

Typical Application

© 2008 National Semiconductor Corporation 300321

30032101

www.national.com

1 page

GPIO1

GPIO2

NC

4 I/O,

Software configurable I/O pin.

LVCMOS

11 I/O,

Software configurable I/O pin.

LVCMOS

2, 8, 12, 13, Misc.

No Connect, for DS32EL0421

19, 20, 21,

22, 23, 24,

29

2, 8, 13, 21, Misc.

22, 23, 24,

No Connect, for DS32ELX0421

29

www.DataSheet4U.com

5 www.national.com

5 Page

www.DataSheet4U.com

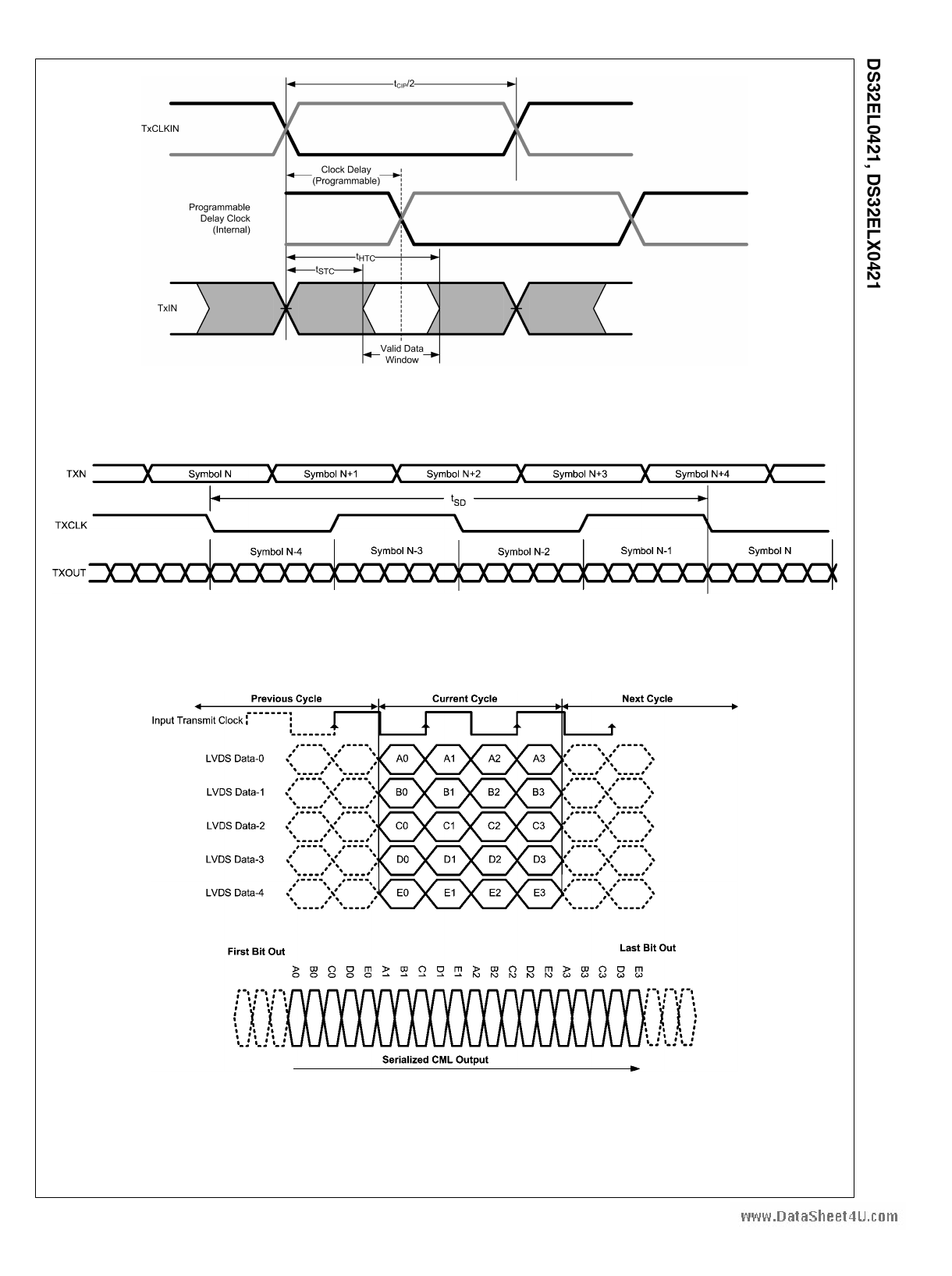

FIGURE 4. LVDS Input Clock Delay

30032113

FIGURE 5. Propagation Delay Timing Diagram

30032112

FIGURE 6. 5-Bit Parallel LVDS Inputs Mapped to CML Output

30032104

11 www.national.com

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet DS32ELX0421.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS32ELX0421 | DS32EL0421/ELX0421 125 - 312.5 MHz FPGA-Link Serializer w/ DDR LVDS Parallel I/F (Rev. F) | Texas Instruments |

| DS32ELX0421 | Serializer | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |