|

|

PDF XCV50E-6CS144C Data sheet ( Hoja de datos )

| Número de pieza | XCV50E-6CS144C | |

| Descripción | Virtex-e Field Programmable Gate Array | |

| Fabricantes | Xilinx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XCV50E-6CS144C (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

R

0

Virtex™-E 1.8 V

Field Programmable Gate Arrays

DS022-1 (v2.3) July 17, 2002

00

Features

• Fast, High-Density 1.8 V FPGA Family

- Densities from 58 k to 4 M system gates

- 130 MHz internal performance (four LUT levels)

- Designed for low-power operation

- PCI compliant 3.3 V, 32/64-bit, 33/ 66-MHz

• Highly Flexible SelectI/O+™ Technology

- Supports 20 high-performance interface standards

- Up to 804 singled-ended I/Os or 344 differential I/O

pairs for an aggregate bandwidth of > 100 Gb/s

• Differential Signalling Support

- LVDS (622 Mb/s), BLVDS (Bus LVDS), LVPECL

- Differential I/O signals can be input, output, or I/O

- Compatible with standard differential devices

- LVPECL and LVDS clock inputs for 300+ MHz

clocks

• Proprietary High-Performance SelectLink™

Technology

- Double Data Rate (DDR) to Virtex-E link

- Web-based HDL generation methodology

• Sophisticated SelectRAM+™ Memory Hierarchy

- 1 Mb of internal configurable distributed RAM

- Up to 832 Kb of synchronous internal block RAM

- True Dual-Port BlockRAM capability

- Memory bandwidth up to 1.66 Tb/s (equivalent

bandwidth of over 100 RAMBUS channels)

- Designed for high-performance Interfaces to

External Memories

- 200 MHz ZBT* SRAMs

- 200 Mb/s DDR SDRAMs

- Supported by free Synthesizable reference design

* ZBT is a trademark of Integrated Device Technology, Inc.

Production Product Specification

• High-Performance Built-In Clock Management Circuitry

- Eight fully digital Delay-Locked Loops (DLLs)

- Digitally-Synthesized 50% duty cycle for Double

Data Rate (DDR) Applications

- Clock Multiply and Divide

- Zero-delay conversion of high-speed LVPECL/LVDS

clocks to any I/O standard

• Flexible Architecture Balances Speed and Density

- Dedicated carry logic for high-speed arithmetic

- Dedicated multiplier support

- Cascade chain for wide-input function

- Abundant registers/latches with clock enable, and

dual synchronous/asynchronous set and reset

- Internal 3-state bussing

- IEEE 1149.1 boundary-scan logic

- Die-temperature sensor diode

• Supported by Xilinx Foundation™ and Alliance Series™

Development Systems

- Further compile time reduction of 50%

- Internet Team Design (ITD) tool ideal for

million-plus gate density designs

- Wide selection of PC and workstation platforms

• SRAM-Based In-System Configuration

- Unlimited re-programmability

• Advanced Packaging Options

- 0.8 mm Chip-scale

- 1.0 mm BGA

- 1.27 mm BGA

- HQ/PQ

• 0.18 µm 6-Layer Metal Process

• 100% Factory Tested

© 2000-2002 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

DS022-1 (v2.3) July 17, 2002

Production Product Specification

www.xilinx.com

1-800-255-7778

Module 1 of 4

1

1 page

R

www.DataSheet4U.com

Virtex™-E 1.8 V Field Programmable Gate Arrays

Date

11/20/00

2/12/01

4/2/01

10/25/01

11/09/01

07/17/02

Version

1.8

1.9

2.0

2.1

2.2

2.3

Revision

• Upgraded speed grade -8 numbers in Virtex-E Electrical Characteristics tables to

Preliminary.

• Updated minimums in Table 13 and added notes to Table 14.

• Added to note 2 to Absolute Maximum Ratings.

• Changed speed grade -8 numbers for TSHCKO32, TREG, TBCCS, and TICKOF.

• Changed all minimum hold times to –0.4 under Global Clock Setup and Hold for

LVTTL Standard, with DLL.

• Revised maximum TDLLPW in -6 speed grade for DLL Timing Parameters.

• Changed GCLK0 to BA22 for FG860 package in Table 46.

• Revised footnote for Table 14.

• Added numbers to Virtex-E Electrical Characteristics tables for XCV1000E and

XCV2000E devices.

• Updated Table 27 and Table 78 to include values for XCV400E and XCV600E devices.

• Revised Table 62 to include pinout information for the XCV400E and XCV600E devices

in the BG560 package.

• Updated footnotes 1 and 2 for Table 76 to include XCV2600E and XCV3200E devices.

• Updated numerous values in Virtex-E Switching Characteristics tables.

• Converted data sheet to modularized format. See the Virtex-E Data Sheet section.

• Updated the Virtex-E Device/Package Combinations and Maximum I/O table to

show XCV3200E in the FG1156 package.

• Minor edits.

• Data sheet designation upgraded from Preliminary to Production.

Virtex-E Data Sheet

The Virtex-E Data Sheet contains the following modules:

• DS022-1, Virtex-E 1.8V FPGAs:

Introduction and Ordering Information (Module 1)

• DS022-2, Virtex-E 1.8V FPGAs:

Functional Description (Module 2)

• DS022-3, Virtex-E 1.8V FPGAs:

DC and Switching Characteristics (Module 3)

• DS022-4, Virtex-E 1.8V FPGAs:

Pinout Tables (Module 4)

DS022-1 (v2.3) July 17, 2002

Production Product Specification

www.xilinx.com

1-800-255-7778

Module 1 of 4

5

5 Page

R

www.DataSheet4U.com

Virtex™-E 1.8 V Field Programmable Gate Arrays

forces a storage element into the initialization state speci-

fied for it in the configuration. BY forces it into the opposite

state. Alternatively, these signals can be configured to oper-

ate asynchronously. All of the control signals are indepen-

dently invertible, and are shared by the two flip-flops within

the slice.

Additional Logic

The F5 multiplexer in each slice combines the function gen-

erator outputs. This combination provides either a function

generator that can implement any 5-input function, a 4:1

multiplexer, or selected functions of up to nine inputs.

Similarly, the F6 multiplexer combines the outputs of all four

function generators in the CLB by selecting one of the

F5-multiplexer outputs. This permits the implementation of

any 6-input function, an 8:1 multiplexer, or selected func-

tions of up to 19 inputs.

Each CLB has four direct feedthrough paths, two per slice.

These paths provide extra data input lines or additional local

routing that does not consume logic resources.

Arithmetic Logic

Dedicated carry logic provides fast arithmetic carry capabil-

ity for high-speed arithmetic functions. The Virtex-E CLB

supports two separate carry chains, one per Slice. The

height of the carry chains is two bits per CLB.

The arithmetic logic includes an XOR gate that allows a

2-bit full adder to be implemented within a slice. In addition,

a dedicated AND gate improves the efficiency of multiplier

implementation. The dedicated carry path can also be used

to cascade function generators for implementing wide logic

functions.

BUFTs

Each Virtex-E CLB contains two 3-state drivers (BUFTs)

that can drive on-chip busses. See Dedicated Routing.

Each Virtex-E BUFT has an independent 3-state control pin

and an independent input pin.

Block SelectRAM

Virtex-E FPGAs incorporate large block SelectRAM memo-

ries. These complement the Distributed SelectRAM memo-

ries that provide shallow RAM structures implemented in

CLBs.

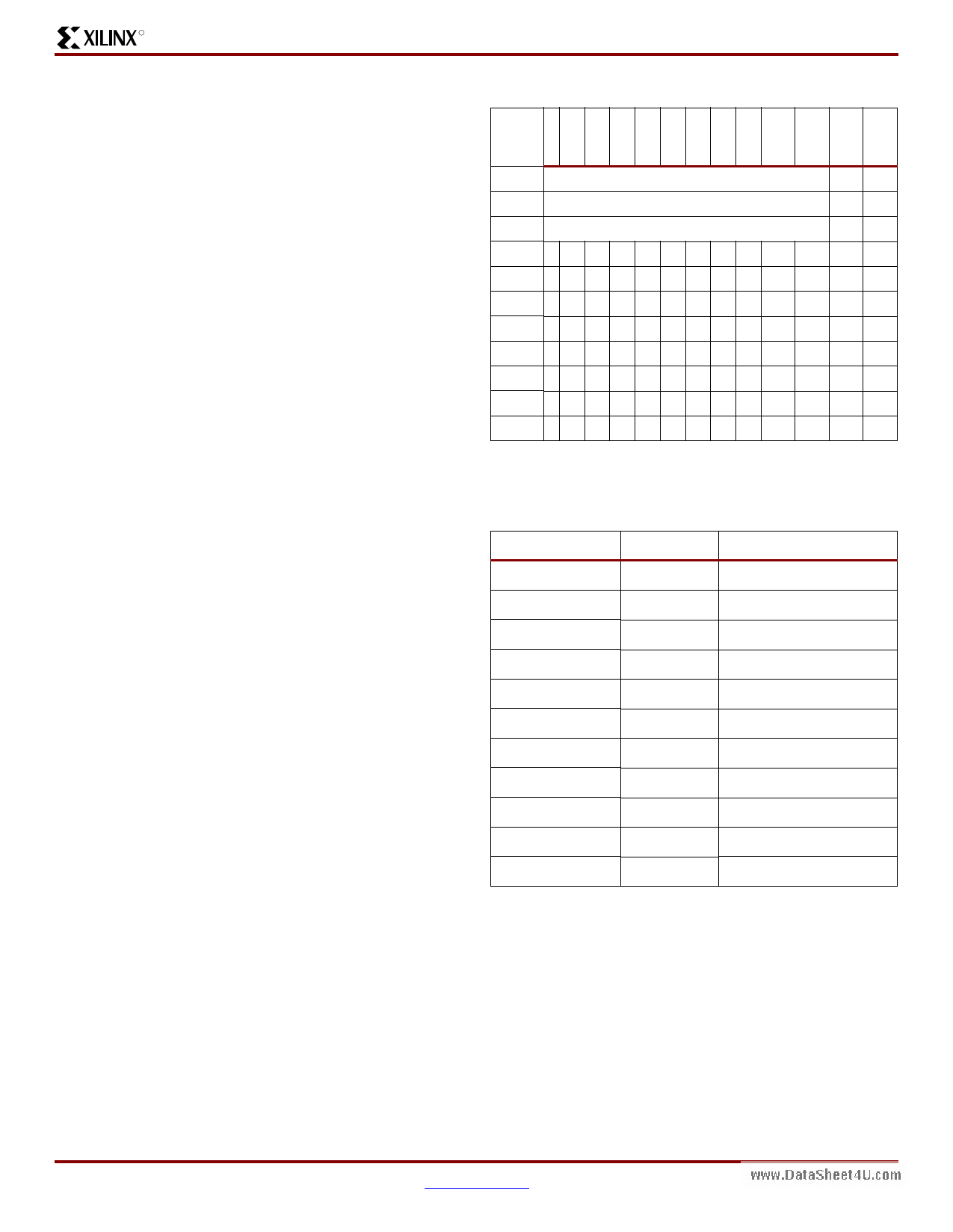

Block SelectRAM memory blocks are organized in columns,

starting at the left (column 0) and right outside edges and

inserted every 12 CLB columns (see notes for smaller

devices). Each memory block is four CLBs high, and each

memory column extends the full height of the chip, immedi-

ately adjacent (to the right, except for column 0) of the CLB

column locations indicated in Table 3.

Table 3: CLB/Block RAM Column Locations

XCV

Device

/Col. 0 12 24 36 48 60 72 84 96 108 120 138 156

50E Columns 0, 6, 18, & 24

100E

Columns 0, 12, 18, & 30

200E

Columns 0, 12, 30, & 42

300E √ √

√√

400E √ √

√√

600E √ √ √

√√√

1000E √ √ √

√√√

1600E √ √ √ √

√√√ √

2000E √ √ √ √

√√ √ √

2600E √ √ √ √

√√ √ √

3200E √ √ √ √

√√√√

Table 4 shows the amount of block SelectRAM memory that

is available in each Virtex-E device.

Table 4: Virtex-E Block SelectRAM Amounts

Virtex-E Device # of Blocks Block SelectRAM Bits

XCV50E

16

65,536

XCV100E

20

81,920

XCV200E

28

114,688

XCV300E

32

131,072

XCV400E

40

163,840

XCV600E

72

294,912

XCV1000E

96

393,216

XCV1600E

144

589,824

XCV2000E

160

655,360

XCV2600E

184

753,664

XCV3200E

208

851,968

As illustrated in Figure 6, each block SelectRAM cell is a

fully synchronous dual-ported (True Dual Port) 4096-bit

RAM with independent control signals for each port. The

data widths of the two ports can be configured indepen-

dently, providing built-in bus-width conversion.

DS022-2 (v2.6) November 19, 2002

Production Product Specification

www.xilinx.com

1-800-255-7778

Module 2 of 4

5

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet XCV50E-6CS144C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XCV50E-6CS144C | Virtex-e Field Programmable Gate Array | Xilinx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |