|

|

PDF LC749450NW Data sheet ( Hoja de datos )

| Número de pieza | LC749450NW | |

| Descripción | Silicon Gate CMOS IC Digital RGB Image Processor IC | |

| Fabricantes | Sanyo Semicon Device | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de LC749450NW (archivo pdf) en la parte inferior de esta página. Total 17 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Ordering number : ENN8096A

SANYO Semiconductors

DATA SHEET

Silicon Gate CMOS IC

LC749450NW Digital RGB Image Processor IC

Overview

The LC749450NW RGB image processing IC converts interlaced video signals such as NTSC and PAL to progressive

scan and adjusts the image quality of that signal. Since the LC749450NW can operate at input clock frequencies up to

27 MHz, it is optimal as a pixel display device IC for high-quality high-resolution images. A high image quality

progressive scan signal playback system can be implemented easily by combining the LC749450NW with external

memory (two 16M SDRAMs).

Features

• Accepts 30-bit (4:4:4) YCbCr signals, 20-bit (4:2:2) YCbCr signals, and 10-bit RT.656 signals as inputs.

• Supports digital TV inputs (480i, 480p, 1080i, and 720p): 30-bit YCbCr digital signal input.

• 30-bit digital RGB signal inputs

• Produces 30-bit and 24-bit digital RGB (or YCbCr) signal outputs

• Provides both YCbCr/YPbPr → RGB conversion and RGB → YCbCr conversion

• Motion adaptive jaggy-less interlaced to progressive conversion

• 3:2 pull down

• Multiple noise reduction systems (1D, 2D, and 3D)

• Cross color and cross luminance cancellers

• Horizontal outline correction (LTI and CTI)

• Sharpness (horizontal and vertical)

• Sharpness adjuster (shading relief enhancement)

• White and black level expansion, white text correction (blue stretch)

• Flesh tone correction

• Hue and color gain adjustments

• Color exciter (6-phase RGBYMC independent saturation adjustment)

• Brightness and contrast adjustment

• White balance and black balance adjustment

• Gamma correction (Independent RGB, programmable LUT system)

• Dithering (10-bit and 8-bit)

• Clamp control

• Aspect ratio conversion (4:3 → 16:9)

• Clock generator (PLL) circuit

• SDRAM interface

• I2C bus and CPU interface circuits

SDPIC™: SANYO Digital Picture Improvement Core

SDPIC™ is a registered trademark of SANYO Electric Co., Ltd.

Any and all SANYO products described or contained herein do not have specifications that can handle

applications that require extremely high levels of reliability, such as life-support systems, aircraft's

control systems, or other applications whose failure can be reasonably expected to result in serious

physical and/or material damage. Consult with your SANYO representative nearest you before using

any SANYO products described or contained herein in such applications.

SANYO assumes no responsibility for equipment failures that result from using products at values that

exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other

parameters) listed in products specifications of any and all SANYO products described or contained

herein.

SANYO Electric Co.,Ltd. Semiconductor Company

TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

70105HK OT B8-7981 No.8096-1/17

1 page

www.DataSheet4U.com

LC749450NW

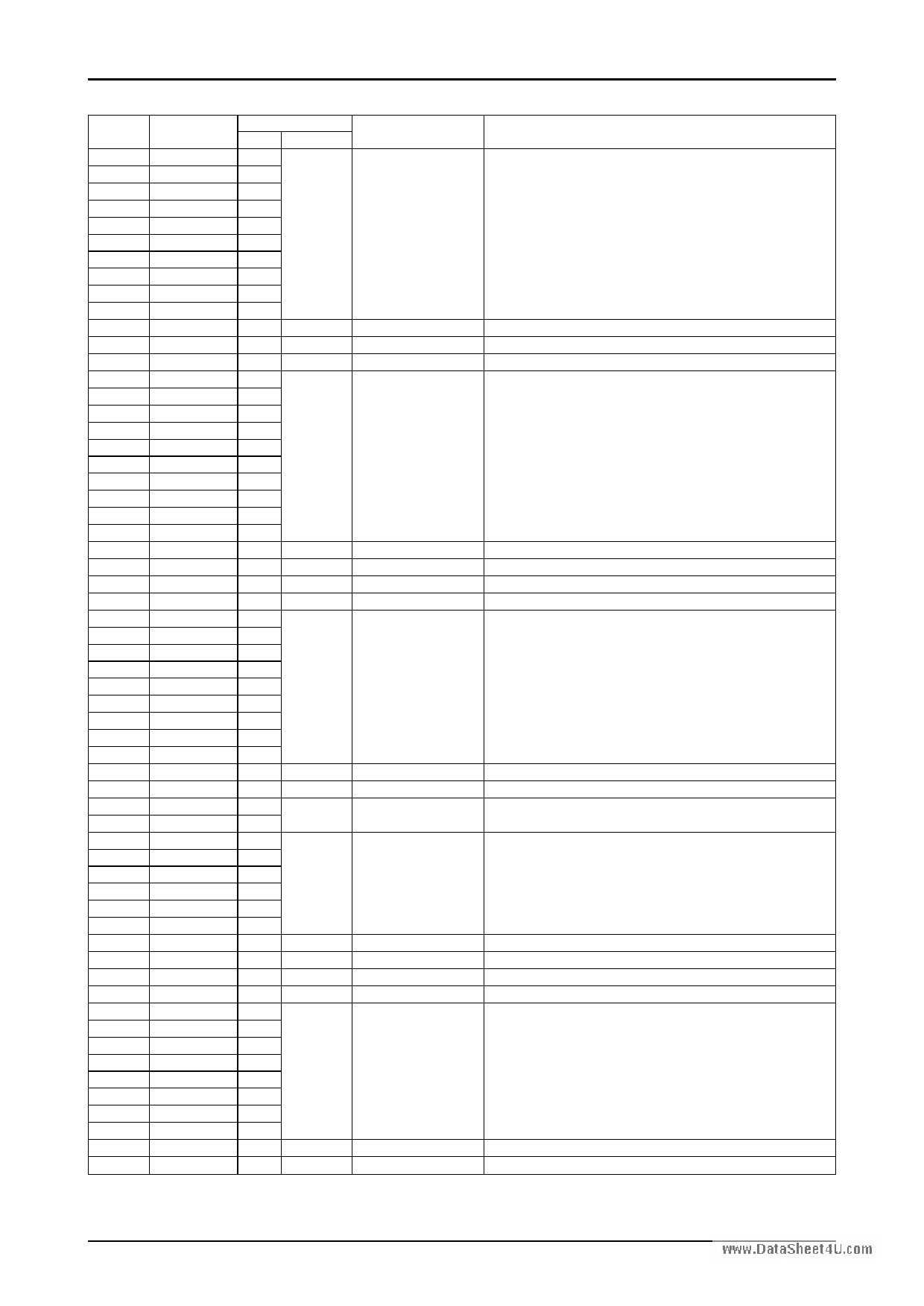

I/O Specifications

Input Signals

Signal type

Video signals

Sync signals

Number of pins

10

10

10

1

1

Data enable

signals

Pixel clock

Fixed oscillator

System reset

Total

1

1

1

1

1

1

1

40

Symbol

YIN

CBI

CRI

DHS

DVS

DEHI

DEVI

FIELD

CLKI

DCLKI

XTAL

XRST

—

Description

Y or G

Cb or B or C

Cr or R or OSD

Horizontal sync signal

Vertical sync signal

Data enable

Vertical data enable

Field signal input

Clock

Used for the output dot clock

System reset

—

Notes

NTSC/PAL/DTV (4801, 480P, 1080I)

or progressive scan RGB (up to SXGA)

or NTSC/PAL decoder input

Pixel sync horizontal sync signal input

The polarity can be switched by setting the DVPOLIN internal register.

Vertical sync signal input

The polarity can be switched by setting the DVPOLIN internal register.

Valid video period enable signal (horizontal/composite)

Valid video period enable signal (vertical)

Field signal input

System clock input

System clock input

Fixed clock input or test clock input

System reset input, active low

—

Output Signals

Signal type

Video signals

Sync signals

Number of pins

10

10

10

1

Symbol

ODG

ODB

ODR

DHO

Description

G

B

R

Horizontal sync signal

Data enable

signals

Pixel clocks

Clamp pulse

signals

Clamp levels

Field

discrimination

signals

Total

1 DVO Vertical sync signal

1 AREA Data enable

1 CLKOUT Outputs the input clock

1 CLAMPO For A/D conversion

1 CLPG Y/G clamp level

1 CLPB Cb/B clamp level

1 CLPR Cr/R clamp level

1 ODEVPPO Field discrimination

39 — —

Notes

RGB output

The LC749450NW also supports dithered 8-bit output.

This pin outputs the DHS pin input after a delay. (Used for pixel sync.)

(This can be set over the I2C bus.)

Outputs a vertical pixel sync signal.

Outputs a valid area signal.

The polarity can be inverted.

Outputs a pulse signal used for A/D conversion clamp period verification

Clamp level discrimination output

(Too large: low, too small: high, match: high-impedance)

Outputs an odd/even field discrimination signal

(Used when IP conversion is not used.)

—

Control Signals

Signal type

I2C bus signals

Number of pins

1

1

1

Symbol

SDAIO

SCLI

SLADR

Description

Data bus

Bus clock

Slave switching

Data output

signals

XTAL

1 OE

1 XTALSW

Total

5 ——

Notes

Used for setting internal registers and reading out the internal status.

The slave address is “1110000+(R/W)”.

Sets the I2C bus slave address.

Normally low, High: E2h, Low: E0h.

Data output enable signal

This signal sets the XTAL clock pin input operation

High: The XTAL clock input signal is divided by 2.

—

No.8096-5/17

5 Page

www.DataSheet4U.com

Continued from preceding page.

Pin No.

120

121

122

123

124

125

126

127

128

129

130

131

132

133

134

135

136

137

138

139

140

141

142

143

144

145

146

147

148

149

150

151

152

153

154

155

156

157

158

159

160

161

162

163

164

165

166

167

168

169

170

171

172

173

174

175

176

177

178

179

Symbol

ODG0

ODG1

ODG2

ODG3

ODG4

ODG5

ODG6

ODG7

ODG8

ODG9

DVDD33

DVSS33

SDCLKI

ODB0

ODB1

ODB2

ODB3

ODB4

ODB5

ODB6

ODB7

ODB8

ODB9

DVDD33

DVSS33

DVDD18

DVSS18

SAD0

SAD1

SAD2

SAD3

SAD4

SAD5

SAD6

SAD7

SAD8

DVDD33

DVSS33

SAD9

SAD10

SDQ0

SDQ1

SDQ2

SDQ3

SDQ4

SDQ5

DVDD33

DVSS33

DVDD18

DVSS18

SDQ6

SDQ7

SDQ8

SDQ9

SDQ10

SDQ11

SDQ12

SDQ13

DVDD33

DVSS33

I/O circuit type

I/O Circuit type

O

O

O

O

O

PHOT08

O

O

O

O

O

P—

P—

I PHIC

O

O

O

O

O

PHOT08

O

O

O

O

O

P—

P—

P—

P—

O

O

O

O

O PHOT12

O

O

O

O

P—

P—

O

PHOT12

O

B

B

B

PHBT12

B

B

B

P—

P—

P—

P—

B

B

B

B

PHBT12

B

B

B

B

P—

P—

LC749450NW

Connected to

Notes

G signal outputs

Power supply

GND

3.3 V system power supply

3.3 V system ground

SDRAM system clock

B signal outputs

Power supply

GND

Power supply

GND

3.3 V system power supply

3.3 V system ground

1.8 V system power supply

1.8 V system ground

SDRAM address outputs

Power supply

GND

3.3 V system power supply

3.3 V system ground

SDRAM address outputs

SDRAM data I/O

Power supply

GND

Power supply

GND

3.3 V system power supply

3.3 V system ground

1.8 V system power supply

1.8 V system ground

SDRAM clock output

Power supply

GND

3.3 V system power supply

3.3 V system ground

Continued on next page.

No.8096-11/17

11 Page | ||

| Páginas | Total 17 Páginas | |

| PDF Descargar | [ Datasheet LC749450NW.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LC749450NW | Silicon Gate CMOS IC Digital RGB Image Processor IC | Sanyo Semicon Device |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |