|

|

PDF GS8662D09E-xxx Data sheet ( Hoja de datos )

| Número de pieza | GS8662D09E-xxx | |

| Descripción | 72Mb SigmaQuad-II Burst of 4 SRAM | |

| Fabricantes | GSI Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de GS8662D09E-xxx (archivo pdf) en la parte inferior de esta página. Total 29 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Preliminary

GS8662D08/09/18/36E-333/300/250/200/167

165-Bump BGA

Commercial Temp

Industrial Temp

72Mb SigmaQuad-II

Burst of 4 SRAM

333 MHz–167 MHz

1.8 V VDD

1.8 V and 1.5 V I/O

Features

• Simultaneous Read and Write SigmaQuad™ Interface

• JEDEC-standard pinout and package

• Dual Double Data Rate interface

• Byte Write controls sampled at data-in time

• Burst of 4 Read and Write

• 1.8 V +100/–100 mV core power supply

• 1.5 V or 1.8 V HSTL Interface

• Pipelined read operation

• Fully coherent read and write pipelines

• ZQ pin for programmable output drive strength

• IEEE 1149.1 JTAG-compliant Boundary Scan

• Pin-compatible with present 9Mb, 18Mb, and 36Mb and

future 144Mb devices

• 165-bump, 15 mm x 17 mm, 1 mm bump pitch BGA package

• RoHS-compliant 165-bump BGA package available

SigmaQuad™ Family Overview

The GS8662D08/09/18/36E are built in compliance with the

SigmaQuad-II SRAM pinout standard for Separate I/O

synchronous SRAMs. They are 75,497,472-bit (72Mb)

SRAMs. The GS8662D08/18/36E SigmaQuad SRAMs are

just one element in a family of low power, low voltage HSTL

I/O SRAMs designed to operate at the speeds needed to

implement economical high performance networking systems.

Clocking and Addressing Schemes

The GS8662D08/09/18/36E SigmaQuad-II SRAMs are

synchronous devices. They employ two input register clock

inputs, K and K. K and K are independent single-ended clock

inputs, not differential inputs to a single differential clock input

buffer. The device also allows the user to manipulate the

output register clock inputs quasi independently with the C and

Bottom View

165-Bump, 15 mm x 17 mm BGA

1 mm Bump Pitch, 11 x 15 Bump Array

C clock inputs. C and C are also independent single-ended

clock inputs, not differential inputs. If the C clocks are tied

high, the K clocks are routed internally to fire the output

registers instead.

Because Separate I/O SigmaQuad-II B4 RAMs always transfer

data in four packets, A0 and A1 are internally set to 0 for the

first read or write transfer, and automatically incremented by 1

for the next transfers. Because the LSBs are tied off internally,

the address field of a SigmaQuad-II B4 RAM is always two

address pins less than the advertised index depth (e.g., the 4M

x 18 has a 1024K addressable index).

Parameter Synopsis

tKHKH

tKHQV

- 333

3.0 ns

0.45 ns

-300

3.3 ns

0.45 ns

-250

4.0 ns

0.45 ns

-200

5.0 ns

0.45 ns

-167

6.0 ns

0.50 ns

Rev: 1.01a 2/2006

1/29

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

© 2005, GSI Technology

1 page

www.DataSheet4U.com

Preliminary

GS8662D08/09/18/36E-333/300/250/200/167

8M x 8 SigmaQuad-II SRAM—Top View

123456789

A CQ SA SA W NW1 K NC R SA

B NC NC NC SA NC K NW0 SA NC

C NC NC NC VSS SA NC SA VSS NC

D NC D4 NC VSS VSS VSS VSS VSS NC

E

NC

NC

Q4

VDDQ

VSS

VSS

VSS VDDQ NC

F

NC

NC

NC

VDDQ

VDD

VSS

VDD VDDQ NC

G

NC

D5

Q5

VDDQ

VDD

VSS

VDD VDDQ NC

H

Doff

VREF

VDDQ

VDDQ

VDD

VSS

VDD

VDDQ

VDDQ

J

NC

NC

NC

VDDQ

VDD

VSS

VDD VDDQ NC

K

NC

NC

NC

VDDQ

VDD

VSS

VDD VDDQ NC

L

NC

Q6

D6

VDDQ

VSS

VSS

VSS VDDQ

NC

M NC NC NC VSS VSS VSS VSS VSS NC

N NC D7 NC VSS SA SA SA VSS NC

P NC NC Q7 SA SA C SA SA NC

R

TDO TCK

SA

SA

SA

C

SA SA SA

11 x 15 Bump BGA—15 x 17 mm2 Body—1 mm Bump Pitch

Notes:

1. NW0 controls writes to D0:D3. NW1 controls writes to D4:D7.

2. MCL = Must Connect Low

10

SA

NC

NC

NC

D2

NC

NC

VREF

Q1

NC

NC

NC

NC

NC

TMS

11

CQ

Q3

D3

NC

Q2

NC

NC

ZQ

D1

NC

Q0

D0

NC

NC

TDI

Rev: 1.01a 2/2006

5/29

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

© 2005, GSI Technology

5 Page

www.DataSheet4U.com

R3

W3

R2

W2

R1

W1

R0

W0

A0–An

K

D1–Dn

C

Q1–Qn

CQ0

CQ1

CQ2

CQ3

Preliminary

GS8662D08/09/18/36E-333/300/250/200/167

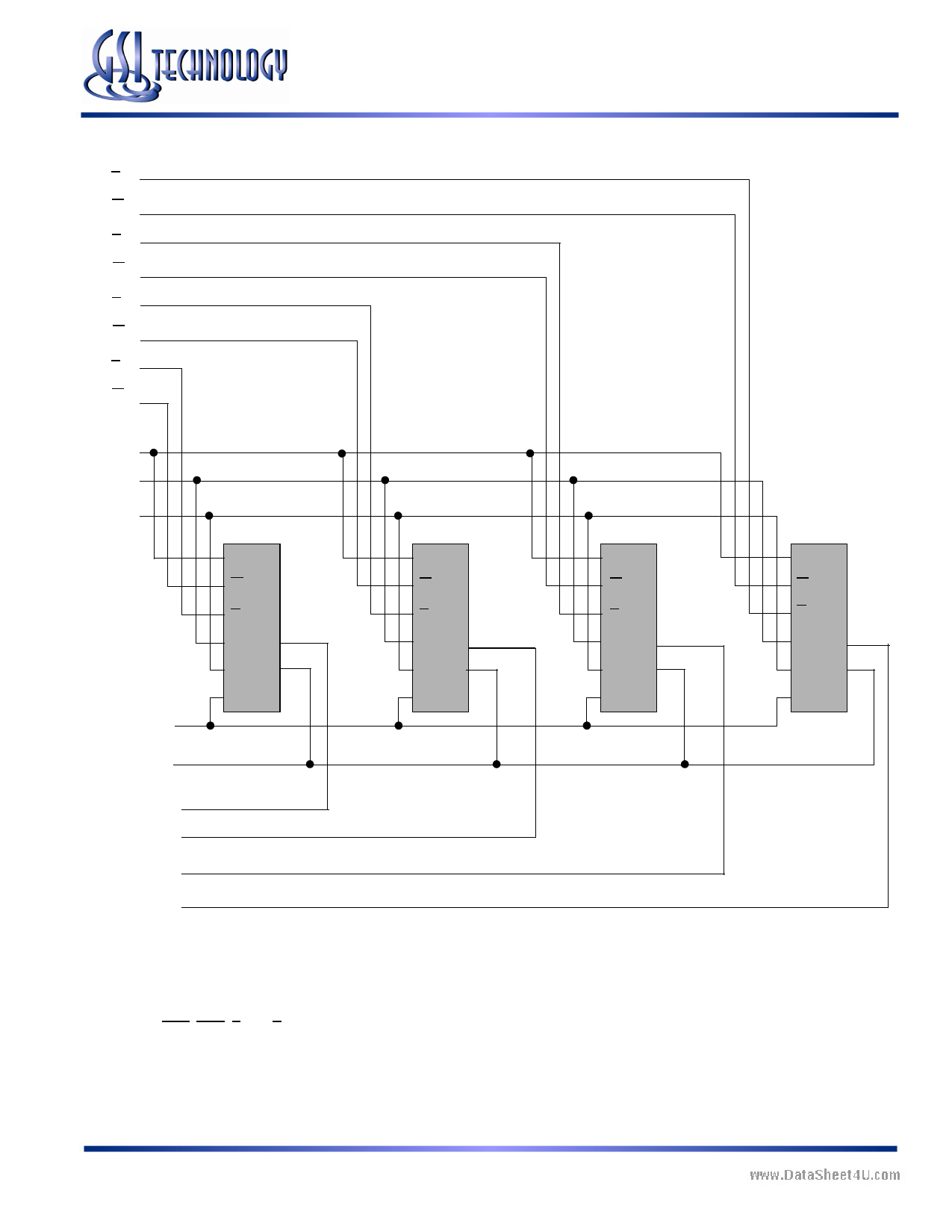

Example Four Bank Depth Expansion Schematic

Bank 0

A

W

R

K CQ

DQ

C

Bank 1

A

W

R

K CQ

DQ

C

Bank 2

A

W

R

K CQ

DQ

C

Bank 3

A

W

R

K CQ

DQ

C

Note:

For simplicity BWn, NWn, K, and C are not shown.

Rev: 1.01a 2/2006

11/29

Specifications cited are subject to change without notice. For latest documentation see http://www.gsitechnology.com.

© 2005, GSI Technology

11 Page | ||

| Páginas | Total 29 Páginas | |

| PDF Descargar | [ Datasheet GS8662D09E-xxx.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| GS8662D09E-xxx | 72Mb SigmaQuad-II Burst of 4 SRAM | GSI Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |