|

|

PDF M58LT128HSB Data sheet ( Hoja de datos )

| Número de pieza | M58LT128HSB | |

| Descripción | (M58LT128HSB / M58LT128HST) Flash memories | |

| Fabricantes | STMicroelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de M58LT128HSB (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

M58LT128HST

M58LT128HSB

128-Mbit (8 Mb ×16, Multiple Bank, Multilevel interface, Burst)

1.8 V supply, Secure Flash memories

Features

■ Supply voltage

– VDD = 1.7 V to 2.0 V for program, erase

and read

– VDDQ = 2.7 V to 3.6 V for I/O buffers

– VPP = 9 V for fast program

■ Synchronous / Asynchronous Read

– Synchronous Burst Read mode: 52 MHz

– Asynchronous Page Read mode

– Random Access: 85 ns

■ Synchronous Burst Read Suspend

■ Programming time

– 2.5 µs typical Word program time using

Buffer Enhanced Factory Program

command

■ Memory organization

– Multiple Bank memory array: 8-Mbit Banks

– Parameter Blocks (top or bottom location)

■ Dual operations

– program/erase in one Bank while read in

others

– No delay between read and write

operations

■ Block protection

– All blocks protected at power-up

– Any combination of blocks can be protected

with zero latency

– Absolute Write Protection with VPP = VSS

■ Security

– Software security features

– 64-bit unique device number

– 2112-bit user programmable OTP Cells

■ Common Flash Interface (CFI)

■ 100 000 program/erase cycles per block

BGA

TBGA64 (ZA)

10 × 13 mm

■ Electronic signature

– Manufacturer code: 20h

– Top device codes:

M58LT128HST: 88D6h

– Bottom device codes

M58LT128HSB: 88D7h

■ TBGA64 package

– ECOPACK® compliant

March 2007

Rev 1

1/110

www.st.com

1

1 page

www.DataSheet4U.com

M58LT128HST, M58LT128HSB

List of tables

List of tables

Table 1.

Table 2.

Table 3.

Table 4.

Table 5.

Table 6.

Table 7.

Table 8.

Table 9.

Table 10.

Table 11.

Table 12.

Table 13.

Table 14.

Table 15.

Table 16.

Table 17.

Table 18.

Table 19.

Table 20.

Table 21.

Table 22.

Table 23.

Table 24.

Table 25.

Table 26.

Table 27.

Table 28.

Table 29.

Table 30.

Table 31.

Table 32.

Table 33.

Table 34.

Table 35.

Table 36.

Table 37.

Table 38.

Table 39.

Table 40.

Table 41.

Table 42.

Table 43.

Table 44.

Table 45.

Signal names . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Bank architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11

Bus operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16

Command codes. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Standard commands. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Factory commands . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Electronic signature codes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Protection Register locks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Status Register bits. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 36

X-Latency Settings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 37

Configuration Register . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 40

Burst type definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 41

Dual operations allowed in other banks . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 47

Dual operations allowed in same bank . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Dual operation limitations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 48

Program/Erase times and endurance cycles . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 51

Absolute maximum ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 53

Operating and ac measurement conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 54

Capacitance . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 55

DC characteristics - currents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 56

DC characteristics - voltages . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 57

Asynchronous Read ac characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 60

Synchronous Read ac characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 64

Write ac characteristics, Write Enable controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 66

Write ac Characteristics, Chip Enable Controlled . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 68

Reset and Power-up ac characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 69

TBGA64 10 × 13 mm - 8 × 8 active ball array, 1 mm pitch, package

mechanical data . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 71

Ordering information scheme . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 72

Top boot block addresses, M58LT128HST . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 73

Bottom boot block addresses, M58LT128HSB . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 77

Query structure overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 81

CFI query identification string . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 82

CFI query system interface information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 83

Device geometry definition . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 84

Primary algorithm-specific extended query table . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 85

Protection Register information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Burst Read information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 86

Bank and Erase Block region information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Bank and Erase Block region 1 information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 87

Bank and Erase Block Region 2 Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 89

Command Interface states - modify table, next state . . . . . . . . . . . . . . . . . . . . . . . . . . . . 100

Command Interface states - modify table, next output state . . . . . . . . . . . . . . . . . . . . . . 103

Command interface states - lock table, next state . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 105

Command interface states - lock table, next output state . . . . . . . . . . . . . . . . . . . . . . . . 107

Document revision history . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 109

5/110

5 Page

www.DataSheet4U.com

M58LT128HST, M58LT128HSB

Table 2. Bank architecture

Number

Bank Size

Parameter Bank

Bank 1

Bank 2

Bank 3

8 Mbits

8 Mbits

8 Mbits

8 Mbits

Description

Parameter Blocks

4 blocks of 16 Kwords

-

-

-

Main Blocks

7 blocks of 64 Kwords

8 blocks of 64 Kwords

8 blocks of 64 Kwords

8 blocks of 64 Kwords

Bank 14

Bank 15

8 Mbits

8 Mbits

- 8 blocks of 64 Kwords

- 8 blocks of 64 Kwords

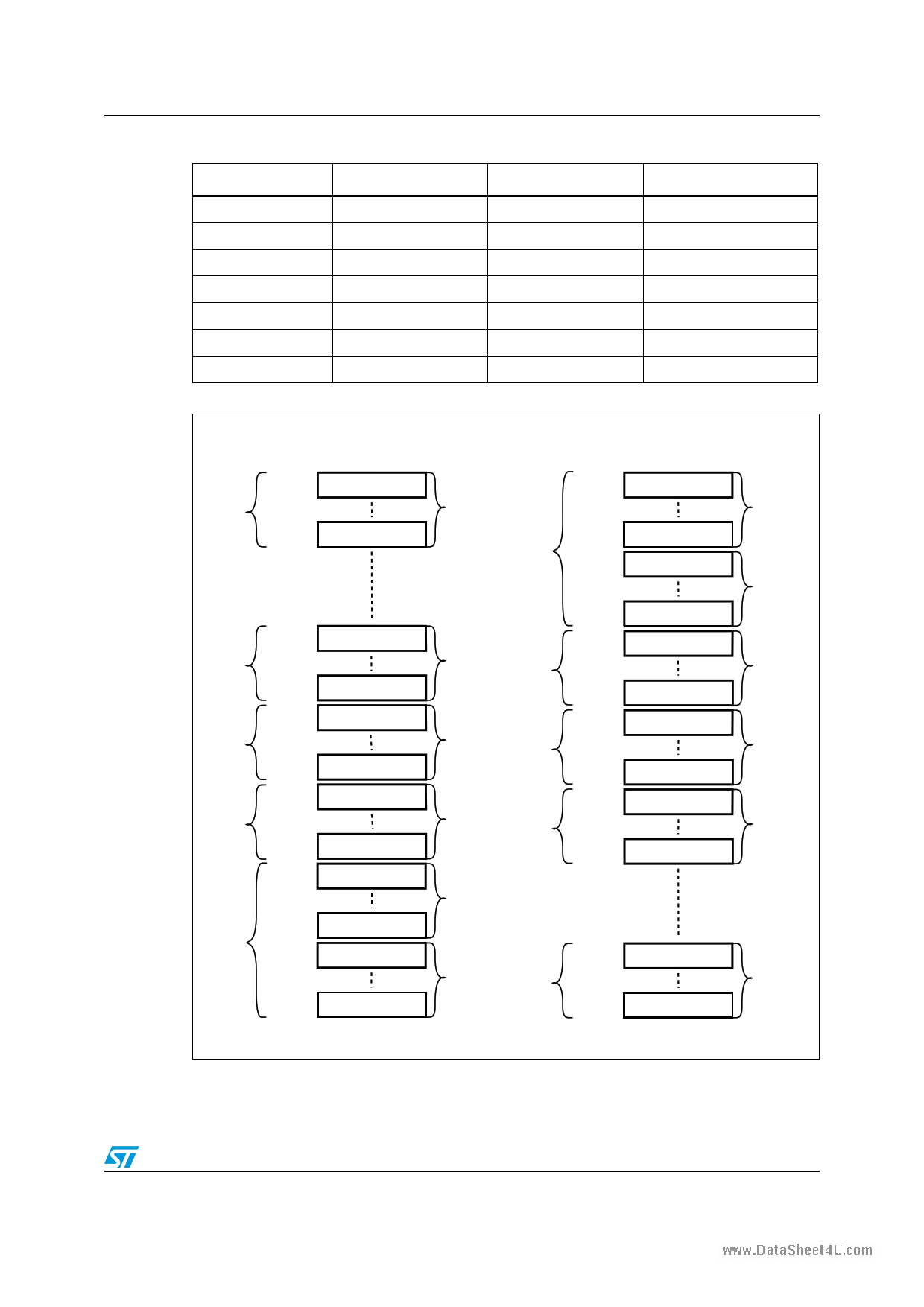

Figure 3. Memory map

M58LT128HST - Top Boot Block

Address lines A0-A16

M58LT128HSB - Bottom Boot Block

Address lines A0-A16

Bank 15

000000h

00FFFFh

070000h

07FFFFh

64 KWord

64 KWord

Bank 3

Bank 2

Bank 1

600000h

60FFFFh

670000h

67FFFFh

680000h

68FFFFh

6F0000h

6FFFFFh

700000h

70FFFFh

770000h

77FFFFh

780000h

78FFFFh

Parameter

Bank

7E0000h

7EFFFFh

7F0000h

7F3FFFh

7FC000h

7FFFFFh

64 KWord

64 KWord

64 KWord

64 KWord

64 KWord

64 KWord

64 KWord

64 KWord

16 KWord

16 KWord

8 Main

Blocks

Parameter

Bank

000000h

003FFFh

00C000h

00FFFFh

010000h

01FFFFh

8 Main

Blocks

8 Main

Blocks

8 Main

Blocks

7 Main

Blocks

Bank 1

Bank 2

Bank 3

070000h

07FFFFh

080000h

08FFFFh

0F0000h

0FFFFFh

100000h

10FFFFh

170000h

17FFFFh

180000h

18FFFFh

1F0000h

1FFFFFh

16 KWord

16 KWord

64 KWord

64 KWord

64 KWord

64 KWord

64 KWord

64 KWord

64 KWord

64 KWord

4 Parameter

Blocks Bank 15

780000h

78FFFFh

7F0000h

7FFFFFh

64 KWord

64 KWord

4 Parameter

Blocks

7 Main

Blocks

8 Main

Blocks

8 Main

Blocks

8 Main

Blocks

8 Main

Blocks

AI12888

11/110

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet M58LT128HSB.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M58LT128HSB | (M58LT128HSB / M58LT128HST) Flash memories | STMicroelectronics |

| M58LT128HST | (M58LT128HSB / M58LT128HST) Flash memories | STMicroelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |