|

|

PDF IDTCV125 Data sheet ( Hoja de datos )

| Número de pieza | IDTCV125 | |

| Descripción | PROGRAMMABLE FLEXPC CLOCK | |

| Fabricantes | IDT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDTCV125 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

IDTCV125

PROGRAMMABLEFLEXPCCLOCKFORP4PROCESSOR

COMMERCIALTEMPERATURERANGE

PROGRAMMABLE FLEXPC

CLOCK FOR P4 PROCESSOR

IDTCV125

FEATURES:

• Power management control suitable for notebook applications

• One high precision PLL for CPU, SSC and N programming

• One high precision PLL for SRC/PCI, supports 100MHz output

frequency, SSC and N programming

• One high precision PLL for LVDS. Supports 100/96MHz output

frequency, SSC programming

• One high precision PLL for 96MHz/48MHz

• Band-gap circuit for differential outputs

• Support spread spectrum modulation, –0.5 down spread and

others

• Support SMBus block read/write, index read/write

• Selectable output strength for REF

• Allows for CPU frequency to change to a slower frequency to

conserve power when an application is less execution-

intensive

• Smooth transition for N programming

• Available in TSSOP package

KEY SPECIFICATION:

• CPU/SRC CLK cycle to cycle jitter < 85ps

• PCI CLK cycle to cycle jitter < 250ps

• Static PLL frequency divide error < 114 ppm

• Static PLL frequency divide error for 48MHz < 5 ppm

DESCRIPTION:

IDTCV125 is a 56 pin clock device, incorporating both Intel CK410M and

CKSSCD requirements, for Intel advance P4 processors. The CPU output

bufferisdesignedtosupportupto400MHzprocessor. ThischiphasfourPLLs

inside for CPU, SRC/PCI, LVDS, and 48MHz/DOT96 IO clocks. This device

also implements Band-gap referenced IREF to reduce the impact of VDD variation

on differential outputs, which can provide more robust system performance.

Static PLL frequency divide error can be as low as 36 ppm, worse case 114

ppm,providinghighaccuracyoutputclock. EachCPU/SRC/LVDShasitsown

Spread Spectrum selection.

OUTPUTS:

• 2*0.7V current –mode differential CPU CLK pair

• 6*0.7V current –mode differential SRC CLK pair

• One CPU_ITP/SRC selectable CLK pair

• 6*PCI, 2 free running, 33.3MHz

• 1*96MHz, 1*48MHz

• 1*REF

• One 100/96 MHz differential LVDS

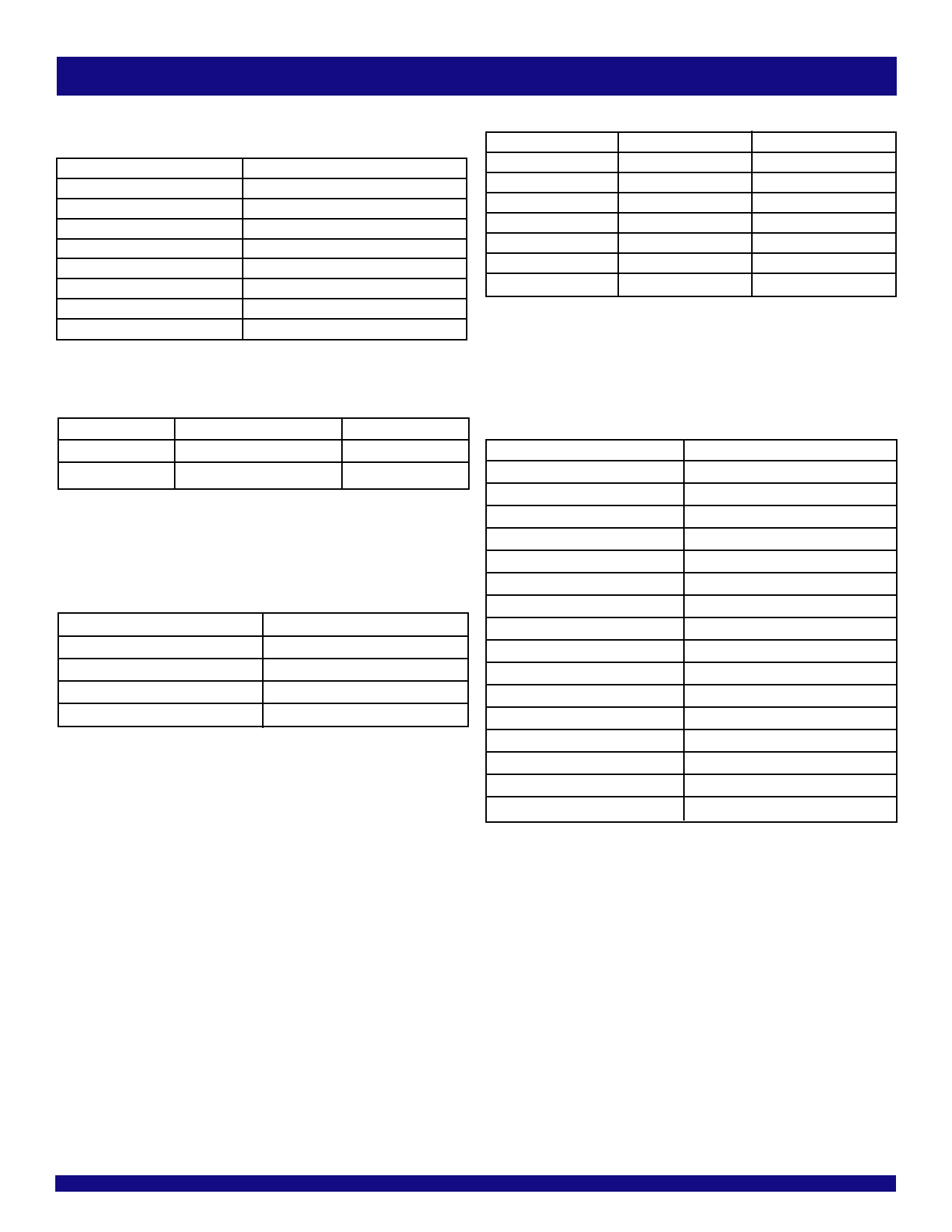

FUNCTIONAL BLOCK DIAGRAM

X1

X2

SDATA

SCLK

XTAL

Osc Amp

SM Bus

Controller

VTT_PWRGD#/PD

SEL100/96#

FSA.B.C

PCI_STOP#

CPU_STOP#

SEL

100/96MHz

Control

Logic

PLL1

SSC

N Programmable

PLL2

SSC

PLL3

SSC

N Programmable

CPU CLK

Output Buffer

Stop Logic

IREF

LVDS CLK

Output Buffer

Stop Logic

IREF

ITP_EN

SRC CLK

Output Buffer

Stop Logic

IREF

PLL4

48MHz/96MHz

Output BUffer

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

COMMERCIAL TEMPERATURE RANGE

© 2004 Integrated Device Technology, Inc.

1

CPU[1:0]

CPU_ITP/SRC7

REF

LVDS

SRC[6:1]

PCI[3:0], PCIF[1:0]

48MHz

DOT96

DECEMBER 2004

DSC 6552/14

1 page

IDTCV125

PROGRAMMABLEFLEXPCCLOCKFORP4PROCESSOR

SSC MAGNITUDE CONTROL FOR CPU,

SRC, AND SMC

SMC[2:0]

000 -0.25

001 -0.5

010 -0.75

011 -1

100 ±0.125

101 ±0.25

110 ±0.375

111 ±0.5

RESOLUTION

CPU (MHz)

100

133

166

200

266

333

400

COMMERCIALTEMPERATURERANGE

Resolution

0.666667

0.666667

1.333333

1.333333

1.333333

2.666667

2.666667

N=

150

200

125

150

200

125

150

SEL 100/96# CONFIGURATION

SEL 100/96#

LVDS Frequency

Unit

0 96 MHz

1 100 MHz

S.E. CLOCK STRENGTH SELECTION

(PCI, REF, USB48)

Str[1:0]

Level

00 1

01 0.8

10 0.6

11 1.2

SPREAD SPECTRUM CONTROL

SELECTION (SSC) FOR LVDS

S[3:0]

0000

0001

0010

0011

0100

0101

0110

0111

1000

1001

1010

1011

1100

1101

1110

1111

Spread

-0.8%

-1%

-1.25%

-1.5%

-1.75%

-2%

-0.3%

-0.5%

±0.3%

±0.4%

±0.5%

±0.6%

±0.8%

±1%

±1.25%

±1.5%

5

5 Page

IDTCV125

PROGRAMMABLEFLEXPCCLOCKFORP4PROCESSOR

COMMERCIALTEMPERATURERANGE

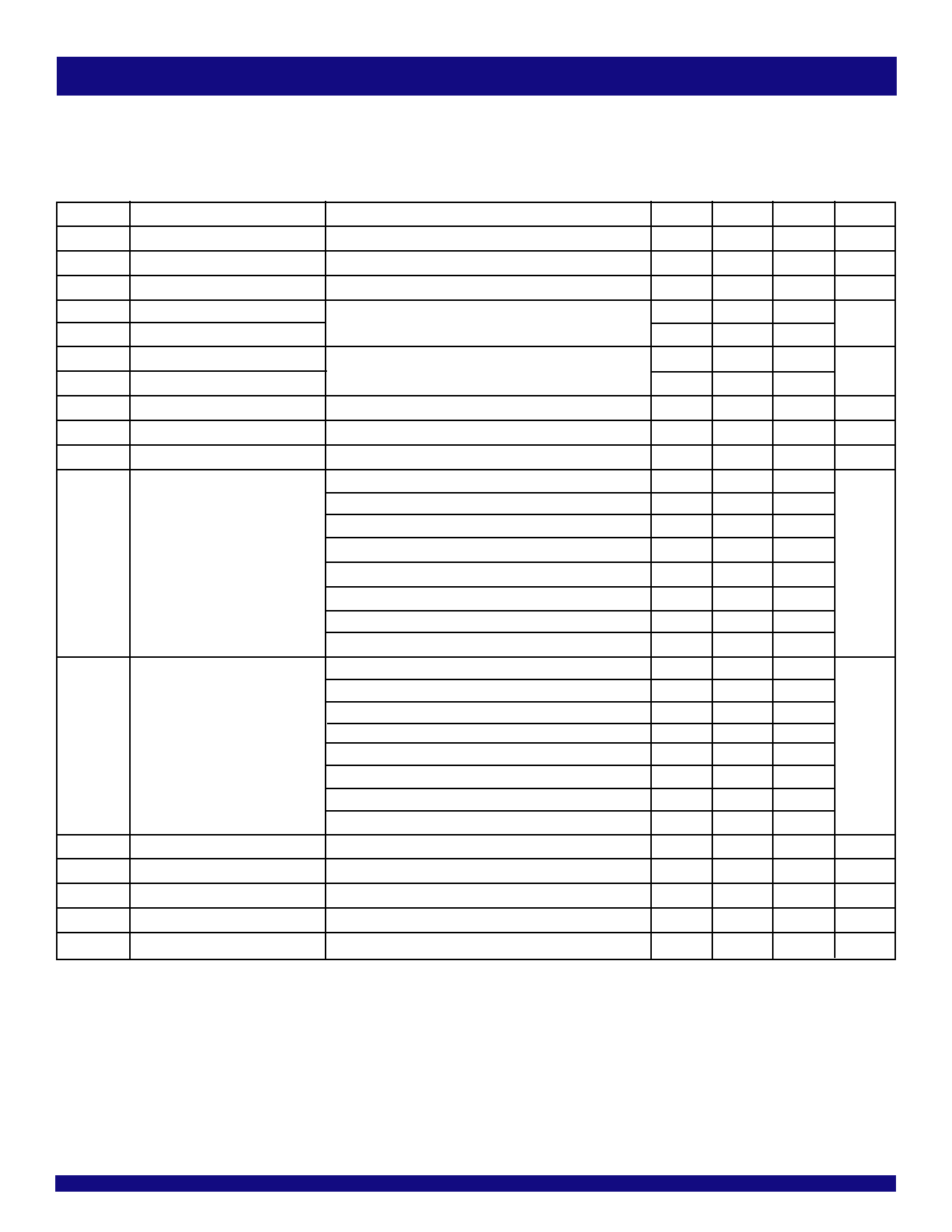

ELECTRICAL CHARACTERISTICS - CPU, SRC, AND DOT96 0.7 CURRENT MODE

DIFFERENTIAL PAIR(1)

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA = 0°C to +70°C, Supply Voltage: VDD = 3.3V ± 5%; CL = 2pF

Symbol

ZO

VOH3

VOL3

VHIGH

VLOW

VOVS

VUDS

VCROSS(ABS)

d - VCROSS

ppm

TPERIOD

Parameter

Test Conditions

Current Source Output Impedance(2) VO = VX

Output HIGH Voltage

IOH = -1mA

Output LOW Voltage

IOL = 1mA

Voltage HIGH(2)

Voltage LOW(2)

Max Voltage(2)

Statistical measurement on single-ended signal using

oscilloscope math function

Measurement on single-ended signal using absolute value

Min Voltage(2)

Crossing Voltage (abs)(2)

Crossing Voltage (var)(2)

Variation of crossing over all edges

Long Accuracy(2,3)

See TPERIOD Min. - Max. values

400MHz nominal / -0.5% spread

333.33MHz nominal / -0.5% spread

266.66MHz nominal / -0.5% spread

Average Period(3)

200MHz nominal / -0.5% spread

Min.

3000

2.4

—

660

–300

—

–300

250

—

–300

2.4993

2.9991

3.7489

4.9985

Typ.

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Max.

—

—

0.4

1150

150

1150

—

550

140

300

2.5133

3.016

3.77

5.0266

Unit

Ω

V

V

mV

mV

mV

mV

ppm

ns

166.66MHz nominal / -0.5% spread

133.33MHz nominal / -0.5% spread

100MHz nominal / -0.5% spread

5.9982

—

6.032

7.4978

—

7.54

9.997 — 10.0533

TABSMIN Absolute Min Period(2,3)

tR Rise Time(2)

tF Fall Time(2)

d-tR Rise Time Variation(2)

d-tF Fall Time Variation(2)

dT3 Duty Cycle(2)

96MHz nominal

400MHz nominal / -0.5% spread

333.33MHz nominal / -0.5% spread

266.66MHz nominal / -0.5% spread

200MHz nominal / -0.5% spread

166.66MHz nominal / -0.5% spread

133.33MHz nominal / -0.5% spread

100MHz nominal / -0.5% spread

96MHz nominal

VOL = 0.175V, VOH = 0.525V

VOL = 0.175V, VOH = 0.525V

Measurement from differential waveform

10.4135

2.4143

2.9141

3.6639

4.9135

5.9132

7.4128

9.912

10.1635

175

175

—

—

45

—

—

—

—

—

—

—

—

—

—

—

—

—

—

10.4198

—

—

—

—

—

—

—

—

700

700

125

125

55

ns

ps

ps

ps

ps

%

NOTES:

1. SRC clock outputs run only at 100MHz.

2. This parameter is guaranteed by design, but not 100% production tested.

3. All long term accuracy and clock period specifications are guaranteed with the assumption that the REF output is at 14.31818MHz.

11

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet IDTCV125.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDTCV122C | CLOCK | Integrated Device Technology |

| IDTCV123 | PROGRAMMABLE FLEXPC CLOCK | IDT |

| IDTCV125 | PROGRAMMABLE FLEXPC CLOCK | IDT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |