|

|

PDF IDT74SSTU32D869 Data sheet ( Hoja de datos )

| Número de pieza | IDT74SSTU32D869 | |

| Descripción | 14-BIT 1:2 REGISTERED BUFFER | |

| Fabricantes | IDT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDT74SSTU32D869 (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

IDT74SSTU32D869

14-BIT 1:2 REGISTERED BUFFER WITH PARITY

14-BIT 1:2 REGISTERED

BUFFER WITH PARITY

COMMERCIAL TEMPERATURE RANGE

IDT74SSTU32D869

FEATURES:

• 1.8V Operation

• Designed to drive low impedance nets

• SSTL_18 style clock and data inputs

• Differential CLK input

• Control inputs compatible with LVCMOS levels

• Center input architecture for optimum PCB design

• Latch-up performance exceeds 100mA

• ESD >2000V per MIL-STD-883, Method 3015; >200V using

machine model (C = 200pF, R = 0)

• Available in 150-pin CTBGA package

APPLICATIONS:

• Along with CSPU877/A/D DDR2 PLL, provides complete solution

for DDR2 DIMMs

• Optimized for DDR2-400/533 [PC2-3200/4300] Raw card L

DESCRIPTION:

The SSTU32D869 is a 14-bit 1:2 configurable registered buffer designed

for 1.7V to 1.9V VDD operation. All clock and data inputs are compatible with

the JEDEC standard for SSTL_18. The control inputs are LVCMOS. All

outputs are 1.8V CMOS drivers that have been optimized to drive the DDR2

DIMM load.

The SSTU32D869 operates from a differential clock (CLK and CLK).

Data are registered at the crossing of CLK going high and CLK going low.

The SSTU32D869 includes a parity checking function. The SSTU32D869

accepts parity bits from the memory controller at its input pins PARIN[1:2],

compares it with the data received on the D-inputs, and indicates whether

a parity error has occured on its open-drain PTYERR[1:2] pins (active low).

When used as a single device, the C1 inputs are tied low. In this

configuration, the partial-parity-out (PPO[1:2]) and PTYERR[1:2] signals

are produced two clock cycles after the corresponding data output. When

used in pairs, the C1 inputs of the first register are tied low and the C1 inputs

of the second register are tied high. The PTYERR[1:2] outputs of the first

SSTU32D869 is left floating and the valid error information is latched on the

PTYERR[1:2] outputs of the second SSTU32D869 .

This device supports low-power standby operation. When the reset input

(RESET) is low, the differential input receivers are disabled, and undriven

(floating) data, clock, and reference voltage (VREF) inputs are allowed. In

addition, when RESET is low all registers are reset, and all outputs are

forced low. The LVCMOS RESET and Cx inputs must always be held at

a valid logic high or low level.

To ensure defined outputs from the register before a stable clock has been

supplied, RESET must be held in the low state during power up.

In the DDR2 DIMM application, RESET is specified to be completely

asynchronous with respect to CLK and CLK. Therefore, no timing

relationship can be guaranteed between the two. When entering reset, the

register will be cleared and the outputs will be driven low quickly, relative

to the time to disable the differential input receivers. However, when coming

out of a reset, the register will become active quickly, relative to the time to

enable the differential input receivers. As long as the data inputs are low,

and the clock is stable during the time from the low-to-high transition of

RESET until the input receivers are fully enabled, the design of the

SSTU32D869 must ensure that the outputs will remain low, thus ensuring

no glitches on the outputs.

The device monitors the DCS input and will gate the Qn outputs from

changing states when DCS is high. If the DCS input is low, the Qn outputs

will function normally. The RESET input has priority over the DCS control

and will force the Qn outputs low and the PTYERR[1:2] outputs high. The

EF[0:3] inputs control the driver strength and slew rate for both the A and

B outputs independently.

This device also supports low-power active operation by monitoring both

system chip select (DCS and CSR) inputs and will fate the Qn and PPO

outputs from changing states when both DCS and CSR inputs are high. If

either DCS and CSR input is low, the Qn and PPO outputs will function

normally. Also, if the DCS and CSR are high, the device will gate the

PTYERR[1:2] outputs from changing states. If the DCS and CSR are low,

the PTYERR[1:2] will function normally. The RESET input has priority over

the DCS and CSR control. When driven low, they will force the Qn and

PPO outputs low and the PTYERR[1:2] outputs high. If the DCS control

functionality is not desired, then the CSR input can be hard-wired to ground,

in which case the setup-time requirement for the DCS would be the same

as for the other D data inputs. To control the low-power mode with DCS

only, then the CSR input should be pulled up to VDD through a pullup resistor.

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

COMMERCIAL TEMPERATURE RANGE

c 2005 Integrated Device Technology, Inc.

1

JANUARY 2005

DSC 6746/7

1 page

IDT74SSTU32D869

14-BIT 1:2 REGISTERED BUFFER WITH PARITY

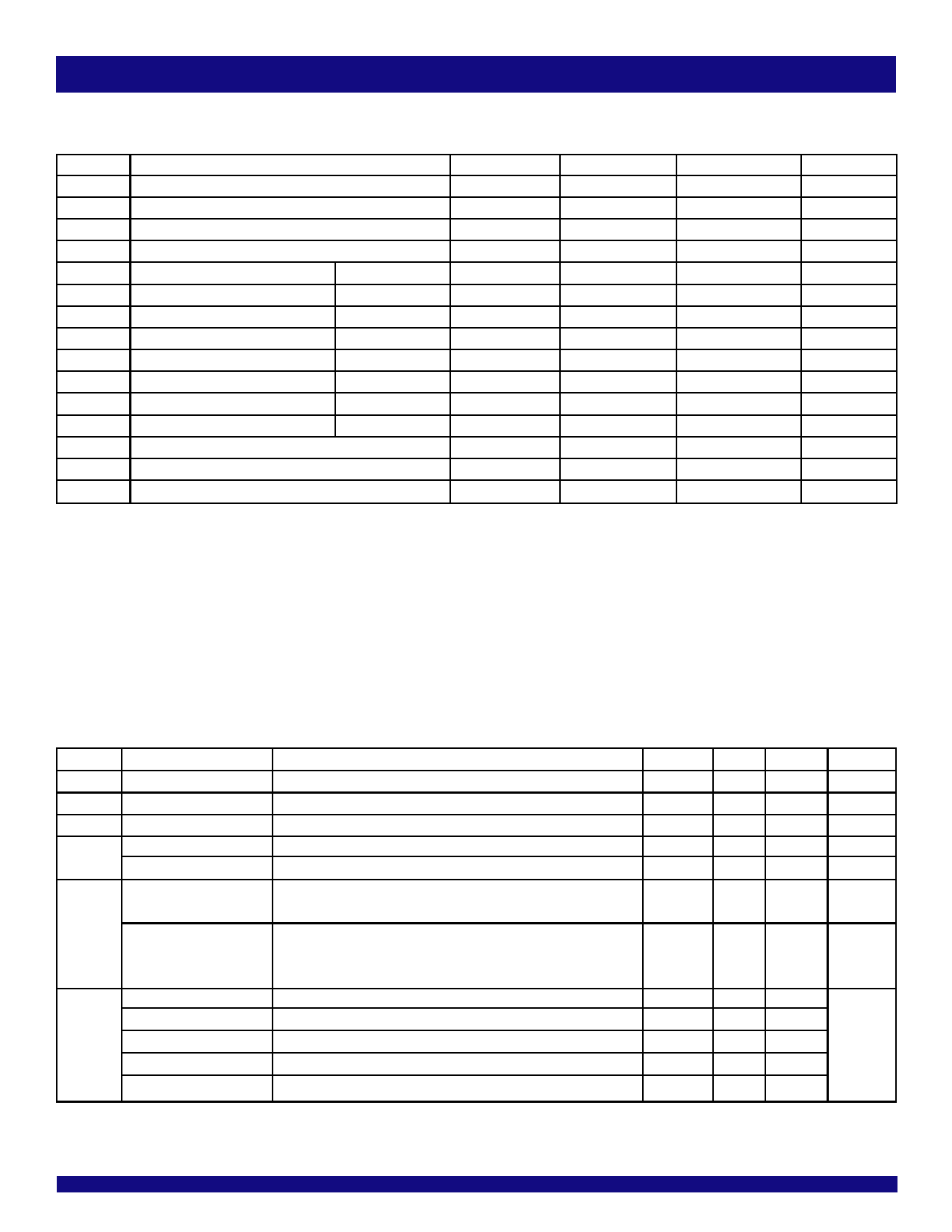

FUNCTION TABLE (EACH FLIP-FLOP) (1)

Inputs

RESET

DCS

CSR

CLK

CLK

HLL ↑ ↓

HLL ↑ ↓

H

L

L

L or H

L or H

H LH ↑ ↓

H LH ↑ ↓

H

L

H

L or H

L or H

HH L ↑ ↓

HH L ↑ ↓

H

H

L

L or H

L or H

HHH ↑ ↓

HHH ↑ ↓

H

H

H

L or H

L or H

L XorFloating XorFloating XorFloating XorFloating

NOTES:

1. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don’t Care

↑ = LOW to HIGH

↓ = HIGH to LOW

2. Output level before the indicated steady-state conditions were established.

Dx, DODT, DCKE

L

H

X

L

H

X

L

H

X

L

H

X

X or Floating

COMMERCIAL TEMPERATURE RANGE

Qx

Outputs

L

H

Q0(2)

L

H

Q0(2)

L

H

Q0(2)

Q0(2)

Q0(2)

Q0(2)

L

QCSx

Output

L

L

Q0(2)

L

L

Q0(2)

H

H

Q0(2)

H

H

Q0(2)

L

QODTx, QCKEx

Outputs

L

H

Q0(2)

L

H

Q0(2)

L

H

Q0(2)

L

H

Q0(2)

L

PARITY AND STANDBY FUNCTION TABLE(1)

Inputs

Outputs

RESET

H

H

H

H

H

H

H

H

H

H

L

DCS

L

L

L

L

X

X

X

X

H

X

X or Floating

CSR

X

X

X

X

L

L

L

L

H

X

X or Floating

CLK

↑

↑

↑

↑

↑

↑

↑

↑

↑

L or H

X or Floating

CLK

↓

↓

↓

↓

↓

↓

↓

↓

↓

L or H

X or Floating

Σ of Inputs = H (D1 - D14)(2)

Even

Odd

Even

Odd

Even

Odd

Even

Odd

X

X

X or Floating

PAR_IN(3)

L

L

H

H

L

L

H

H

X

X

X or Floating

PPO(3,4)

L

H

H

L

L

H

H

L

PPO0

PPO0

L

PTYERR(3,5)

H

L

L

H

H

L

L

H

PTYERR0

PTYERR0

H

NOTES:

1. H = HIGH Voltage Level

L = LOW Voltage Level

X = Don’t Care

↑ = LOW to HIGH

↓ = HIGH to LOW

2. This range does not include D1, D4, and D7.

3. PARIN1 is used to generate PPO1 and PTYERR1. PARIN2 is used to generate PPO2 and PTYERR2.

4. PAR_IN arrives one clock cycle (C1 = 0), or two clock cycles (C1 = 1), after the data to which it applies.

5. This transition assumes PTYERR[1:2] is HIGH at the crossing of CLK going HIGH and CLK going LOW. If PTYERR[1:2] is LOW, it stays latched LOW for two clock cycles

or until RESET is driven LOW.

5

5 Page

IDT74SSTU32D869

14-BIT 1:2 REGISTERED BUFFER WITH PARITY

COMMERCIAL TEMPERATURE RANGE

OPERATING CHARACTERISTICS, TA = 25ºC (1,2)

Symbol

Parameter

Min.

Typ.

VDD Supply Voltage

VREF ReferenceVoltage

VTT TerminationVoltage

VI InputVoltage

VIH AC High-Level Input Voltage

Data Inputs

VIL AC Low-Level Input Voltage

Data Inputs

VIH DC High-Level Input Voltage

Data Inputs

VIL DC Low-Level Input Voltage

Data Inputs

VIH High-Level Input Voltage

RESET, Cx

VIL Low-Level Input Voltage

RESET, Cx

VICR Common Mode Input Voltage

CLK, CLK

VID DifferentialInputVoltage

CLK, CLK

IOH High-Level Output Current

IOL Low-Level Output Current

TA OperatingFree-AirTemperature

1.7

0.49 * VDD

VREF– 40mV

0

VREF+ 250mV

—

VREF+ 125mV

—

0.65 * VDD

—

0.675

600

—

—

0

—

0.5 * VDD

VREF

—

—

—

—

—

—

—

—

—

—

—

—

NOTES:

1. The RESET and Cx inputs of the device must be held at valid levels (not floating) to ensure proper device operation.

2. The differential inputs must not be floating unless RESET is LOW.

Max.

1.9

0.51 * VDD

VREF+ 40mV

VDD

—

VREF– 250mV

—

VREF– 125mV

—

0.35 * VDD

1.125

—

-8

+8

70

Unit

V

V

V

V

V

V

V

V

V

V

V

mV

mA

mA

°C

DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

Operating Condition: TA = 0°C to +70°C, VDD = 1.8V ±0.1V

Symbol

VOH

VOL

II

IDD

IDDD

Parameter

All Inputs

Static Standby

Static Operating

Dynamic Operating

(Clock Only)

Dynamic Operating

(Per Each Data Input)

Data Inputs

DCSn / CSR

CI CLK and CLK

RESET

Parity Inputs

Test Conditions

VDD = 1.7V to 1.9V, IOH = – 6 mA

VDD = 1.7V to 1.9V, IOL = +6 mA

VI = VDD or GND

IO = 0, VDD = 1.9V, RESET = GND

IO = 0, VDD = 1.9V, RESET = VDD, VI = VIH (AC) or VIL (AC)

IO = 0, VDD = 1.8V, RESET = VDD, VI = VIH (AC) or VIL (AC),

CLK and CLK Switching 50% Duty Cycle.

IO = 0, VDD = 1.8V, RESET = VDD, VI = VIH (AC) or VIL (AC),

1:2 Mode, CLK and CLK Switching at 50% Duty Cycle.

One Data Input Switching at Half Clock Frequency, 50% Duty Cycle.

VI = VREF ± 250mV

VI = VREF ± 250mV

VICR = 0.9V, VID = 600mV

VI = VDD or GND

VI = VREF ± 250mV

Min.

1.2

—

—

—

—

—

—

2.5

4

4

2

2

Typ.

—

—

—

—

—

—

—

—

—

—

—

—

Max.

—

0.5

±5

200

80

—

—

4

6

6

6

3

Unit

V

V

μA

μA

mA

μA/Clock

MHz

μA/Clock

MHz/Data

Input

pF

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet IDT74SSTU32D869.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDT74SSTU32D869 | 14-BIT 1:2 REGISTERED BUFFER | IDT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |