|

|

PDF IDT70P9268L Data sheet ( Hoja de datos )

| Número de pieza | IDT70P9268L | |

| Descripción | MOBILE MULTIMEDIA INTERFACE VERY LOW POWER 1.8V 16K X 16 SYNCHRONOUS DUAL-PORT STATIC RAM | |

| Fabricantes | IDT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDT70P9268L (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

MOBILE MULTIMEDIA INTERFACE (M2I)

Final

VERY LOW POWER 1.8V

Datasheet

16K X 16

IDT70P9268L

SYNCHRONOUS

DUAL-PORT STATIC RAM

Features

◆ True Dual-Ported Memory Cells

– Allows simultaneous access of the same memory location

◆ High per-port throughput performance

– Industrial: 800 Mbps

◆ Low-Power Operation

– Active: 15 mA (typ.)

– Standby: 2 uA (typ.)

◆ Multiplexed address and data I/Os

◆ Counter enable and repeat features

◆ Full synchronous operation on both ports

◆ Separate upper-byte and lower-byte controls for multiplexed bus

and bus matching compatibility

◆ LVTTL-compatible, single 1.8V (+/- 100mV) power supply

◆ Industrial temperature range (-40C to +85C)

◆ Available in a 100-ball fpBGA (fine pitch BGA)

◆ Green parts available, see ordering information

Block Diagram

A0L – A13L

I/O0L – I/O15L

ADSL

UBL

LBL

CNTEN L

CNTRPT L

CLKL

DATA0L – DATA15L

Address/Data

I/O Control

Addr0L – Addr13L

16K x 16

MEMORY

ARRAY

DATA0R – DATA15R

Address/Data

Addr0R – Addr13R

I/O Control

I/O0R – I/O15R

ADSR

UBR

LBR

CNTENR

CNTRPTR

CLKR

SFEN

CEL

OEL

R/WL

INTL

CLKL

ZZL

SPECIAL FUNCTION

LOGIC

CONTROL

LOGIC

ZZ CONTROL

LOGIC

SF0 – SF7

CER

OER

R/WR

INTR

CLKR

ZZR

NOTES:

1. This block diagram depicts operation with the address and data signals mux’d on the right port but not on the left port. If each port is set to operate with the address and data signals

mux’d, then both sides of the block diagram will be the same as the right port pictured above.

©2007 Integrated Device Technology, Inc.

1 of 23

August 22, 2007

DSC 5695/1

1 page

IDT70P9268L

Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M2I) Dual Port Static RAM

Final Datasheet

Industrial Temperature Range

Truth Table I - Read/Write and Enable Control (Multiplexed Port)

OE CLK CE UB LB R/W ADS ZZ

Upper

Byte

Lower

Byte

Cycle

Address Mode

X ↑ HXX X

X ↑ LHH X

X ↑ L LH L

X ↑ XXX L

X ↑ LHL L

X ↑ XXX L

X ↑ LLL L

X ↑ XXX L

H ↑ L LH H

L

↑

XXX

H

H ↑ LHL H

L

↑

XXX

H

H ↑ LLL H

L

↑

XXX

H

H ↑ LLL X

X X XXX X

X L High Z High Z X

X L High Z High Z X

LL

--

-- N

HL

DIN High Z N+1

LL

--

-- N

H L High Z DIN

N+1

LL

--

-- N

HL

LL

DIN

--

DIN N+1

-- N

H

L

DOUT

High Z N+2

LL

--

-- N

H

L High Z

DOUT

N+2

LL

--

-- N

H

L

DOUT

DOUT

N+2

H L High Z High Z X

X H High Z High Z X

X Deslected

X Both bytes deselected

AN W rite to Upper Byte

--

AN W rite to Lower Byte

--

AN W rite to Both Bytes

--

AN Read Upper Byte Only

--

AN Read Lower Byte Only

--

AN Read Both Bytes

--

X Outputs Disabled

X Sleep Mode – Power down

Truth Table II - Read/Write and Enable Control (Non-Multiplexed Port)

OE CLK CE UB LB R/W

X ↑ HXX X

X ↑ LHH X

X ↑ L LH L

X ↑ LHL L

X ↑ LLL L

L ↑ L LH H

L ↑ LHL H

L ↑ LLL H

H ↑ LLL X

X X XXX X

ZZ

L

L

L

L

L

L

L

L

L

H

Upper Byte I/O

High Z

High Z

DIN

High Z

DIN

DOUT

High Z

DOUT

High Z

High Z

Lower Byte I/O

High Z

High Z

High Z

DIN

DIN

High Z

DOUT

DOUT

High Z

High Z

Mode

Deselected

Both Bytes Deselected

W rite To Upper Byte Only

W rite to Lower Byte Only

W rite to Both Bytes

Read Upper Byte Only

Read Lower Byte Only

Read Both Bytes

Outputs Disabled

Sleep Mode – Power Down

Truth Table III - Address Counter Control

External

Address

An

X

Previous

Internal

Address

X

An

Internal

Address

Used

An

An + 1

CLK ADS CNTEN

↑L

↑H

X

L

CNTRPT

H

H

X

An + 1

An + 1 ↑ H

H

H

X X An ↑ X X L

Mode

External Address Used

Counter Enabled – Internal Address

Generation

External Address Blocked – Counter

Disabled (An + 1 reused)

Counter Reset to Last External Address

Loaded

Recommended Operating Temperature and Supply Voltage

G rade

In du strial

A m bien t T em p eratu re

-40°C to +85°C

GND

0V

VDD

1 .8 V + /- 10 0 m V

5 of 23

August 22, 2007

5 Page

IDT70P9268L

Very Low Power 16K x 16 Synchronous Mobile Multimedia Interface (M2I) Dual Port Static RAM

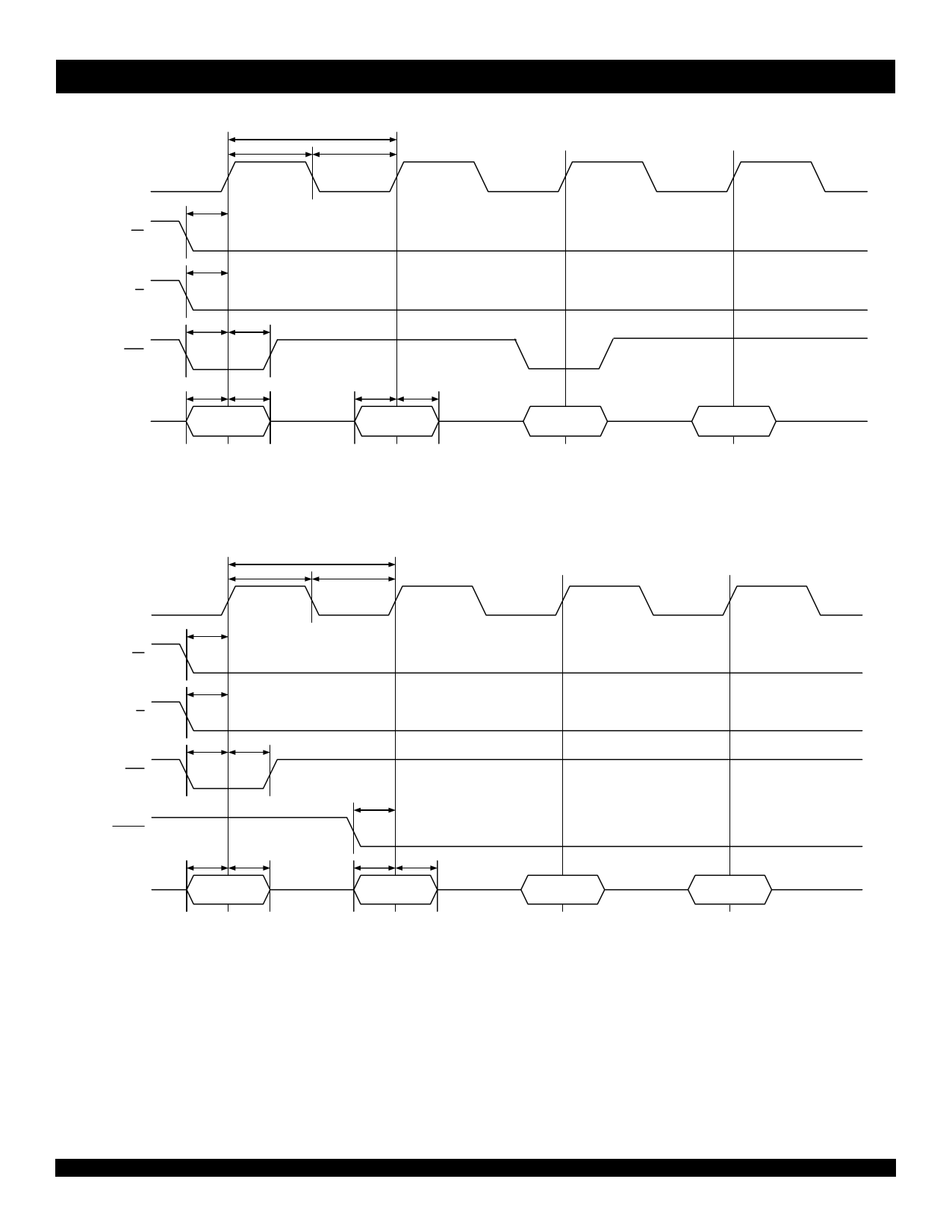

Timing Waveform for Mux’d Port Single Write Cycle

tCYC

tCH tCL

CLK

tSC

CE

tSW

R/W

tSAD

tHAD

ADS

ADDR / DATA

tSA tHA

An

tSD tHD

Dn

An+1

Final Datasheet

Industrial Temperature Range

Dn+1

Timing Waveform for Mux’d Port Burst Write Cycle

tCYC

tCH tCL

CLK

tSC

CE

tSW

R/W

tSAD

tHAD

ADS

tSCN

CNTEN

tSA tHA

tSD tHD

ADDR / DATA

An

Dn Dn+1

Dn+2

11 of 23

August 22, 2007

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet IDT70P9268L.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDT70P9268L | MOBILE MULTIMEDIA INTERFACE VERY LOW POWER 1.8V 16K X 16 SYNCHRONOUS DUAL-PORT STATIC RAM | IDT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |