|

|

PDF K4Q153212M Data sheet ( Hoja de datos )

| Número de pieza | K4Q153212M | |

| Descripción | (K4Q153211M / K4Q153212M) 512kx32bit CMOS Quad Casdram | |

| Fabricantes | Samsung Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de K4Q153212M (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

K4Q153211M, K4Q153212M

CMOS DRAM

512K x 32Bit CMOS Quad CAS DRAM with EDO

DESCRIPTION

This is a 524,288 x 32 bit Extended Data Out CMOS DRAM. Extended Data Out Mode offers high speed random access of memory cells

within the same row, so called Hyper Page Mode. Power supply voltage (+5.0V or +3.3V), refresh cycle 1K, access time (-50 or -60),

power consumption(Normal or Low power) and SOJ package type are optional features of this family. All of this family have CAS-before-

RAS refresh, RAS-only refresh and Hidden refresh capabilities. Furthermore, Self-refresh operation is available in L-version. This

512Kx32 EDO Mode Quad CAS DRAM is fabricated using Samsung's advanced CMOS process to realize high band-width, low power

consumption and high reliability.

FEATURES

• Part Identification

- K4Q153211M-JC (5.0V, 1K Ref.)

- K4Q153211M-JL (5.0V, 1K Ref. LP)

- K4Q153212M-JC (3.3V, 1K Ref.)

- K4Q153212M-JL (3.3V, 1K Ref. LP)

• Active Power Dissipation

Speed

-50

-60

3.3V

-

540

Unit : mW

5.0V

880

825

• Extended Data Out Mode operation

(Fast Page Mode with Extended Data Out)

• Four separate CAS pins provide for separate I/O operation

• CAS-before-RAS refresh capability

• RAS-only and Hidden refresh capability

• Self-refresh capability (L-ver only)

• TTL(5V)/LVTTL(3.3V) compatible inputs and outputs

• Early Write or output enable controlled write

• JEDEC Standard pinout

• Plastic SOJ 400mil x 1125mil package

• Single +5.0V±0.5V power supply(5V product)

• Single +3.3V±0.3V power supply(3.3V product)

• Refresh Cycles

Part

NO.

153211M-J

153212M-J

VCC Refresh

cycle

5.0V 1K

3.3V 1K

Refresh period

Normal L-ver

16ms 128ms

16ms 128ms

• Performance Range

Speed

-50

-60

tRAC

50ns

60ns

tCAC

15ns

17ns

tRC

84ns

104ns

tHPC

20ns

27ns

Remark

5.0V only

5V/3.3V

FUNCTIONAL BLOCK DIAGRAM

RAS

CAS0-3

W

A0 - A9

A0 - A8

Control

Clocks

VBB Generator

Vcc

Vss

Refresh Timer

Refresh Control

Refresh Counter

Row Address Buffer

Col. Address Buffer

Row Decoder

Memory

Array

524,288 x 32

Cells

Column Decoder

CAS0

D/I Buffer

CAS0

D/O Buffer

CAS1

D/I Buffer

CAS1

D/O Buffer

CAS2

D/I Buffer

CAS2

D/O Buffer

CAS3

D/I Buffer

CAS3

D/O Buffer

DQ0

to

DQ7

DQ8

to

DQ15

OE

DQ16

to

DQ23

DQ24

to

DQ31

SAMSUNG ELECTRONICS CO., LTD. reserves the right to

change products and specifications without notice.

1 page

www.DataSheet4U.com

K4Q153211M, K4Q153212M

CAPACITANCE (TA=25°C, VCC=5V or 3.3V, f=1MHz)

Parameter

Symbol

Input capacitance [A0 ~ A9]

CIN1

Input capacitance [RAS, CASx, W, OE]

CIN2

Output capacitance [DQ0 - DQ31]

CDQ

Min

-

-

-

CMOS DRAM

Max Units

5 pF

7 pF

7 pF

AC CHARACTERISTICS (0°C≤TA≤70°C, See note 1,2)

Test condition (5V device) : VCC=5.0V±0.5V, Vih/Vil=2.4/0.8V, Voh/Vol=2.0/0.8V

Test condition (3.3V device) : VCC=3.3V±0.3V, Vih/Vil=2.2/0.8V, Voh/Vol=2.0/0.8V

Parameter

Symbol

-50*1

Min Max

Random read or write cycle time

Read-modify-write cycle time

Access time from RAS

Access time from CAS

Access time from column address

CAS to output in Low-Z

Output buffer turn-off delay from CAS

OE to output in Low-Z

Transition time (rise and fall)

RAS precharge time

RAS pulse width

RAS hold time

CAS hold time

CAS pulse width

RAS to CAS delay time

RAS to column address delay time

CAS to RAS precharge time

Row address set-up time

Row address hold time

Column address set-up time

Column address hold time

Column address to RAS lead time

Read command set-up time

Read command hold time referenced to CAS

Read command hold time referenced to RAS

Write command hold time

Write command pulse width

Write command to RAS lead time

Write command to CAS lead time

Note) *1 : 5V only

tRC

tRWC

tRAC

tCAC

tAA

tCLZ

tCEZ

tOLZ

tT

tRP

tRAS

tRSH

tCSH

tCAS

tRCD

tRAD

tCRP

tASR

tRAH

tASC

tCAH

tRAL

tRCS

tRCH

tRRH

tWCH

tWP

tRWL

tCWL

84

115

3

3

3

2

30

50

13

40

8

20

15

5

0

10

0

8

25

0

0

0

10

10

13

8

50

15

25

13

50

10K

10K

35

25

-60

Min Max

104

140

60

17

30

3

3 15

3

2 50

40

60 10K

17

48

12 10K

20 43

15 30

5

0

10

0

10

30

0

0

0

10

10

15

10

Units Notes

ns

ns

ns 3,4,10

ns 3,4,5,18

ns 3,10

ns 3,18

ns 6,11,18

ns 3

ns 2

ns

ns

ns 14

ns 17

ns 23

ns 4,16

ns 10

ns 15

ns

ns

ns 16

ns 16

ns

ns

ns 8,15

ns 8

ns 14

ns

ns

ns 17

5 Page

www.DataSheet4U.com

K4Q153211M, K4Q153212M

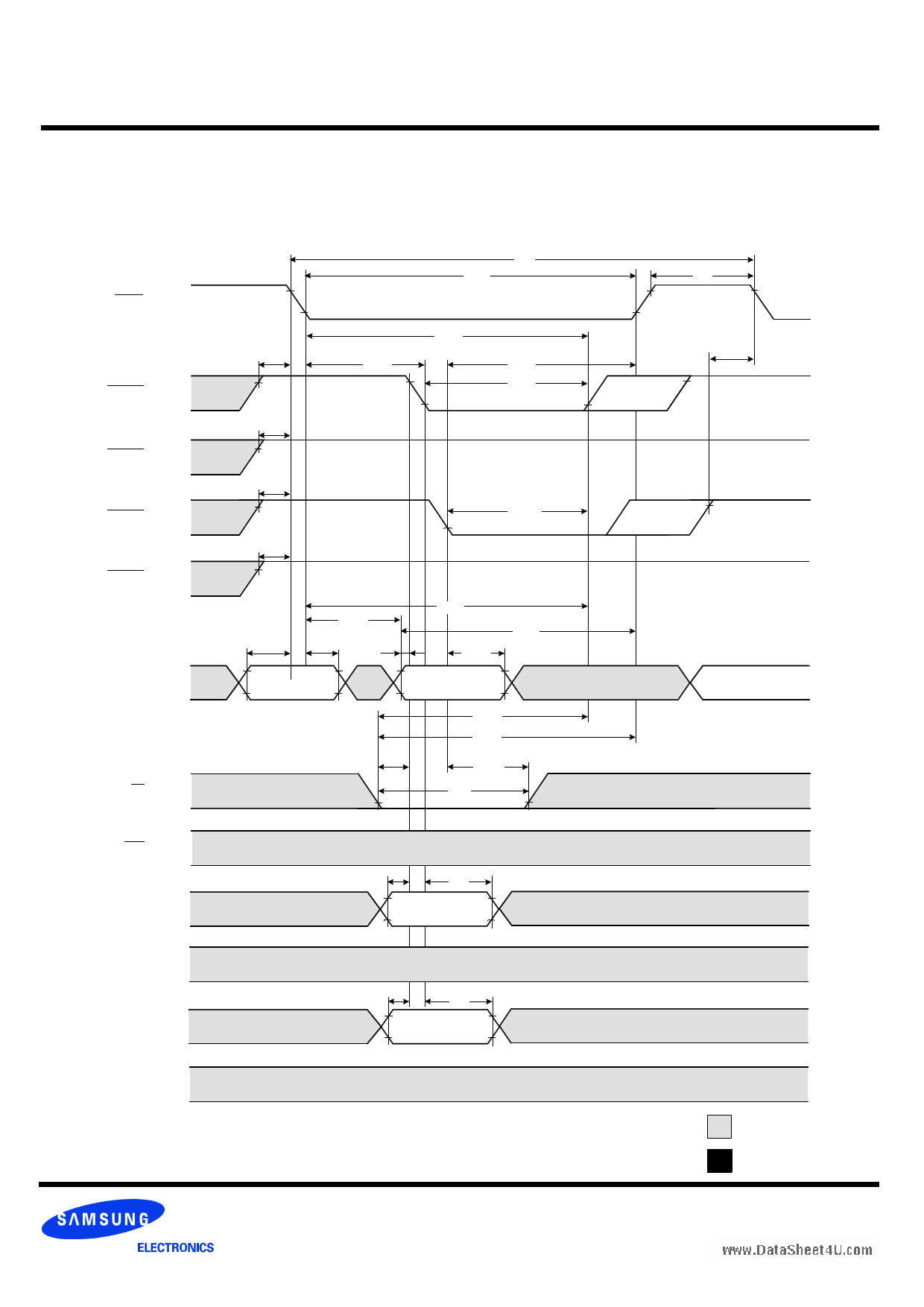

BYTE WIDE WRITE CYCLE ( EARLY WRITE )

NOTE : DOUT = OPEN

VIH -

RAS

VIL -

VIH -

CAS0

VIL -

VIH -

CAS1

VIL -

VIH -

CAS2

VIL -

VIH -

CAS3

VIL -

VIH -

A

VIL -

VIH -

W

VIL -

VIH -

OE

VIL -

DQ0~7 VIH -

VIL -

VIH -

DQ8~15

VIL -

VIH -

DQ16~23

VIL -

VIH -

DQ24~31

VIL -

tRAS

tRC

tCRP

tCRP

tCRP

tCRP

tRCD

tCSH

tRSH

tCAS

tCLCH

tASR

tRAD

tRAH

tASC

ROW

ADDRESS

tCSH

tCAH

COLUMN

ADDRESS

tRAL

tWCS

tCWL

tRWL

tWCH

tWP

tDS tDH

DATA-IN

tDS tDH

DATA-IN

CMOS DRAM

tRP

tCRP

Don't care

Undefined

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet K4Q153212M.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| K4Q153212M | (K4Q153211M / K4Q153212M) 512kx32bit CMOS Quad Casdram | Samsung Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |