|

|

PDF AZ10ELT22 Data sheet ( Hoja de datos )

| Número de pieza | AZ10ELT22 | |

| Descripción | CMOS/TTL to Differential PECL Translator | |

| Fabricantes | Arizona Microtek | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AZ10ELT22 (archivo pdf) en la parte inferior de esta página. Total 6 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

ARIZONA MICROTEK, INC.

AZ10ELT22

AZ100ELT22

CMOS/TTL to Differential PECL Translator

FEATURES

PACKAGE AVAILABILITY

• Green / RoHS Compliant /

Lead (Pb) Free package available

• 0.5ns Typical Propagation Delay

• <100ps Typical Output to Output

Skew

PACKAGE

SOIC 8

SOIC 8 RoHS

Compliant / Lead

(Pb) Free

PART NUMBER

AZ10ELT22D

AZ10ELT22D+

MARKING NOTES

AZM10

ELT22

1,2,4

AZM10+

ELT22

1,2,4

• Differential PECL Outputs

• Flow Through Pinouts

• Operating Range of 3.0V to 5.5V

• Direct Replacement for

ON Semiconductor MC10ELT22 &

MC100ELT22

SOIC 8

SOIC 8 RoHS

Compliant / Lead

(Pb) Free

TSSOP 8

AZ100ELT22D

AZ100ELT22D+

AZ10ELT22T

AZM100

ELT22

AZM100+

ELT22

AZT

LT22

1,2,4

1,2,4

1,2,4

• IBIS Model Files Available on

Arizona Microtek Website

TSSOP 8 RoHS

Compliant / Lead

(Pb) Free

AZ10ELT22T+

AZT+

LT22

1,2,4

TSSOP 8

AZ100ELT22T

AZH

LT22

1,2,4

DESCRIPTION

TSSOP 8 RoHS

Compliant / Lead

(Pb) Free

AZ100ELT22T+

AZH+

LT22

1,2,4

1 Add R1 at end of part number for 7 inch (1K parts), R2 for 13 inch (2.5K parts)

The AZ10/100ELT22 is a dual

Tape & Reel.

2 Date code format: “Y” or “YY” for year followed by “WW” for week.

CMOS/TTL to differential PECL

translator. Because PECL (Positive ECL)

3 Parts marked JNB for date codes prior to 4WW (prior to 2004).

4 Date code “YWW” or “YYWW” on underside of part.

levels are used, only VCC and ground are

required. The small outline packaging and the low skew, dual gate design of the ELT22 makes it ideal for

applications that require the translation of a clock and a data signal.

The ELT22 is available in both PECL standards: the 10ELT is compatible with PECL 10K logic levels while

the 100ELT is compatible with PECL 100K logic levels.

NOTE: Specifications in PECL tables are valid when thermal equilibrium is established.

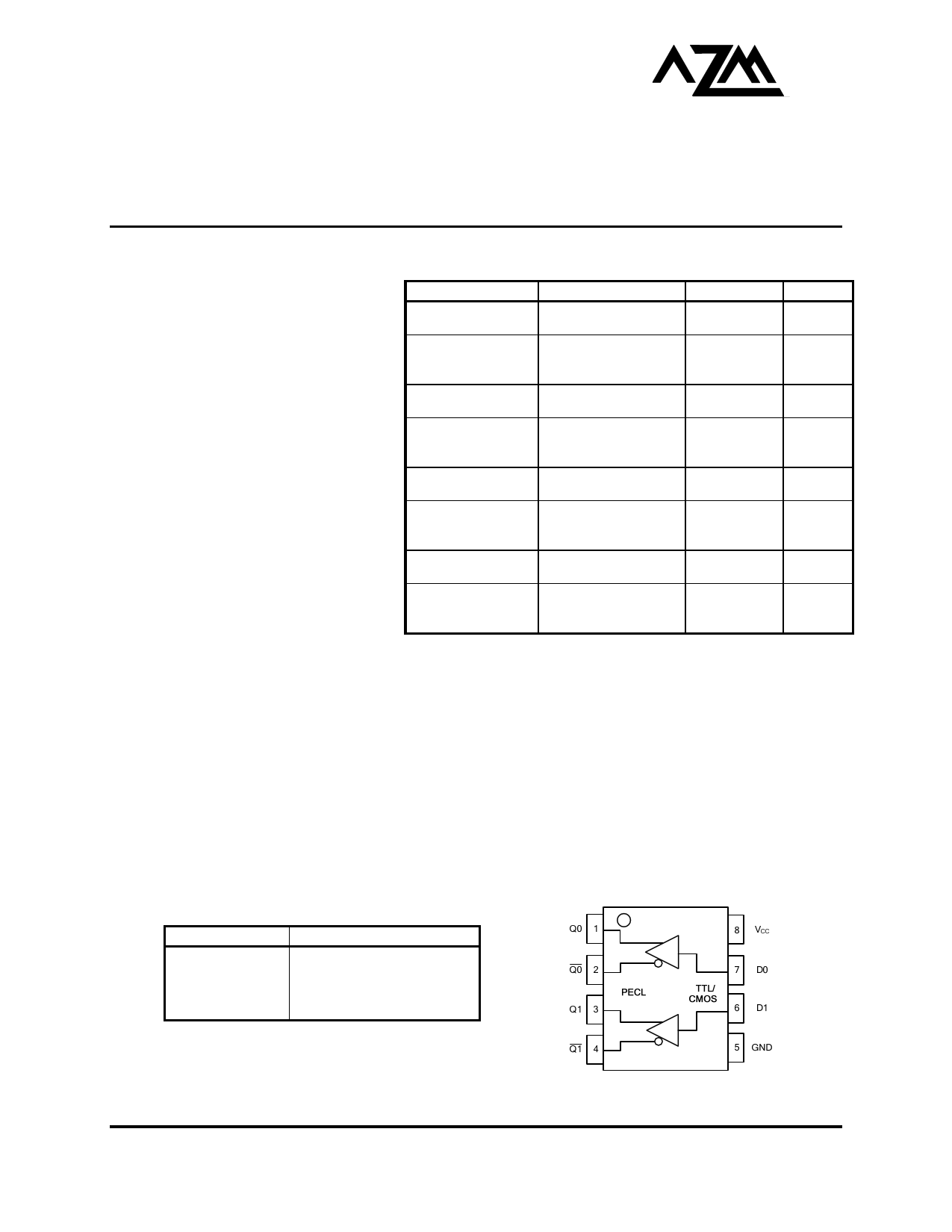

PIN DESCRIPTION

PIN

Q0, Q¯¯0, Q1, Q¯¯1

D0, D1

VCC

GND

FUNCTION

Differential PECL Outputs

CMOS/TTL Input

Positive Supply

Ground

LOGIC DIAGRAM AND

PINOUT

1630 S. STAPLEY DR., SUITE 127 • MESA, ARIZONA 85204 • USA • (480) 962-5881 • FAX (480) 890-2541

www.azmicrotek.com

1 page

AZ10ELT22

AZ100ELT22

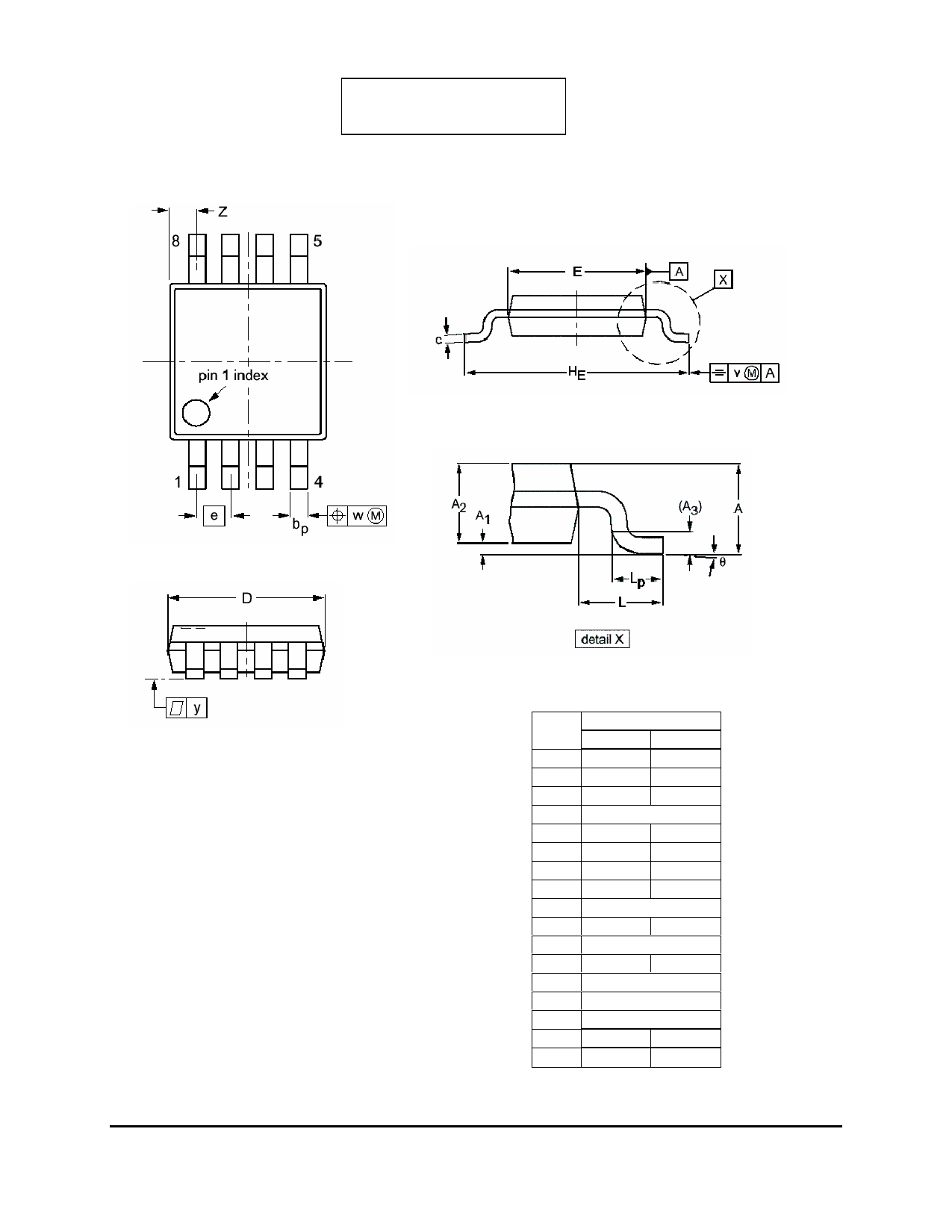

PACKAGE DIAGRAM

TSSOP 8

NOTES:

1. DIMENSIONS D AND E DO NOT

INCLUDE MOLD PROTRUSION.

2. MAXIMUM MOLD PROTRUSION

FOR D IS 0.15mm.

3. MAXIMUM MOLD PROTRUSION

FOR E IS 0.25mm.

DIM

A

A1

A2

A3

bp

c

D

E

e

HE

L

Lp

v

w

y

Z

θ

MILLIMETERS

MIN MAX

1.10

0.05 0.15

0.75 0.95

0.25

0.22 0.40

0.13 0.23

2.90 3.10

2.90 3.10

0.65

4.75 5.05

0.95

0.40 0.70

0.10

0.08

0.10

0.38 0.64

0O 6O

April 2007 * REV - 7

www.azmicrotek.com

5

5 Page | ||

| Páginas | Total 6 Páginas | |

| PDF Descargar | [ Datasheet AZ10ELT22.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AZ10ELT20 | CMOS/TTL to Differential PECL Translator | Arizona |

| AZ10ELT22 | CMOS/TTL to Differential PECL Translator | Arizona Microtek |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |