|

|

PDF XRT72L56 Data sheet ( Hoja de datos )

| Número de pieza | XRT72L56 | |

| Descripción | SIX CHANNEL DS3/E3 FRAMER IC | |

| Fabricantes | Exar | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XRT72L56 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

áçwww.DataSheet4U.com

PRELIMINARY

XRT72L56

JANUARY 2001

SIX CHANNEL DS3/E3 FRAMER IC WITH HDLC CONTROLLER

REV. P1.1.2

GENERAL DESCRIPTION

The XRT72L56, 6 Channel DS3/E3 Framer is de-

signed to accept “User Data” from the Terminal

Equipment and insert this data into the “payload” bit-

fields within an “outbound” DS3/E3 Data Stream.

The XRT72L56 DS3/E3 Framer support full-duplex

data flow between Terminal Equipment and an LIU

(Line Interface Unit) . The Framer will transmit, re-

ceive and process data in the DS3-C-bit Parity, DS3-

M13, E3-ITU-T G.751 and E3-ITU-T G.832 Framing

Formats.

In addition, XRT72L56 has 6 independent high speed

HDLC controllers both on the receive and transmit

data paths which can be optionally configured to sup-

port Framer Relay applications.

The Transmit Sections, include a Transmit Payload

Data Input Interface, a Transmit Overhead data Input

Interface Section, a Transmit HDLC Controller, a

Transmit DS3/E3 Framer block and a Transmit LIU In-

terface Block which permits the Terminal Equipment

to transmit data to a remote terminal.

The Receive Sections, consist of a Receive LIU Inter-

face, a Receive DS3/E3 Framer, a Receive HDLC

Controller, a Receive Payload Data Output Interface,

and a Receive Overhead Data Interface which allows

the local terminal equipment to receive data from re-

mote terminal equipment.

The Microprocessor Interface is used to configure the

Framer in different operating modes and monitor the

performance of the Framer.

The Performance Monitor Sections consist of a large

number of "Reset-upon-Read" and "Read-Only" reg-

isters that contain cumulative and "one-second" sta-

tistics that reflect the performance/status of the chan-

nels.

FEATURES

• Transmits, Receives and Processes data in the

DS3-C-bit Parity, DS3-M13, E3-ITU-T G.751 and

E3-ITU-T G.832 Framing Formats.

• Per Channel High Speed HDLC Controllers.

• Interfaces to all Popular Microprocessors

• Extensive Performance Monitoring support.

• Available in a 388 Ball PBGA package

• 3.3V Power Supply with 5V Tolerant I/O

• Operating Temperature -40°C to +85°C

APPLICATIONS

• Digital Cross Connects

• CSU/DSU Equipment.

• ADD/Drop Multiplexers

• DS3/E3 Frame Relay Equipment

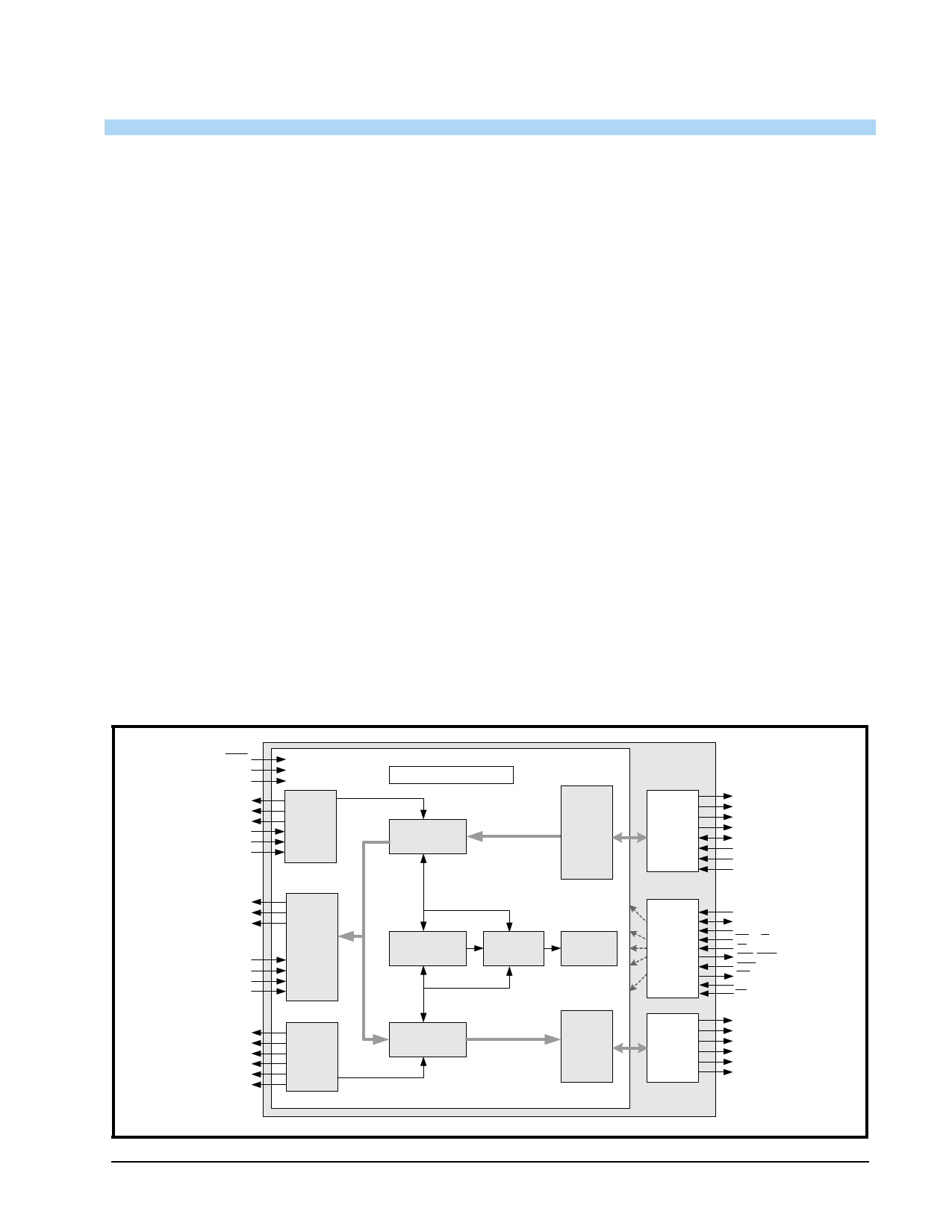

FIGURE 1. BLOCK DIAGRAM OF THE XRT72L56

Reset

TestMode

NibbleLnTF

TxOHEnable

TxOHClk

TxOHFrame

TxAISEn

TxOH

TxOHIns

T3/E3

Transmit

Overhead

Interface

TxLineClk[n:0]

TxPOS[n:0]

TxNEG[n:0]

RxLineClk[n:0]

RxPOS[n:0]

RxNEG[n:0]

ExtLOS

RxOHEnable[n:0]

RxOHClk[n:0]

RxOH[n:0]

RxRed[n:0]

RxOHFrame[n:0]

RxOOF[n:0]

LIU

Interface/

Controller

T3/E3

Receive

Overhead

Interface

Typical Channel n

Where n = 0, 1, 2, 3, 4 & 5

T3/E3 Transmit

Framer

T3/E3

transmit

Input

T3 FEAC & Data

Link Controller

Performance

Monitor

Interrupt

Controller

T3/E3 Receive

Framer

T3/E3

Receive

Output

HDLC

controller

uP

Interface

HDLC

controller

TxOHInd[n:0]

TxNibFrame[n:0]

TxFrame[n:0]

TxNibClk[n:0]

TxLnClk[n:0]

TxFrameRef[n:0]

TxNib[n:0]

TxSer[n:0]

A(11:0)

D(7:0)

ALE_AS

WR_R/W

CS

RDY_DTCK

Reset

INT

MOTO

RD_DS

RxClk[n:0]

RxOHind[n:0]

RxFrame[n:0]

RxNib[n:0]

RxSer[n:0]

RxOUTClk[n:0]

Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

1 page

áç

PRELIMINARY

XRT72L56

SIX CHANNEL DS3/E3 FRAMER IC WITH HDLC CONTROLLER

REV. P1.1.2

RXE3 LAPD CONTROL REGISTER (ADDRESS = 0X18) ............................................................................. 88

RXE3 LAPD STATUS REGISTER (ADDRESS = 0X19) ................................................................................ 88

RXE3 NR BYTE REGISTER (ADDRESS = 0X1A) ........................................................................................ 89

RXE3 GC BYTE REGISTER (ADDRESS = 0X1B) ....................................................................................... 89

RXE3 TTB-0 REGISTER (ADDRESS = 0X1C) ............................................................................................ 90

RXE3 TTB-1 REGISTER (ADDRESS = 0X1D) ............................................................................................ 90

RXE3 TTB-2 REGISTER (ADDRESS = 0X1E) ............................................................................................ 90

RXE3 TTB-3 REGISTER (ADDRESS = 0X1F) ............................................................................................ 91

RXE3 TTB-4 REGISTER (ADDRESS = 0X20) ............................................................................................ 91

RXE3 TTB-5 REGISTER (ADDRESS = 0X21) ............................................................................................ 91

RXE3 TTB-6 REGISTER (ADDRESS = 0X22) ............................................................................................ 91

RXE3 TTB-7 REGISTER (ADDRESS = 0X23) ............................................................................................ 92

RXE3 TTB-8 REGISTER (ADDRESS = 0X24) ............................................................................................ 92

RXE3 TTB-9 REGISTER (ADDRESS = 0X25) ............................................................................................ 92

RXE3 TTB-10 REGISTER (ADDRESS = 0X26) .......................................................................................... 93

RXE3 TTB-11 REGISTER (ADDRESS = 0X27) .......................................................................................... 93

RXE3 TTB-12 REGISTER (ADDRESS = 0X28) .......................................................................................... 93

RXE3 TTB-13 REGISTER (ADDRESS = 0X29 ........................................................................................... 93

RXE3 TTB-14 REGISTER (ADDRESS = 0X2A) .......................................................................................... 94

RXE3 TTB-15 REGISTER (ADDRESS = 0X2B) .......................................................................................... 94

RXE3 SSM REGISTER (ADDRESS = 0X2B) ................................................................................................ 94

2.4.4 Receive E3 Framer Configuration Registers (ITU-T G.751) ................................................................... 95

RXE3 CONFIGURATION & STATUS REGISTER - 1 G.751 (ADDRESS = 0X10) ............................................. 95

RXE3 CONFIGURATION & STATUS REGISTER - 2 (ADDRESS = 0X11) ........................................................ 95

RXE3 INTERRUPT ENABLE REGISTER - 1 (ADDRESS = 0X12) ................................................................... 96

RXE3 INTERRUPT ENABLE REGISTER - 2 (ADDRESS = 0X13) ................................................................... 97

RXE3 INTERRUPT STATUS REGISTER - 1 (ADDRESS = 0X14) ................................................................... 97

RXE3 INTERRUPT STATUS REGISTER - 2 (ADDRESS = 0X15) ................................................................... 98

RXE3 LAPD CONTROL REGISTER (ADDRESS = 0X18) ............................................................................. 99

RXE3 LAPD STATUS REGISTER (ADDRESS = 0X19) ................................................................................ 99

RXE3 SERVICE BIT REGISTER (ADDRESS = 0X1A) ................................................................................. 100

2.4.5 Transmit DS3 Configuration Registers .................................................................................................. 100

TRANSMIT DS3 CONFIGURATION REGISTER (ADDRESS = 0X30) ............................................................. 101

TRANSMIT DS3 FEAC CONFIGURATION & STATUS REGISTER (ADDRESS = 0X31) .................................. 102

TXDS3 FEAC REGISTER (ADDRESS = 0X32) ........................................................................................ 103

TXDS3 LAPD CONFIGURATION REGISTER (ADDRESS = 0X33) ............................................................... 103

TXDS3 LAPD STATUS AND INTERRUPT REGISTER (ADDRESS = 0X34) ................................................... 104

TXDS3 M-BIT MASK REGISTER (ADDRESS = 0X35) ............................................................................... 104

TXDS3 F-BIT MASK REGISTER - 1 (ADDRESS = 0X36) ........................................................................... 105

TXDS3 F-BIT MASK REGISTER - 2 (ADDRESS = 0X37) ........................................................................... 106

TXDS3 F-BIT MASK REGISTER - 3 (ADDRESS = 0X38) ........................................................................... 106

TXDS3 F-BIT MASK REGISTER - 4 (ADDRESS = 0X39) ........................................................................... 106

2.4.6 Transmit E3 (ITU-T G.832) Configuration Registers ............................................................................. 106

TXE3 CONFIGURATION REGISTER (ADDRESS = 0X30) ............................................................................ 107

TXE3 LAPD CONFIGURATION REGISTER (ADDRESS = 0X33) ................................................................. 108

TXE3 LAPD STATUS AND INTERRUPT REGISTER (ADDRESS = 0X34) ...................................................... 108

TXE3 GC BYTE REGISTER (ADDRESS = 0X35) ...................................................................................... 109

TXE3 MA BYTE REGISTER (ADDRESS = 0X36) ...................................................................................... 110

TXE3 MA BYTE REGISTER (ADDRESS = 0X36) ...................................................................................... 110

TXE3 NR BYTE REGISTER (ADDRESS = 0X37) ...................................................................................... 110

TXE3 TTB-0 REGISTER (ADDRESS = 0X38) ........................................................................................... 111

TXE3 TTB-1 REGISTER (ADDRESS = 0X39) ........................................................................................... 111

TXE3 TTB-2 REGISTER (ADDRESS = 0X3A) .......................................................................................... 111

TXE3 TTB-3 REGISTER (ADDRESS = 0X3B) .......................................................................................... 112

TXE3 TTB-4 REGISTER (ADDRESS = 0X3C) .......................................................................................... 112

III

5 Page

áç

PRELIMINARY

XRT72L56

SIX CHANNEL DS3/E3 FRAMER IC WITH HDLC CONTROLLER

REV. P1.1.2

RX DS3 LAPD CONTROL REGISTER (ADDRESS = 0X18) ........................................................................ 221

RX DS3 LAPD STATUS REGISTER (ADDRESS = 0X19) .......................................................................... 221

TABLE 41: THE RELATIONSHIP BETWEEN RXLAPDTYPE[1:0] AND THE RESULTING LAPD MESSAGE TYPE AND

SIZE ...................................................................................................................................................... 222

Figure 86. Flow Chart depicting the Functionality of the LAPD Receiver .......................................... 223

4.3.4 The Receive Overhead Data Output Interface ...................................................................................... 223

Figure 87. A Simple Illustration of the Receive Overhead Output Interface block ............................. 224

TABLE 42: LISTING AND DESCRIPTION OF THE PIN ASSOCIATED WITH THE RECEIVE OVERHEAD DATA OUTPUT

INTERFACE BLOCK ................................................................................................................................ 225

Figure 88. Illustration of how to interface the Terminal Equipment to the Receive Overhead Data Output

Interface block (for Method 1). ............................................................................................................ 225

TABLE 43: THE RELATIONSHIP BETWEEN THE NUMBER OF RISING CLOCK EDGES IN RXOHCLK, (SINCE RXO-

HFRAME WAS LAST SAMPLED "HIGH") TO THE DS3 OVERHEAD BIT, THAT IS BEING OUTPUT VIA THE RXOH OUTPUT

PIN ....................................................................................................................................................... 226

Figure 89. Illustration of the signals that are output via the Receive Overhead Output Interface (for Method

1). ........................................................................................................................................................ 228

TABLE 44: LISTING AND DESCRIPTION OF THE PIN ASSOCIATED WITH THE RECEIVE OVERHEAD DATA OUTPUT

INTERFACE BLOCK (METHOD 2) ............................................................................................................. 229

Figure 90. Illustration of how to interface the Terminal Equipment to the Receive Overhead Data Output

Interface block (for Method 2). ............................................................................................................ 230

TABLE 45: THE RELATIONSHIP BETWEEN THE NUMBER OF RXOHENABLE OUTPUT PULSES ((SINCE RXOHFRAME

WAS LAST SAMPLED "HIGH") TO THE DS3 OVERHEAD BIT, THAT IS BEING OUTPUT VIA THE RXOH OUTPUT PIN

231

Figure 91. Illustration of the signals that are output via the Receive Overhead Data Output Interface block

(for Method 2). ..................................................................................................................................... 233

4.3.5 The Receive Payload Data Output Interface ......................................................................................... 233

Figure 92. A Simple illustration of the Receive Payload Data Output Interface block ........................ 234

TABLE 46: LISTING AND DESCRIPTION OF THE PIN ASSOCIATED WITH THE RECEIVE PAYLOAD DATA OUTPUT IN-

TERFACE BLOCK .................................................................................................................................... 235

Figure 93. Illustration of the XRT72L56 DS3/E3 Framer IC being interfaced to the Receive Terminal Equip-

ment (Serial Mode Operation) ............................................................................................................. 236

Figure 94. An Illustration of the behavior of the signals between the Receive Payload Data Output Interface

block of the XRT72L56 and the Terminal Equipment (Serial Mode Operation) .................................. 237

Figure 95. Illustration of the XRT72L56 DS3/E3 Framer IC being interfaced to the Receive Section of the

Terminal Equipment (Nibble-Mode Operation) ................................................................................... 238

Figure 96. An Illustration of the Behavior of the signals between the Receive Payload Data Output Interface

Block of the XRT72L56 and the Terminal Equipment (Nibble-Mode Operation). ............................... 239

4.3.6 Receive Section Interrupt Processing ................................................................................................... 239

BLOCK INTERRUPT ENABLE REGISTER (ADDRESS = 0X04) ..................................................................... 240

RXDS3 INTERRUPT ENABLE REGISTER (ADDRESS = 0X12) .................................................................... 240

RXDS3 INTERRUPT STATUS REGISTER (ADDRESS = 0X13) .................................................................... 241

RXDS3 CONFIGURATION & STATUS REGISTER (ADDRESS = 0X10) ......................................................... 241

RXDS3 INTERRUPT ENABLE REGISTER (ADDRESS = 0X12) .................................................................... 242

RXDS3 INTERRUPT STATUS REGISTER (ADDRESS = 0X13) .................................................................... 242

RXDS3 CONFIGURATION & STATUS REGISTER (ADDRESS = 0X10) ......................................................... 242

RXDS3 INTERRUPT ENABLE REGISTER (ADDRESS = 0X12) .................................................................... 243

RXDS3 INTERRUPT STATUS REGISTER (ADDRESS = 0X13) .................................................................... 243

RXDS3 CONFIGURATION & STATUS REGISTER (ADDRESS = 0X10) ......................................................... 244

RXDS3 INTERRUPT ENABLE REGISTER (ADDRESS = 0X12) .................................................................... 244

RXDS3 INTERRUPT STATUS REGISTER (ADDRESS = 0X13) .................................................................... 245

RXDS3 CONFIGURATION & STATUS REGISTER (ADDRESS = 0X10) ......................................................... 245

RXDS3 INTERRUPT ENABLE REGISTER (ADDRESS = 0X12) .................................................................... 245

RXDS3 INTERRUPT STATUS REGISTER (ADDRESS = 0X13) .................................................................... 246

RXDS3 STATUS REGISTER (ADDRESS = 0X11) ...................................................................................... 246

RXDS3 INTERRUPT ENABLE REGISTER (ADDRESS = 0X12) .................................................................... 246

IX

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet XRT72L56.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XRT72L50 | SINGLE CHANNEL DS3/E3 FRAMER IC | Exar Corporation |

| XRT72L52 | TWO CHANNEL DS3/E3 FRAMER IC | Exar |

| XRT72L53 | THREE CHANNEL DS3/E3 FRAMER IC | Exar Corporation |

| XRT72L54 | FOUR CHANNEL DS3/E3 FRAMER IC | Exar |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |