|

|

PDF XRT84L38 Data sheet ( Hoja de datos )

| Número de pieza | XRT84L38 | |

| Descripción | OCTAL T1/E1/J1 FRAMER | |

| Fabricantes | Exar Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XRT84L38 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

XRT84L38

OCTAL T1/E1/J1 FRAMER

SEPTEMBER 2006

REV. 1.0.1

GENERAL DESCRIPTION

The XRT84L38 is an eight-channel 1.544 Mbit/s or

2.048 Mbit/s DS1/E1/J1 framing controller. The

XRT84L38 contains an integrated DS1/E1/J1 framer

which provides DS1/E1/J1 framing and error

accumulation in accordance with ANSI/ITU_T

specifications. Each framer has its own framing

synchronizer and transmit-receive slip buffers, and

can be independently enabled or disabled as

required and can be configured to frame to the

common DS1/E1/J1 signal formats

Each Framer block contains its own Transmit and

Receive T1/E1/J1 Framing function including 3 HDLC

controllers to support V5.2. Each Transmit HDLC

controller encapsulates contents of the Transmit

HDLC buffers into LAPD Message frames. Each

Receive HDLC controller extracts payload content of

Receive LAPD Message frames from the incoming

T1/E1/J1 data stream and writes it into the Receive

HDLC buffer. Each framer also contains a Transmit

and Overhead Data Input port, which permits Data

Link Terminal Equipment direct access to the

outbound T1/E1/J1 frames Likewise, a Receive

Overhead output data port permits Data Link Terminal

Equipment direct access to the Data Link bits of the

inbound T1/E1/J1 frames.

The XRT84L38 fully meets all of the latest T1/E1/J1

specifications: ANSI T1/E1.107-1988, ANSI T1/

E1.403-1995, ANSI T1/E1.231-1993, ANSI T1/

E1.408-1990, AT&T TR 62411 (12-90) TR54016, and

ITU G-703, G.704, G706 and G.733, AT&T Pub.

43801, and ETS 300 011, 300 233, JT G.703, JT

G.704, JT G706, I.431. Extensive test and diagnostic

functions include Loop-backs, Boundary scan,

Pseudo Random bit sequence (PRBS) test pattern

generation, Performance Monitor, Bit Error Rate

(BER) meter, forced error insertion, and LAPD

unchannelized data payload processing according to

ITU-T standard Q.921.

Applications and Features (next page)

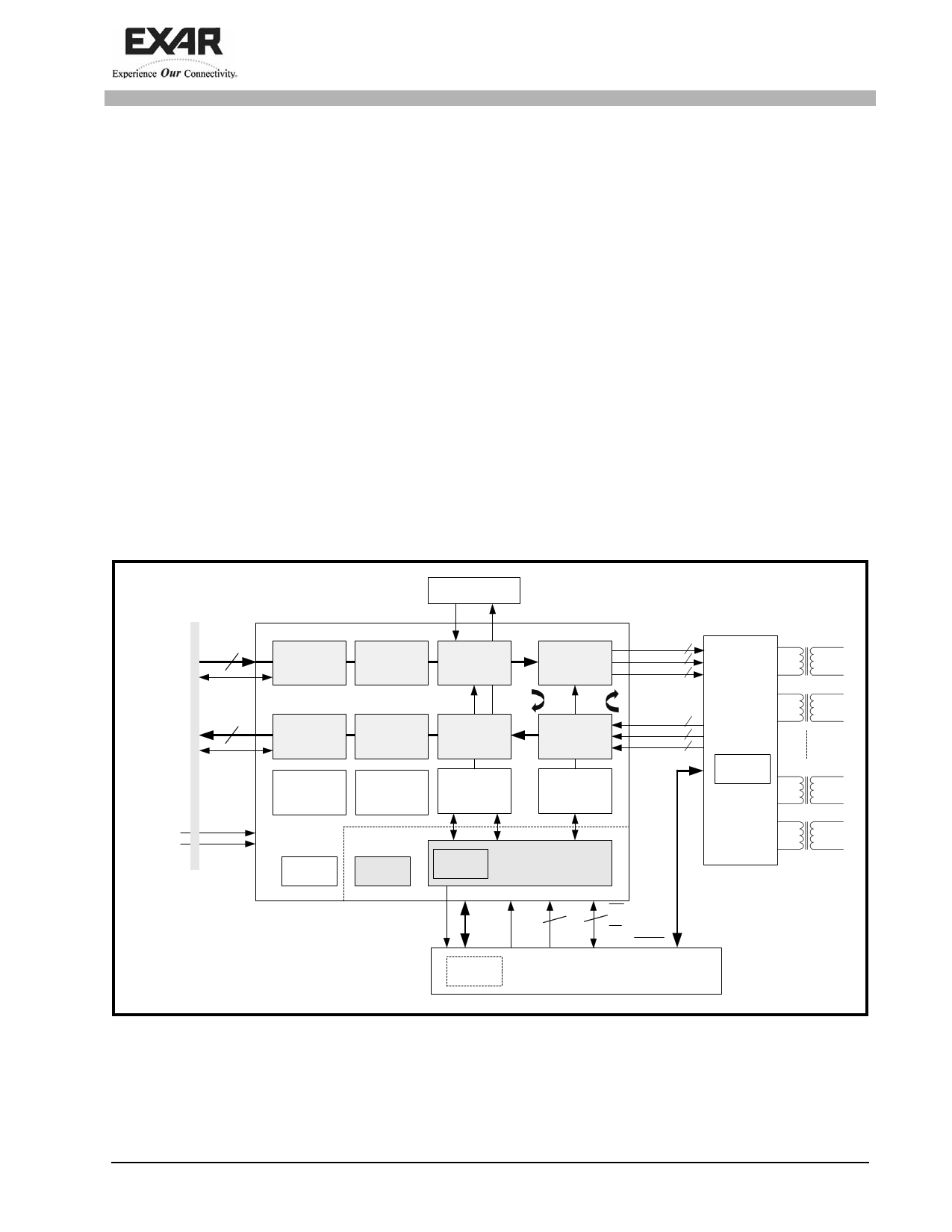

FIGURE 1. XRT84L38 8-CHANNEL DS1 (T1/E1/J1) FRAMER

Local PCM

Highway

XRT84L38

1 of 8-channels

8

Tx Serial

Clock

Tx Serial

Data In

8

Rx Serial

Clock

Rx Serial

Data Out

PRBS

Generator &

Analyser

External Data

Link Controller

Tx Overhead In

Rx Overhead Out

2-Frame

Slip Buffer

Elastic Store

Tx Framer

2-Frame

Slip Buffer

Elastic Store

Rx Framer

Performance

Monitor

HDLC (LAPD)

Controller &

96-byte Buffer

Tx Encoder

LIU

Interface

LLB LB

Rx Encoder

LIU

Interface

LIU &

Loopback

Control

TxPOS 8

TxNEG 8

TxLineCLK 8

8 DS1/E1

Channels

1.544/2.048 MHz

XRT83L38

TPOS

TNEG

TCLK1

Tx1

Twisted

Pair

RxPOS 8

RxNEG 8

RxLineCLK 8

Rx1

RPOS

RNEG

RCLK1

µP

Interface

Tx8

Twisted

Pair

8kHz sync

OSC

Back Plane

1.544-16.384 Mbit/s

Signaling &

Alarms

System (Terminal) Side

JTAG

DMA

Interface

Microprocessor

Interface

Interrupt

D[7:0]

Memory

A[6:0]

3

4

WR

ALE_AS

Channel RD

Select

RDY_DTACK

Intel/Motorola µP

Configuration, Control &

Status Monitor

Rx8

8-CH T1/E1/LIU

Host Mode

Line Side

Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

1 page

REV. 1.0.1

TABLE OF CONTENTS

XRT84L38

OCTAL T1/E1/J1 FRAMER

GENERAL DESCRIPTION................................................................................................ 1

FIGURE 1. XRT84L38 8-CHANNEL DS1 (T1/E1/J1) FRAMER ............................................................................................................ 1

APPLICATIONS .............................................................................................................................................. 2

FEATURES .................................................................................................................................................... 2

ORDERING INFORMATION ................................................................................................................... 3

FIGURE 2. PIN OUT OF THE XRT84L38 TOP VIEW (SEE PIN LIST FOR NAMES AND FUNCTION) ............................................................ 4

TABLE OF CONTENTS ..................................................................................................... I

TABLE 1: LIST BY PIN NUMBER ......................................................................................................................................................... 5

PIN DESCRIPTIONS ......................................................................................................... 5

TRANSMIT SERIAL DATA INPUT...................................................................................................................... 5

OVERHEAD INTERFACE ............................................................................................................................... 14

RECEIVE SERIAL DATA OUTPUT .................................................................................................................. 16

RECEIVE DECODER LIU INTERFACE ............................................................................................................. 23

TRANSMIT ENCODER LIU INTERFACE ........................................................................................................... 23

TIMING ....................................................................................................................................................... 24

LIU CONTROL ............................................................................................................................................. 25

JTAG......................................................................................................................................................... 26

MICROPROCESSOR INTERFACE.................................................................................................................... 27

POWER SUPPLY PINS ................................................................................................................................. 30

GROUND PINS ............................................................................................................................................ 30

NO CONNECT PINS ..................................................................................................................................... 31

ELECTRICAL CHARACTERISTICS................................................................................................................... 32

ABSOLUTE MAXIMUMS ................................................................................................................................ 32

DC ELECTRICAL CHARACTERISTICS............................................................................................................. 32

TABLE 2: XRT84L38 POWER CONSUMPTION ................................................................................................................................. 32

1.0 MICROPROCESSOR INTERFACE BLOCK ......................................................................................... 33

TABLE 3: µC/µP SELECTION TABLE ................................................................................................................................................ 33

1.1 CHANNEL SELECTION WITHIN THE FRAMER .............................................................................................. 34

TABLE 4: CHANNEL SELECTION ...................................................................................................................................................... 34

FIGURE 3. SIMPLIFIED BLOCK DIAGRAM OF THE MICROPROCESSOR INTERFACE BLOCK.................................................................... 35

1.2 THE MICROPROCESSOR INTERFACE BLOCK SIGNAL .............................................................................. 35

TABLE 5: XRT84L38 MICROPROCESSOR INTERFACE SIGNALS THAT EXHIBIT CONSTANT ROLES IN BOTH THE INTEL AND MOTOROLA MODES

35

TABLE 6: INTEL MODE: MICROPROCESSOR INTERFACE SIGNALS ...................................................................................................... 36

TABLE 7: MOTOROLA MODE: MICROPROCESSOR INTERFACE SIGNALS ............................................................................................. 36

1.3 INTERFACING THE XRT84L38 TO THE LOCAL µC/µP VIA THE MICROPROCESSOR INTERFACE BLOCK 36

1.3.1 INTERFACING THE FRAMER TO THE MICROPROCESSOR OVER AN 8 BIT WIDE BI-DIRECTIONAL DATA BUS 37

1.3.2 DATA ACCESS MODES............................................................................................................................................... 37

1.3.2.1 PROGRAMMED I/O ................................................................................................................................................ 37

1.3.2.2 DATA ACCESS USING PROGRAMMED I/O ............................................................................................................... 37

FIGURE 4. INTEL µP INTERFACE SIGNALS DURING PROGRAMMED I/O READ OPERATION ................................................................... 38

FIGURE 5. INTEL µP INTERFACE SIGNALS DURING PROGRAMMED I/O WRITE OPERATION ................................................................. 39

FIGURE 6. MOTOROLA µP INTERFACE SIGNALS DURING A PROGRAMMED I/O READ OPERATION ....................................................... 40

FIGURE 7. MOTOROLA µP INTERFACE SIGNAL DURING PROGRAMMED I/O WRITE OPERATION........................................................... 41

1.3.2.3 BURST MODE I/O FOR DATA ACCESS ................................................................................................................... 41

FIGURE 8. INTEL µP INTERFACE SIGNALS, DURING THE INITIAL READ OPERATION OF A BURST CYCLE .............................................. 43

FIGURE 9. INTEL µP INTERFACE SIGNALS, DURING SUBSEQUENT READ OPERATIONS OF A BURST I/O CYCLE ................................... 44

FIGURE 10. INTEL µP INTERFACE SIGNALS, DURING THE INITIAL WRITE OPERATION OF A BURST CYCLE ........................................... 46

FIGURE 11. µP INTERFACE SIGNALS, DURING SUBSEQUENT WRITE OPERATIONS OF A BURST I/O CYCLE ......................................... 47

FIGURE 12. MOTOROLA µP INTERFACE SIGNALS DURING THE INITIAL READ OPERATION OF A BURST CYCLE .................................... 48

FIGURE 13. MOTOROLA µP INTERFACE SIGNALS, DURING SUBSEQUENT READ OPERATIONS OF A BURST I/O CYCLE ........................ 49

FIGURE 14. MOTOROLA µP INTERFACE SIGNALS, DURING THE INITIAL WRITE OPERATION OF A BURST CYCLE .................................. 51

FIGURE 15. MOTOROLA µP INTERFACE SIGNALS DURING SUBSEQUENT WRITE OPERATIONS OF A BURST I/O CYCLE ........................ 52

1.4 DMA READ/WRITE OPERATIONS................................................................................................................... 52

DMA-0 Write DMA Interface ..................................................................................................................................... 53

FIGURE 16. DMA MODE FOR THE XRT84L38 AND A MICROPROCESSOR......................................................................................... 53

1.5 MEMORY AND REGISTER MAP ...................................................................................................................... 53

1.5.1 MEMORY MAPPED I/O INDIRECT ADDRESSING...................................................................................................... 53

I

5 Page

XRT84L38

REV. 1.0.1

OCTAL T1/E1/J1 FRAMER

THIRD OCTET OF 16.384MBIT/S DATA STREAM ......................................................................................... 272

FIFTH OCTET OF 16.384MBIT/S DATA STREAM.......................................................................................... 272

SEVENTH OCTET OF 16.384MBIT/S DATA STREAM .................................................................................... 273

SECOND OCTET OF 16.384MBIT/S DATA STREAM...................................................................................... 273

FOURTH OCTET OF 16.384MBIT/S DATA STREAM ...................................................................................... 273

SIXTH OCTET OF 16.384MBIT/S DATA STREAM ......................................................................................... 273

EIGHTH OCTET OF 16.384MBIT/S DATA STREAM ....................................................................................... 273

FIGURE 79. INTERFACING XRT84L38 TO LOCAL TERMINAL EQUIPMENT USING 16.384MBIT/S DATA BUS ......................................... 274

FIGURE 80. TIMING SIGNAL WHEN THE FRAMER IS RUNNING AT H.100 16.384MBIT/S MODE ........................................................... 275

6.2 THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK................................................................. 275

6.2.1 DESCRIPTION OF THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK............................................. 275

RECEIVE INTERFACE CONTROL REGISTER (RICR) (INDIRECT ADDRESS = 0XN0H, 0X22H) ........................ 276

6.2.2 BRIEF DISCUSSION OF THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK OPERATING AT XRT84V24

COMPATIBLE 2.048MBIT/S MODE ............................................................................................................................ 276

SLIP BUFFER CONTROL REGISTER (SBCR) (INDIRECT ADDRESS = 0XN0H, 0X16H) ................................... 276

SLIP BUFFER CONTROL REGISTER (SBCR) (INDIRECT ADDRESS = 0XN0H, 0X16H) ................................... 277

RECEIVE INTERFACE CONTROL REGISTER (RICR) (INDIRECT ADDRESS = 0XN0H, 0X22H) ........................ 278

6.2.2.1 CONNECT THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK TO THE LOCAL TERMINAL EQUIPMENT IF THE SLIP

BUFFER IS BYPASSED ............................................................................................................................................. 279

FIGURE 81. INTERFACING XRT84L38 TO LOCAL TERMINAL EQUIPMENT WITH SLIP BUFFER BYPASSED AND RECOVERED RECEIVE LINE CLOCK

AS RECEIVE TIMING SOURCE......................................................................................................................................... 280

FIGURE 82. WAVEFORMS OF THE SIGNALS CONNECTING THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK TO THE LOCAL TERMINAL

EQUIPMENT WHEN THE SLIP BUFFER IS BYPASSED AND THE RECOVERED LINE CLOCK IS THE TIMING SOURCE OF THE RECEIVE

SECTION ..................................................................................................................................................................... 281

6.2.2.2 CONNECT THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK TO THE LOCAL TERMINAL EQUIPMENT IF THE SLIP

BUFFER IS ENABLED ............................................................................................................................................... 281

SLIP BUFFER STATUS REGISTER (SBSR) (INDIRECT ADDRESS = 0XNAH, 0X08H)...................................... 282

FIGURE 83. INTERFACING XRT84L38 TO LOCAL TERMINAL EQUIPMENT WITH SLIP BUFFER ENABLED OR ACTS AS FIFO..................... 283

FIGURE 84. WAVEFORMS OF THE SIGNALS THAT CONNECT THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK TO THE LOCAL TERMI-

NAL EQUIPMENT WHEN THE SLIP BUFFER IS ENABLED................................................................................................... 284

6.2.2.3 CONNECT THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK TO THE LOCAL TERMINAL EQUIPMENT IF THE SLIP

BUFFER IS CONFIGURED AS FIFO ........................................................................................................................... 284

FIFO LATENCY REGISTER (FIFOL) (INDIRECT ADDRESS = 0XN0H, 0X17H) .............................................. 284

FIGURE 85. INTERFACING XRT84L38 TO LOCAL TERMINAL EQUIPMENT WITH SLIP BUFFER ENABLED OR ACTS AS FIFO..................... 285

FIGURE 86. WAVEFORMS OF THE SIGNALS THAT CONNECT THE RECEIVE PAYLOAD DATA OUTPUT INTERFACE BLOCK TO THE LOCAL TERMI-

NAL EQUIPMENT WHEN THE SLIP BUFFER IS ACTED AS FIFO......................................................................................... 286

6.2.3 HIGH SPEED RECEIVE BACK-PLANE INTERFACE................................................................................................ 286

RECEIVE INTERFACE CONTROL REGISTER (RICR) (INDIRECT ADDRESS = 0XN0H, 0X22H) ........................ 286

RECEIVE MULTIPLEX ENABLE BIT = 0 ........................................................................................................ 287

RECEIVE MULTIPLEX ENABLE BIT = 1 ........................................................................................................ 288

RECEIVE INTERFACE CONTROL REGISTER (RICR) (INDIRECT ADDRESS = 0XN0H, 0X22H) ......................... 288

6.2.3.1 E1 RECEIVE INPUT INTERFACE - MVIP 2.048 MHZ ............................................................................................. 288

FIGURE 87. INTERFACING XRT84L38 TO LOCAL TERMINAL EQUIPMENT USING MVIP 2.048MBIT/S DATA BUS.................................. 289

FIGURE 88. TIMING DIAGRAM OF INPUT SIGNALS TO THE FRAMER WHEN RUNNING AT MVIP 2.048MBIT/S ...................................... 289

6.2.3.2 E1 RECEIVE INPUT INTERFACE - 4.096 MHZ ....................................................................................................... 290

FIGURE 89. INTERFACING XRT84L38 TO LOCAL TERMINAL EQUIPMENT USING 4.096MBIT/S DATA BUS ........................................... 290

FIGURE 90. TIMING DIAGRAM OF INPUT SIGNALS TO THE FRAMER WHEN RUNNING AT 4.096MBIT/S MODE ....................................... 291

6.2.3.3 E1 RECEIVE INPUT INTERFACE - 8.192 MHZ ....................................................................................................... 291

FIGURE 91. INTERFACING XRT84L38 TO LOCAL TERMINAL EQUIPMENT USING 8.192MBIT/S DATA BUS ........................................... 292

FIGURE 92. TIMING DIAGRAM OF INPUT SIGNALS TO THE FRAMER WHEN RUNNING AT 8.192MBIT/S MODE........................................ 292

6.2.3.4 E1 RECEIVE INPUT INTERFACE - BIT-MULTIPLEXED 16.384MBIT/S....................................................................... 292

FIRST OCTET OF 16.384MBIT/S DATA STREAM.......................................................................................... 293

SECOND OCTET OF 16.384MBIT/S DATA STREAM...................................................................................... 293

FIFTH OCTET OF 16.384MBIT/S DATA STREAM.......................................................................................... 294

SIXTH OCTET OF 16.384MBIT/S DATA STREAM ......................................................................................... 294

SEVENTH OCTET OF 16.384MBIT/S DATA STREAM .................................................................................... 294

EIGHTH OCTET OF 16.384MBIT/S DATA STREAM ....................................................................................... 294

FIGURE 93. INTERFACING XRT84L38 TO LOCAL TERMINAL EQUIPMENT USING 16.384 MBIT/S DATA BUS ........................................ 295

FIGURE 94. TIMING SIGNAL WHEN THE FRAMER IS RUNNING AT BIT-MULTIPLEXED 16.384MBIT/S MODE .......................................... 295

6.2.3.5 E1 RECEIVE INPUT INTERFACE - HMVIP 16.384MBIT/S....................................................................................... 295

FIRST OCTET OF 16.384MBIT/S DATA STREAM.......................................................................................... 296

VII

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet XRT84L38.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XRT84L38 | OCTAL T1/E1/J1 FRAMER | Exar Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |