|

|

PDF XRK4993 Data sheet ( Hoja de datos )

| Número de pieza | XRK4993 | |

| Descripción | 3.3V PROGRAMMABLE SKEW CLOCK BUFFER | |

| Fabricantes | Exar Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XRK4993 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

XRK4993

3.3V PROGRAMMABLE SKEW CLOCK BUFFER

FEBRUARY 2007

REV. 1.0.0

FUNCTIONAL DESCRIPTION

The XRK4993 is a 3.3V High-Speed Low-Voltage

Programmable Skew Clock Buffer. It is intended for

high-performance computer systems and offers user

selectable control over system clock functions to

optimize timing. Eight ouputs, arranged in four

banks, can each drive 75Ω terminated transmission

lines while delivering minimal and specified output

skews and full-swing Low Voltage TTL logic levels.

Banks A, B, C (two outputs per bank) can be

individually selected for one of nine delay or function

configurations through two dedicated three-level

inputs. These outputs are able to lead or lag the

CLKIN input reference clock by up to 6 time units

from their nominal "zero" skew position. The

integrated PLL allows external load and transmission

line delay effects to be canceled achieving zero delay

capability. Combining the zero delay capability with

the selectable output skew functions, output-to-output

delays of up to +12 time units can be created.

The XRK4993’s divide functions (divide-by-two and

divide-by-four) allow distribution of a low-frequency

clock that can be multiplied by two or four at the clock

destination. This feature facilitates clock distribution

while allowing maximum system clock flexibility.

When the OE pin is held low, all the outputs are

synchronously enabled. However, if OE is held high,

all the outputs except QC0 and QC1 are

synchronously disabled.

When PE is held high, all the outputs are

synchronized with the positive edge of the CLKIN

clock input. When PE is held low, all the outputs are

synchronized with the negative edge of CLKIN. The

device has LVTTL outputs with 12mA balanced drive.

FEATURES

• 3 pairs of programmable skew outputs

• Low skew: 200ps same pair, 250ps all outputs

• Selectable positive or negative edge

synchronization: Excellent for DSP applications

• Synchronous output enable

• Output frequency: 3.75MHz to 85MHz

• 2x, 4x, 1/2, and 1/4 output frequencies

• 3 skew grades

• 3-level inputs for skew and PLL range control

• PLL bypass mode

• External feedback, internal loop filter

• 12mA balanced drive outputs

• Available in 28 pin QSOP package

• Jitter < 200 ps peak-to-peak

• CLKIN input is 5V tolerant

FIGURE 1. BLOCK DIAGRAM OF THE XRK4993

CLKIN

FB_IN

PE

FSEL*

PLL_BYPASS*

SELA[1:0]*

SELB[1:0]*

SELC[1:0]*

Ref

PLL

Feedback

2

2

2

OE

* Three-level inputs

H

M

L

Bank “SKEW”

Control

QA0

QA1

QB0

QB1

QC0

QC1

QD0

QD1

Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

1 page

XRK4993

REV. 1.0.0

3.3V PROGRAMMABLE SKEW CLOCK BUFFER

In the PLL_BYPASS mode the PE input can be used to invert the outputs. Thus, for a 20% (High) duty cycle

input, all outputs will retain the 20% high condition with PE High. For PE Low, however, they will be 80% High.

PE does not effect the duty cycle of the divided outputs.

TABLE 3: TYPICAL PROPAGATION DELAY WITH ZERO SKEW SETTING

PLL_BYPASS INPUT

FSEL INPUT

TOTAL PROPAGATION DELAY

Mid

Low or Mid

52nS

High

29nS

High

Low or Mid

12nS

High

10nS

SPECIAL FUNCTIONS

The following special functions have been implemented in the chip.

PE pin:

• In Normal operation, PE controls the "alignment" edge of the CLKIN and the FB-IN signals. (All other output signals are

aligned to the Feedback). PE=Low, aligns the FB_IN faliing edge to the CLKIN falling edge. PE=High, aligns rising

edges.

• In the "disabled output mode (see below), the disabled state is forced to the opposite state of PE. This keeps the off

condition in a low-noise state.

• In PLL_BYPASS mode, PE controls the duty cycle (inversion) of the outputs (see PLL_BYPASS mode above).

OE pin:

• In Normal mode, OE is used to disable all outputs except QC[1,0]. These are maintained to provide PLL Feedback to

keep frequency lock. OE is kept low to enable the outputs and High to disable them. This is a synchronized operation to

prevent "partial" clocks When OE goes high, the outputs will go to their disabled level at the end of the next active clock

cycle. The level is determined by the state of PE. If PE is high, the output will go low at the end of the cycle and remain

there until OE return to a low state. If PE is low, at the end of the next clock high state it will continue to remain high until

OE returns low.

• If OE is high when PLL_BYPASS is at the Mid level, the PLL is enabled to provide an individual bank output control. In

this mode, taking both SEL(x)1 & 0 to the Low state will disable that bank's outputs.

FIGURE 3. TYPICAL OUTPUTS WITH FB_IN CONNECTED TO A ZERO-SKEW OUTPUT

SELA[1:0]

SELB[1:0]

(N/A)

LL

LM

LH

ML

MM

MH

HL

HM

HH

(N/A)

(N/A)

FB_IN

CLKIN

SELC[1:0]

LM

LH

(N/A)

ML

(N/A)

MM

(N/A)

MH

(N/A)

HL

HM

-6tU

-4tU

-3tU

-2tU

-1tU

0tU

+1tU

+2tU

+3tU

+4tU

+6tU

LL/HH DIVIDED

5

5 Page

REV. 1.0.0

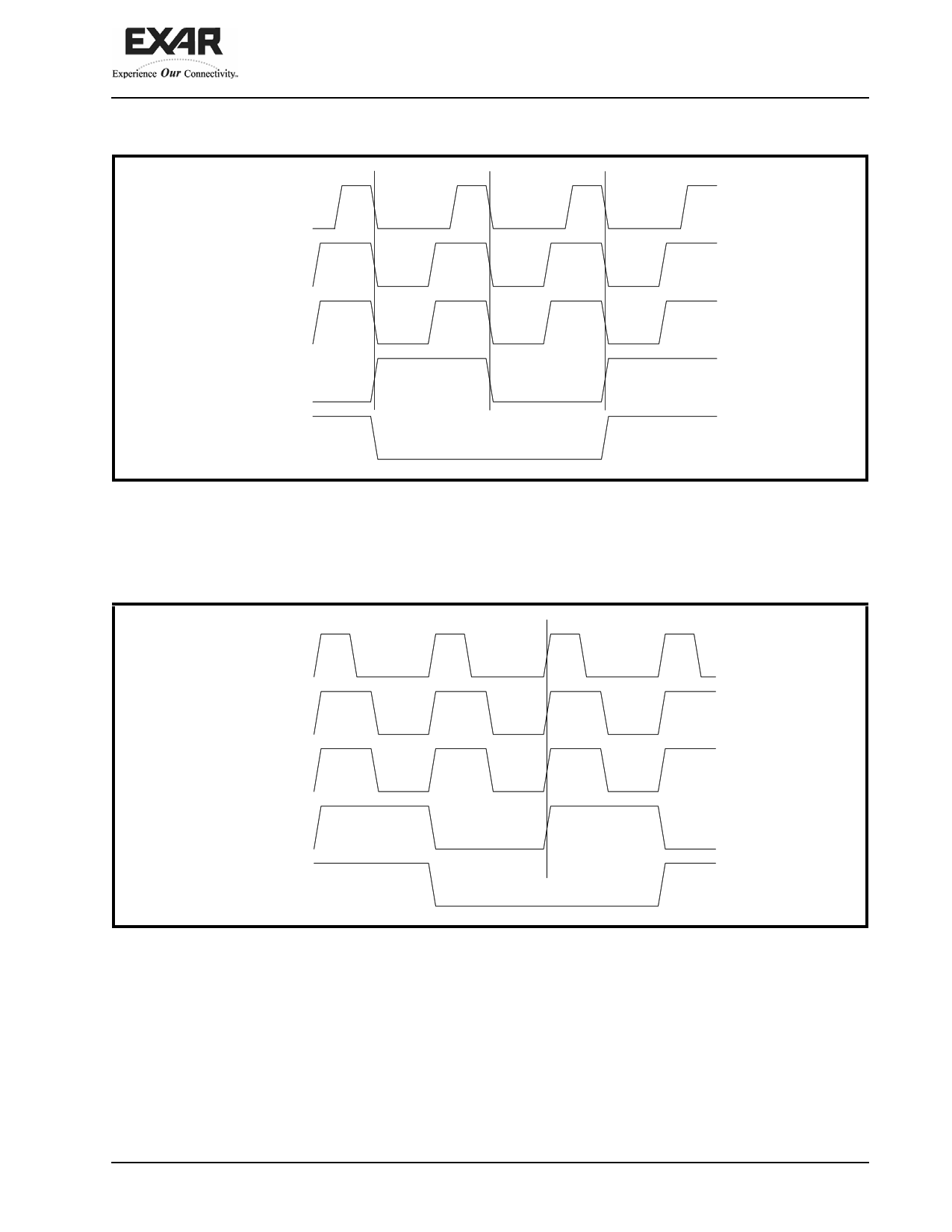

FIGURE 7. TIMING DIAGRAM PE=LOW

XRK4993

3.3V PROGRAMMABLE SKEW CLOCK BUFFER

Clkin

FB_In

Qxn

QC div2

QC div4

PE = LOW TIMING:

All output changes occur on the falling edge of the Clkin reference signal. Programmable skews are made

relative to this edge.

FIGURE 8. TIMING DIAGRAM PE=HIGH

Clkin

FB_In

Qxn

QC div2

QC div4

PE=HIGH TIMING:

When the PE pin is High, all changes begin relative to the rising edge of the Clkin reference signal. This

includes not only the "zero tu" signals but also the divided output signals. The divided-by-two outputs will

change on each rising edge. As QD can only be 0tu, QC is the only "divide by" output providing either divide-

by- two or divide-by-four, not both.

11

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet XRK4993.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XRK4991 | SKEW CLOCK BUFFER | Exar Corporation |

| XRK49911 | SKEW CLOCK BUFFER | Exar Corporation |

| XRK4991A | SKEW CLOCK BUFFER | Exar Corporation |

| XRK4993 | 3.3V PROGRAMMABLE SKEW CLOCK BUFFER | Exar Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |