|

|

PDF XRT83D10 Data sheet ( Hoja de datos )

| Número de pieza | XRT83D10 | |

| Descripción | SINGLE CHANNEL DS1/CEPT LINE INTERFACE UNIT | |

| Fabricantes | Exar Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XRT83D10 (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

xrwww.DataSheet4U.com

XRT83D10

JULY 2004

SINGLE CHANNEL DS1/CEPT LINE INTERFACE UNIT

REV. 1.0.3

GENERAL DESCRIPTION

The XRT83D10 is a fully integrated, single channel,

Line Interface Unit (Transceiver) for 75 Ω or 120 Ω E1

(2.048 Mbps) and 100Ω DS1 (1.544 Mbps)

applications. The LIU consists of a receiver with

adaptive data slicer for accurate data and clock

recovery and a transmitter which accepts dual-rail

digital inputs for signal transmission to the line using

a low- impedance differential line driver. The LIU also

includes a crystal-less jitter attenuator for clock and

data smoothing which, depending on system

requirements, can be selected in either the transmit

or receive path.

The XRT83D10 uses the transformer coupling on

both the Receiver and Transmitter sides, and

supports both 120Ω balanced,75Ω unbalanced and

100Ω interfaces.

FEATURES

• Complete E1 (CEPT) and DS1 Line Interface Unit

• Generates transmit output pulses that are compli-

ant with the ITU-T G.703 Pulse Template for

2.048Mbps (E1) rates

• On-Chip Pulse Shaping for both 75 Ω ,120 Ω and

100 Ω Line Drivers

• Clock Recovery and Selectable Crystal-less Jitter

attenuator

• Compliant with ETS300166 Return Loss

• Compliant with the ITU-T G.823 Jitter Tolerance

Requirements

• Remote, Local and Digital Loop backs

• Declares and Clears LOS per ITU-T G.775

• -40°C to 85°C Temperature Range

• Low Power Dissipation

• +5V or +3.3V Supply Operation

• Pin Compatible with AGERE T7290A and T5290A

APPLICATIONS

• PDH Multiplexers

• SDH Multiplexers

• Digital Cross-Connect Systems

• DECT (Digital European Cordless Telephone) Base

Stations

• CSU/DSU Equipment

FIGURE 1. BLOCK DIAGRAM OF THE XRT83D10

RTIP

R e ceiv e

D ata

RRING

Peak

D e te cto r

D a ta

Slicer

ALOS

Data &

Tim ing

Recovery

EXCLK

Tim ing

G e n e ra to r

DLOS

DLOS

MODE1

MODE2

2

2

Jitter

Attenuator

2

Local

Loopback

LP1

2

D ig ita l

Loopback

LP3

2

SCLK

TTIP

T ransm it

D a ta

TRING

Tx Line

D riv e r

Transm it

Monitor

TSC

Pulse

Equalizer

2

Loss of

C lo c k

TAOS

ICT CLKLOS JA

C lo c k

2

R e m o te

2 Looback

LP2

TAOS

MODE2

EXCLK

Local

R em ote

D ig ita l

TAOS

EC1

EC2

EC3

MODE1

MODE2

Decode

2

EXCLK

µP

Interface

4

RLOS

RPDATA

RNDATA

RCLK

FOFS

TPDATA

TNDATA

TCLK

EXCLK

TAOS

EC1

EC2

EC3

MODE1

MODE2

LOOPA

LOOPB

CS

VDDA, GNDA

VDDD, GNDD

Exar Corporation 48720 Kato Road, Fremont CA, 94538 • (510) 668-7000 • FAX (510) 668-7017 • www.exar.com

1 page

xr

SINGLE CHANNEL DS1/CEPT LINE INTERFACE UNIT

XRT83D10

REV. 1.0.3

CONTROL FUNCTION

PIN #

NAME

2 ICT

16 ExCLK

11 TAOS

9 LOOPB

10 LOOPA

13 FOFS

TYPE

I

I

I

I

DESCRIPTION

In Circuit Testing

When this pin is tied "Low" all output pins are forced to high-impedance state

for in-circuit testing.

NOTE: Internally pulled up.

External Clock Input:

DS1 (1.544 MHz ± 130 ppm) or CEPT E1 (2.048 MHz ± 80 ppm) clock signal is

provided. ExCLK must be an independent clock to guarantee device perfor-

mance for all specifications. This clock must be continuously active (ungapped

or unswitched) and void of jitter for the device to operate properly.

Transmit All Ones:

With this pin tied "High", an AMI encoded all "1’s" signal sent to the transmit

output using ExCLK as the timing reference. A remote loop back has higher

priority over TAOS request.

NOTE: Internally pulled down.

Loopback control.

LOOPB along with LOOPA is used for selecting different loopbacks.

LOOPA

0

0

1

1

LOOPB

0

1

0

1

Loopback Mode

Normal Operation

Digital

Remote

Local

NOTE: Internally Pulled down.

I Loopback control.

LOOPB along with LOOPA is used for selecting different loopbacks.

NOTE: Internally Pulled down.

O FIFO Overflow Signal:

This pin is set "High" if the phase jitter of the incoming signal exceeds the toler-

ance of the jitter attenuator’s buffer. This may result in loss of data and Jitter

Attenuator is no longer attenuating jitter.

POWER AND GROUND

PIN #

3

NAME

AVDD

4 AGND

24 DVDD

26 DGND

TYPE

****

****

****

****

DESCRIPTION

Analog Supply: 5V ± 5% or 3.3V ± 5%

Analog GND.

Digital Supply: 5V ± 5% or 3.3V ± 5%

Digital GND

5

5 Page

xr

XRT83D10

SINGLE CHANNEL DS1/CEPT LINE INTERFACE UNIT

REV. 1.0.3

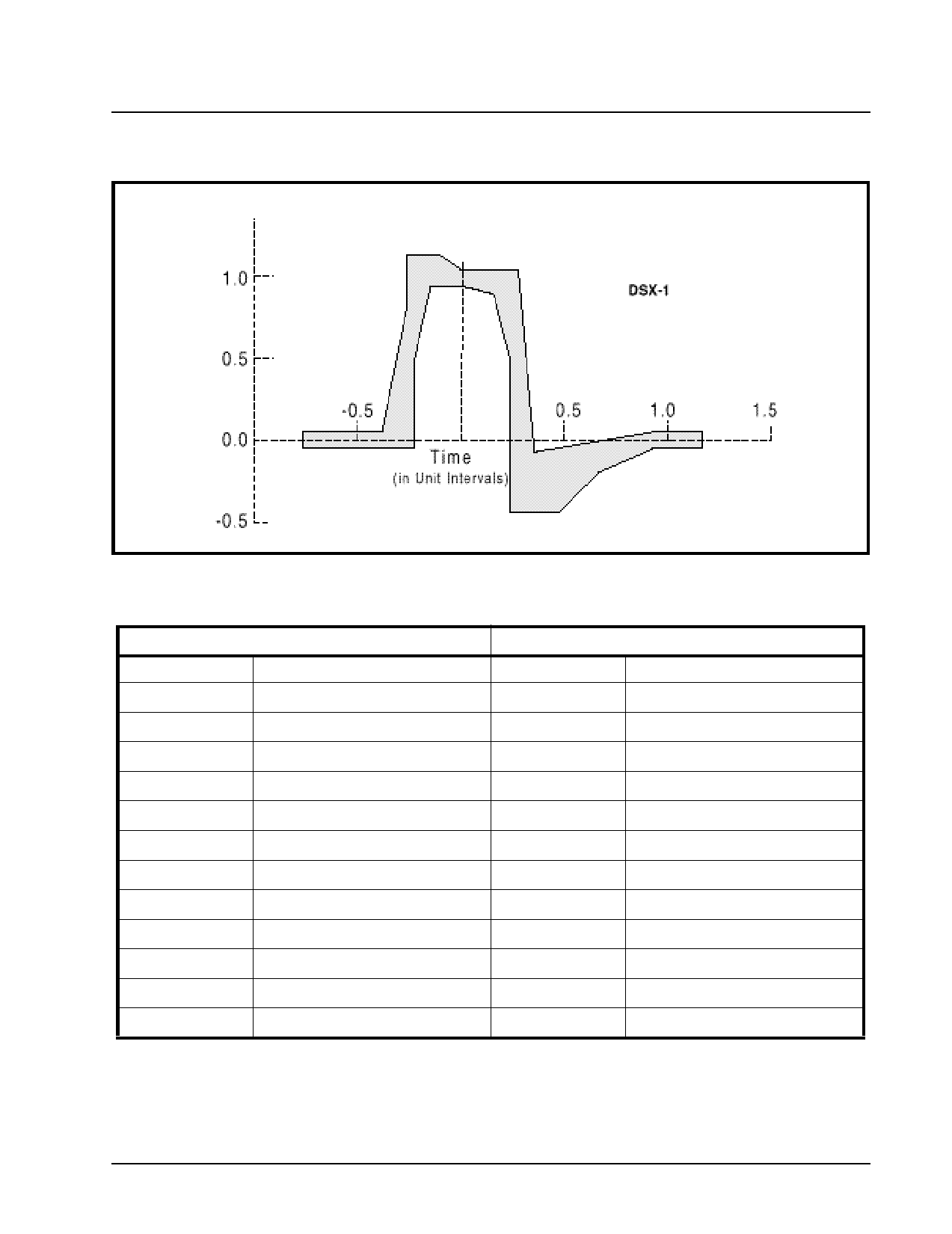

FIGURE 6. DSX-1 PULSE TEMPLATE (NORMALIZED AMPLITUDE)

TABLE 7: DSX1 INTERFACE ISOLATED PULSE MASK PER ANSI T1.102-1993 AND CORNER POINT SPECIFICATIONS

MINIMUM CURVE

MAXIMUM CURVE

TIME (UI)

-0.77

NORMALIZED AMPLITUDE (V)

-0.05

TIME (UI)

-0.77

NORMALIZED AMPLITUDE (V)

0.05

-0.23

-0.05

-0.39

0.05

-0.23 0.5 -0.27 0.8

-0.15 0.95 -0.27 1.15

0.0 0.95 -0.12 1.15

0.15 0.9

0.0 1.05

0.23 0.5 0.27 1.05

0.23 -0.45 0.35 -0.07

0.46 -0.45 0.93 0.05

0.66 -0.2 1.16 0.05

0.93 -0.05

1.16 -0.05

11

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet XRT83D10.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XRT83D10 | SINGLE CHANNEL DS1/CEPT LINE INTERFACE UNIT | Exar Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |