|

|

PDF ICS81006 Data sheet ( Hoja de datos )

| Número de pieza | ICS81006 | |

| Descripción | VCXO-TO-6 LVCMOS OUTPUTS | |

| Fabricantes | ICS | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS81006 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

Integrated

Circuit

Systems, Inc.

ICS81006

VCXO-TO-6 LVCMOS OUTPUTS

GENERAL DESCRIPTION

The ICS81006 is a high performance, low

ICS j i t t e r / l o w p h a s e n o i s e V C X O a n d i s a

HiPerClockS™ member of the HiPerClockS™ family of high

performance clock solutions from ICS. The

ICS81006 works in conjunction with a

pullable crystal to generate an output clock over the

range of 12MHz - 40MHz and has 6 LVCMOS outputs,

effectively integrating a fanout buffer function.

The frequency of the VCXO is adjusted by the VC control

voltage input. The output range is ±100ppm around the

nominal crystal frequency. The VC control voltage range

is 0 - V . The device is packaged in a small 4mm x 4mm

DD

VFQFN package and is ideal for use on space

constrained boards typically encountered in ADSL/

VDSL applications.

FEATURES

• Six LVCMOS/LVTTL outputs, 20Ω nominal

output impedance

• Output Q5 can be selected for ÷1 or ÷2 frequency relative

to the crystal frequency

• Output frequency range: 12MHz to 40MHz

• Crystal pull range: ± 90ppm (typical)

• Synchronous output enable places outputs in High-Z state

• On-chip filter on VIN to suppress noise modulation of VCXO

• VDD/VDDO combinations

3.3V/3.3V

3.3V/2.5V

3.3V/1.8V

2.5V/2.5V

2.5V/1.8V

• 4mm x 4mm 20 Lead VFQFN package is ideal for space

constrained designs

• 0°C to 70°C ambient operating temperature

• Available in both standard and lead-free RoHS compliant

packages

BLOCK DIAGRAM

OE0 (Pullup)

VC LP Filter

SYNC

XTAL_IN

XTAL_OUT

VCXO

DIV_SEL_Q5 (Pulldown)

0: ÷1

1: ÷2

PIN ASSIGNMENT

Q0 20 19 18 17 16

XTAL_IN 1

15 GND

XTAL_OUT 2

14 Q2

Q1

VDD 3

1 3 VDDO

VC 4

12 Q3

Q2

DIV_SEL_Q5 5

11 GND

6 7 8 9 10

Q3

ICS81006

20-Lead VFQFN

Q4 4mm x 4mm x 0.95 package body

K Package

Top View

Q5

OE1 (Pullup)

SYNC

81006AK

www.icst.com/products/hiperclocks.html

1

REV. A JANUARY 4, 2006

1 page

Integrated

Circuit

Systems, Inc.

ICS81006

VCXO-TO-6 LVCMOS OUTPUTS

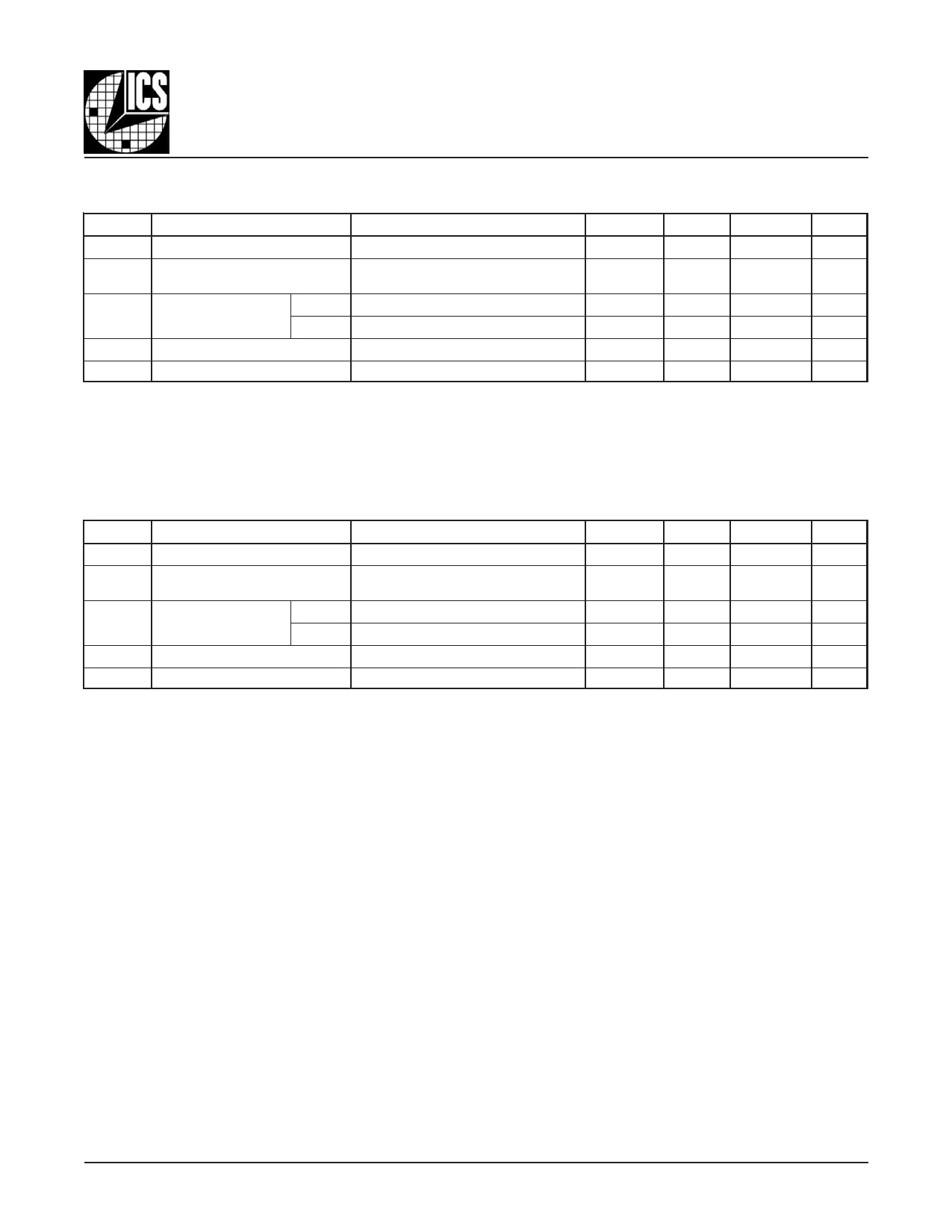

TABLE 4D. AC CHARACTERISTICS, VDD = VDDO = 2.5V±5%, TA = 0°C TO 70°C

Symbol Parameter

Test Conditions

Minimum Typical Maximum

fOUT

tjit(Ø)

Output Frequency

RMS Phase Jitter (Random);

NOTE 1

Integration Range: 1kHz-1MHz

12 19.44 40

0.28

tsk(o)

Output Skew;

NOTE 2, 3

Q0:Q4

Q0:Q5

DIV_SEL_Q5 = ÷1

25

100

tR / tF

odc

Output Rise/Fall Time

Output Duty Cycle

20% to 80%

300

45

NOTE 1: Please refer to the Phase Noise Plot.

NOTE 2: Defined as skew between outputs at the same supply voltage and with equal load conditions.

Measured at the output differential cross points.

NOTE 3: This parameter is defined in accordance with JEDEC Standard 65.

800

55

Units

MHz

ps

ps

ps

ps

%

TABLE 4E. AC CHARACTERISTICS, VDD = 2.5V±5%, VDDO = 1.8V±0.2V, TA = 0°C TO 70°C

Symbol Parameter

Test Conditions

Minimum Typical Maximum

fOUT

tjit(Ø)

tsk(o)

Output Frequency

RMS Phase Jitter (Random);

NOTE 1

Output Skew;

NOTE 2, 3

Q0:Q4

Q0:Q5

Integration Range: 1kHz-1MHz

DIV_SEL_Q5 = ÷1

12 19.44 40

0.26

40

175

tR / tF

odc

Output Rise/Fall Time

Output Duty Cycle

20% to 80%

450

40

NOTE 1: Please refer to the Phase Noise Plot.

NOTE 2: Defined as skew between outputs at the same supply voltage and with equal load conditions.

Measured at the output differential cross points.

NOTE 3: This parameter is defined in accordance with JEDEC Standard 65.

1400

60

Units

MHz

ps

ps

ps

ps

%

81006AK

www.icst.com/products/hiperclocks.html

5

REV. A JANUARY 4, 2006

5 Page

Integrated

Circuit

Systems, Inc.

ICS81006

VCXO-TO-6 LVCMOS OUTPUTS

RECOMMENDATIONS FOR UNUSED INPUT AND OUTPUT PINS

INPUTS:

OUTPUTS:

CONTROL PINS:

All control pins have internal pull-ups or pull-downs; additional

resistance is not required but can be added for additional

protection. A 1kΩ resistor can be used. The VC pin can not be

floated.

LVCMOS OUTPUT:

All unused LVCMOS output can be left floating. We

recommend that there is no trace attached.

SCHEMATIC EXAMPLE

Figure 2 shows an example of ICS81006 application sche-

matic. The decoupling capacitors should be located as close

as possible to the power pin. For the LVCMOS 20Ω output

drivers, series termination example is shown in the sche-

matic. Additional termination approaches are shown in the

LVCMOS Termination Application Note.

Quartz crystal should be

placed as close to the

device as possible.

C1

SPARE

VDD

Pull-up VDD

example

R4

1K

U1

VDDO

R1

30

Zo = 50

XTAL

C2

SPARE

VC = 0V to VDD

VC

1

2 XTAL_IN

3

4

5

XTAL_OUT

VDD

VC

DIV_SEL_Q5

Pull-down

example

81006

R3

1K

VDD

R5 1K

GND

Q2

VDDO

Q3

GND

15

14

13

12

11

R2

Zo = 50

30

(U1-3)

VDD

C7

10uf

C6

0.1uF

(U1-9) (U1-13) (U1-17)

VDDO

C5

0.1uF

C4

0.1uF

C3

0.1uF

Unused outputs can be left floating. There should be

no trace attached to unused outputs. Device

characterized and specification limits set with all

outputs terminated.

FIGURE 2. ICS81006 SCHEMATIC EXAMPLE

81006AK

www.icst.com/products/hiperclocks.html

11

REV. A JANUARY 4, 2006

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet ICS81006.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS810001-21 | FEMTOCLOCKS-TM DUAL VCXO VIDEO PLL | ICS |

| ICS81006 | VCXO-TO-6 LVCMOS OUTPUTS | ICS |

| ICS81006I | VCXO-TO-LVCMOS OUTPUTS | IDT |

| ICS81006I | VCXO-TO-6 LVCMOS OUTPUTS | ICS |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |