|

|

PDF 21555 Data sheet ( Hoja de datos )

| Número de pieza | 21555 | |

| Descripción | Non-Transparent PCI-to-PCI Bridge | |

| Fabricantes | Intel Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 21555 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

21555 Non-Transparent PCI-to-

PCI Bridge

Specification Update

December 2002

Notice: The 21555 may contain design defects or errors known as errata. Characterized errata

that may cause the 21555’s behavior to deviate from published specifications are documented in

this specification update.

Order Number: 278337-008

1 page

Revision History

Documentation Changes

Date

12/19/02

6/12/02

4/12/02

6/11/01

6/7/01

5/24/01

9/15/00

2/21/00

Version

Description

The following changes have been made to this document:

• 21555 bridge steppings have changed to A3. Markings have been updated

as well. See “Markings” on page 11.

• Added related document to “Affected Documents/Related Documents” on

page 7.

008 • Status for Errata 1 and 2 are changed to Fixed. See “Errata” on page 9.

• Specification change - 21555 bridge PCI compliancy now at Version 2.3. See

“Specification Changes” on page 9.

• Documentation changes - Data sheet and User Manual include 2.3

compliance information. See “Added Section 3.1.1 PCI Local Bus

Compliance” on page 22. and “Change to Tables 61 and 62 in Section 16.5.2”

on page 22.

007 Added Errata 2.

006 Added Errata 1.

005

Corrected PBGA package description from 2-layer to 4-layer within this

document.

Documentation changes: (See page 9)

004 • Replaced last row of Table 2-3. See Section 14 on Page 21.

• Changed l_stat description in Section 11-5. See Section 15 on Page 22.

Documentation changes: (See page 8)

• Added Markings Table on page 11.

• Insert reference to 21554 for improved accuracy. See Section 3 on Page 16.

• Remove misplaced sections from Chapter 4. See Section 4 on Page 17.

• Remove unnecessary parenthetical phrase. See Section 5 on Page 19.

• Change p_clk and s_clk signal description. See Section 6 on Page 19.

• Remove incorrect sentence from Hot Swap input pin description. See Section

7 on Page 19.

003 • Change or remove three (3) references to the 21554. See Section 8 on Page

19.

• Update D7:D6 byte offset descriptions. See Section 9 on Page 20.

• Remove three references to CLS=4. See Section 10 on Page 20.

• Additional information about JTAG pin termination requirements. See Section

11 on Page 20.

• Emphasize special handling of the JTAG tms signal for Hot insertion

applications.See Section 12 on Page 20.

• Changed Section 12.2.1 and JTAG description. See Section 13 on Page 21.

002

Added specification change to PBGA package dimensions for coplanarity

maximum value.

This new Specification Update document contains:

• One Specification Change that announces coplanarity value changes.

001 Two Documentation changes that:

• Correct the JTAG timing specifications.

• Correct the coplanarity values in the datasheet document.

21555 Non-Transparent PCI-to-PCI Bridge Specification Update

5

5 Page

Identification Information

Documentation Changes

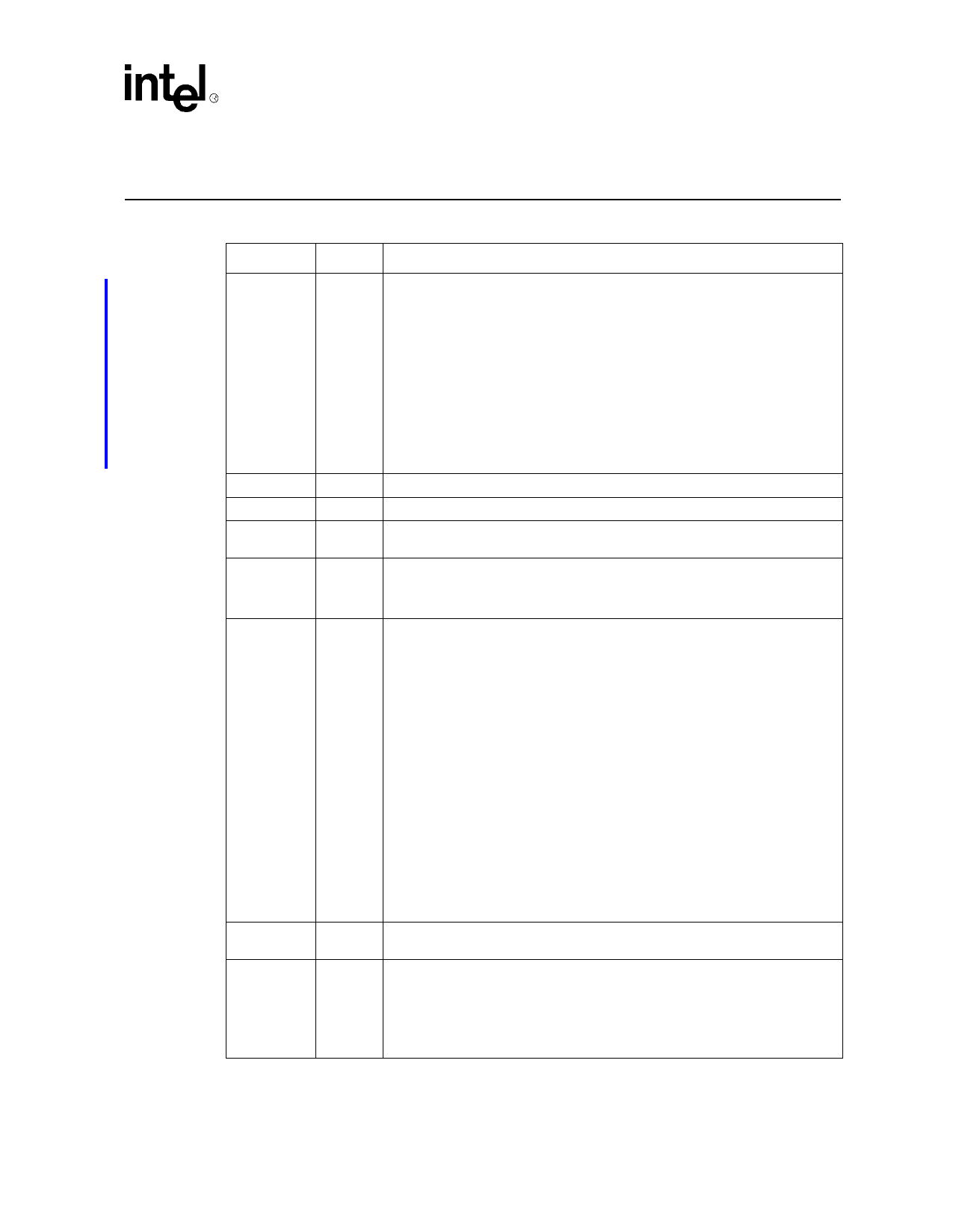

Markings

Package Markings

REV_ID

Register

Value1

Speed (MHz)

Intel FW21555AA

Intel FW21555BA

Intel FW21555AB

Intel FW21555BB

02h 33

02h 66

03h 33

03h 66

1. Identified in a PCI system by reading the value in the REV_ID register.

Stepping

A2

A2

A3

A3

21555 Non-Transparent PCI-to-PCI Bridge Specification Update

11

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet 21555.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 2155 | 2100 System Rack Adaptersand Cabinets | VishaySiliconix |

| 21555 | Non-Transparent PCI-to-PCI Bridge | Intel Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |