|

|

PDF W3EG64128S-BD4 Data sheet ( Hoja de datos )

| Número de pieza | W3EG64128S-BD4 | |

| Descripción | 1GB - 2x64Mx64 DDR SDRAM UNBUFFERED | |

| Fabricantes | White Electronic | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de W3EG64128S-BD4 (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

White Electronic Designs

W3EG64128S-AD4

-BD4

PRELIMINARY*

1GB – 2x64Mx64 DDR SDRAM UNBUFFERED w/PLL

FEATURES

Double-data-rate architecture

Bi-directional data strobes (DQS)

Differential clock inputs (CK & CK#)

Programmable Read Latency 2,2.5 (clock)

Programmable Burst Length (2,4,8)

Programmable Burst type (sequential & interleave)

Edge aligned data output, center aligned data input

Auto and self refresh

Serial presence detect

Dual Rank

Power supply: 2.5V ± 0.2V

JEDEC standard 200 pin SO-DIMM package

• Package height options:

www.DataSheet4U.com

BD4: 31.75 mm (1.25”)

NOTE: Consult factory for availability of:

• RoHS compliant products

• Vendor source control options

• Industrial temperature option

DESCRIPTION

The W3EG64128S is a 2x64Mx64 Double Data Rate

SDRAM memory module based on 512Mb DDR SDRAM

component. The module consists of eight 128Mx8 stack

DDR SDRAMs in 66 pin TSOP packages mounted on a

200 pin FR4 substrate.

Synchronous design allows precise cycle control with the

use of system clock. Data I/O transactions are possible on

both edges and Burst Lengths allow the same device to be

useful for a variety of high bandwidth, high performance

memory system applications.

* This product is under development, is not qualified or characterized and is subject to

change without notice.

Clock Speed

CL-tRCD-tRP

OPERATING FREQUENCIES

DDR333 @CL=2.5

166MHz

2.5-3-3

DDR266 @CL=2

133MHz

2-2-2

DDR266 @CL=2.5

133MHz

2.5-3-3

DDR200 @CL=2

100MHz

2-2-2

May 2004

Rev. 0

1 White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

1 page

White Electronic Designs

W3EG64128S-AD4

-BD4

PRELIMINARY

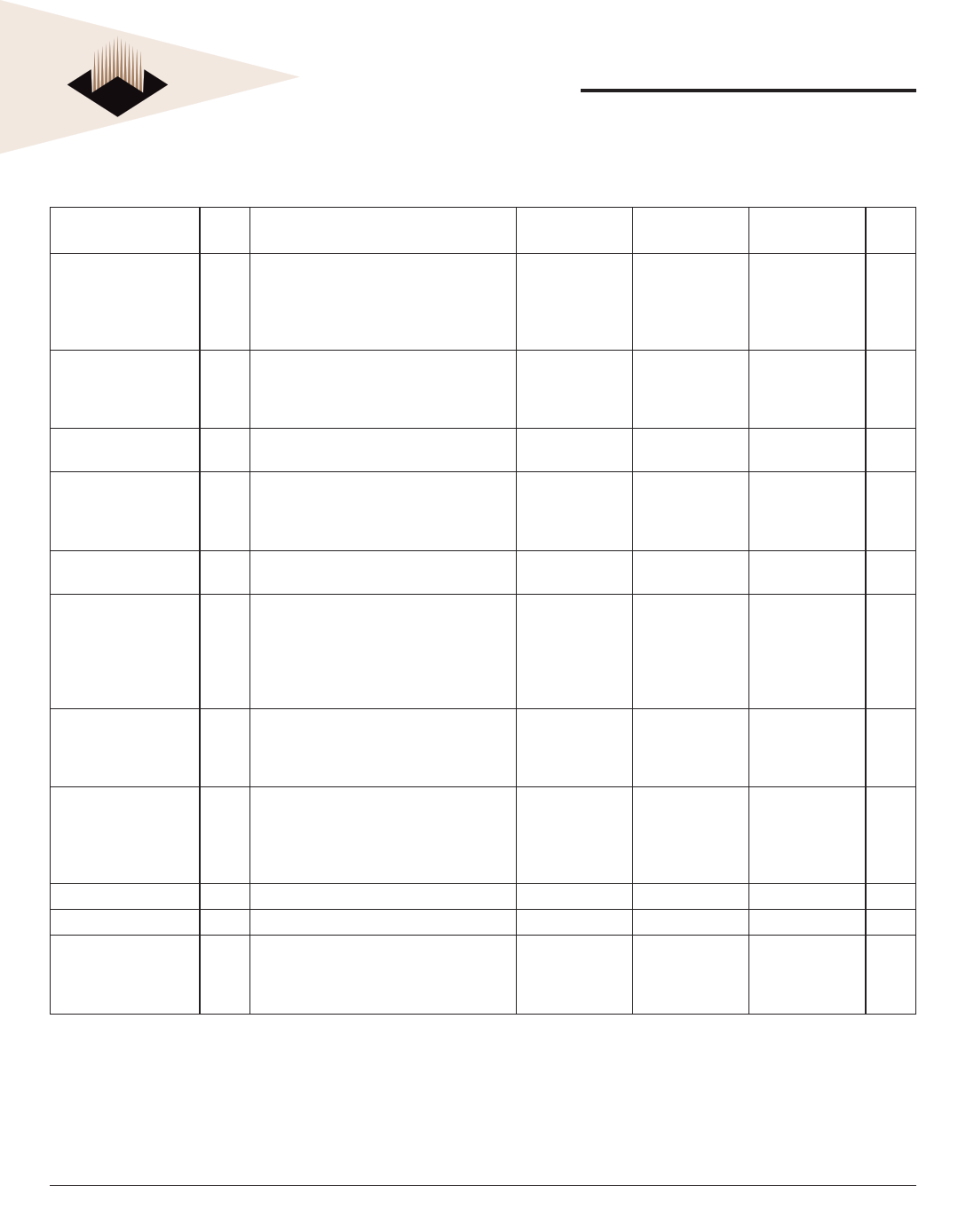

IDD SPECIFICATIONS AND TEST CONDITIONS

Recommended operating conditions, 0°c ≤ TA ≤ 70°C, VCCQ = 2.5V ± 0.2V, VCC = 2.5V ± 0.2V

Parameter

Operating Current

Operating Current

Precharge Power-Down

Standby Current

Idle Standby Current

Active Power-Down

Standby Current

Active Standby Current

Operating Current

Operating Current

Auto Refresh Current

Self Refresh Current

Operating Current

Symbol Conditions

IDD0

IDD1

IDD2P

IDD2F

IDD3P

IDD3N

IDD4R

IDD4W

IDD5

IDD6

IDD7A

One device bank; Active - Precharge;

tRC=tRC(MIN); tCK=tCK(MIN); DQ,DM and DQS

inputs changing once per clock cycle; Address

and control inputs changing once every two

cycles.

One device bank; Active-Read-Precharge;

Burst = 2; tRC=tRC(MIN);tCK=tCK(MIN); Iout =

0mA; Address and control inputs changing

once per clock cycle.

All device banks idle; Power- down mode;

tCK=tCK(MIN); CKE=(low)

CS# = High; All device banks idle;

tCK=tCK(MIN); CKE = high; Address and other

control inputs changing once per clock cycle.

VIN = VREF for DQ, DQS and DM.

One device bank active; Power-down mode;

tCK(MIN); CKE=(low)

CS# = High; CKE = High; One device

bank; Active-Precharge; tRC=tRAS(MAX);

tCK=tCK(MIN); DQ, DM and DQS inputs

changing twice per clock cycle; Address and

other control inputs changing once per clock

cycle.

Burst = 2; Reads; Continous burst; One

device bank active;Address and control inputs

changing once per clock cycle; tCK=tCK(MIN);

Iout = 0mA.

Burst = 2; Writes; Continous burst; One

device bank active; Address and control inputs

changing once per clock cycle; tCK=tCK(MIN);

DQ,DM and DQS inputs changing twice per

clock cycle.

tRC=tRC(MIN)

CKE ≤ 0.2V

Four bank interleaving Reads (BL=4) with auto

precharge with tRC=tRC (MIN); tCK=tCK(MIN);

Address and control inputs change only

during Active Read or Write commands.

DDR333@CL=2.5

Max

2915

3315

96

1075

800

1795

3795

4275

5235

355

7955

DDR266@CL=2.5

Max

2915

3315

96

1075

800

1795

3795

4275

5235

355

7955

DDR200@CL=2

Max

2915

3315

96

1075

800

1795

3795

4275

5235

355

7955

Units

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

mA

May 2004

Rev. 0

5 White Electronic Designs Corporation • (602) 437-1520 • www.wedc.com

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet W3EG64128S-BD4.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W3EG64128S-BD4 | 1GB - 2x64Mx64 DDR SDRAM UNBUFFERED | White Electronic |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |