|

|

PDF USB97C102 Data sheet ( Hoja de datos )

| Número de pieza | USB97C102 | |

| Descripción | Multi-Endpoint USB Peripheral Controller | |

| Fabricantes | SMSC Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de USB97C102 (archivo pdf) en la parte inferior de esta página. Total 70 Páginas | ||

|

No Preview Available !

USB97C102

Multi-Endpoint USB Peripheral Controller with

Integrated 5 Port HUB

www.DataSheet4U.com

FEATURES

!" High Performance USB Peripheral Controller

Engine

- Integrated USB Transceiver

- Serial Interface Engine (SIE)

- 8051 Microcontroller (MCU)

- Patented Memory Management Unit (MMU)

- 4 Channel 8237 DMA Controller (ISADMA)

- 4K Byte On Board USB Packet Buffer

- Quasi-ISA Peripheral Interface

- USB Bus Snooping Capabilities

- GPIOs

!" Pin Compatible with SMSC USB97C100

!" Complete USB Specification 1.1 Compatibility

- Isochronous, Bulk, Interrupt, and Control Data

Independently Configurable per Endpoint

- Dynamic Hardware Allocation of -Packet

Buffer for Virtual Endpoints

- Multiple Virtual Endpoints (up to 16 TX, 16 RX

Simultaneously)

- Multiple Alternate Address Filters

- Dynamic Endpoint Buffer Length Allocation (0-

1280 Byte Packets)

!" USB Full (12Mbps) and Low Speed Capability

!" MMU and SRAM Buffer Allow Buffer Optimization

and Maximum Utilization of USB Bandwidth

- 128 Byte Page Size

- 10 Pages Maximum per Packet

- 32 Deep Receive Packet Queue

- Up to 5 Deep Transmit Packet Queue, per

Endpoint

- Hardware Generated Packet Header Records

Each Packet Status Automatically

- Simultaneous Arbitration Between MCU, SIE,

and ISA DMA Accesses

!" Extended Power Management

- Standard 8051 "Stop Clock" Modes

- Additional USB and ISA Suspend Resume

Events

- Internal 8MHz Ring Oscillator for Immediate

Low Power Code Execution

- 24, 16, 12, 8, 4, and 2 MHz PLL Taps For on

the Fly MCU and DMA Clock Switching

- Independent Clock/Power Management for

SIE, MMU, DMA and MCU

!" DMA Capability with ISA Memory

- Four Independent Channels

- Transfer Between Internal and External

Memory

- Transfer Between I/O and Internal Memory

- External Bus Master Capable

!" Scatter Gather DMA

- Four Independent Channels

- Up to 16 Transfers can be Programmed to

Occur Consecutively Without MCU

InterventionExternal MCU Memory Interface

- 1M Byte Code and Data Storage via 16K

Windows

- Flash, SRAM, or EPROM

- Downloadable via USB, Serial Port, or ISA

Peripheral

!" Quasi-ISA Interface Allows Interface to New and

"Legacy" Peripheral Devices

- 1M ISA Memory Space via 4K MCU Window

- 64K ISA I/O Space via 256 Byte MCU Window

- 4 External Interrupt Inputs

- 4 DMA Channels

- Variable Cycle Timing

- 8 Bit Data Path

!" 3.3 Volt, Low Power Operation

!" 5 Volt Tolerant Operation on I/O Signal Pins

!" On Board Crystal Driver Circuit

!" 128 Pin QFP Package

GENERAL DESCRIPTION

The USB97C102 is a flexible, general purpose USB peripheral interface and controller ideally suited for multiple

endpoint applications. The USB97C102 provides an ISA-like bus interface, which will allow virtually any PC peripheral

to be placed at the end of a USB connection. Its unique dynamic buffer architecture overcomes the throughput

disadvantages of existing fixed FIFO buffer schemes allowing maximum utilization of the USB connection’s overall

bandwidth. This architecture minimizes the integrated microcontroller’s participation in the USB data flow, allowing

back-to-back packet transfers to block oriented devices. The efficiency of this architecture allows floppy drives to

coexist with other peripherals such as serial and parallel ports on a single USB link.

SMSC DS – USB97C102

Rev. 03/23/2000

1 page

QFP PIN

NUMBER

SYMBOL

100 READY

104, 106,

108, 110

DRQ[3:0]

105, 107,

109, 111

103

nDACK

[3:0]

TC

19-13, 127-7,

9-12

112-115, 117-

120

122

SA[19:0]

SD[7:0]

AEN

123 nIOW

124 nIOR

125 nMEMR

126 nMEMW

102 nMASTER

21-24

IRQ[3:0]

DESCRIPTION OF PIN FUNCTIONS

Table 1 - USB97C102 Pin Configuration

PIN DESCRIPTION

ISA INTERFACE

Channel is ready when high.

ISA memory or slave devices use this signal to lengthen a bus

cycle from the default time. Extending the length of the bus cycle

can only be done when the bus cycles are derived from the Internal

DMA controller core. 8051 MCU generated Memory or I/O accesses

cannot and will not be extended even if READY is asserted low by

an external ISA slave device. The external slave device negates this

signal after decoding a valid address and sampling the command

signals (nIOW, nIOR, nMEMW, and nMEMR). When the slave’s

access has completed, this signal should be allowed to float high.

DMA Request channels 3-0; active high.

These signals are used to request DMA service from the DMA controller.

The requesting device must hold the request signal until the DMA

controller drives the appropriate DMA acknowledge signal (nDACK[3:0]).

DMA Acknowledge channels 3-0; active low.

These signals are used to indicate to the DMA requesting device that it

has been granted the ISA bus.

DMA Terminal Count; active high.

This signal is used to indicate that a DMA transfer has completed.

System Address Bus

These signals address memory or I/O devices on the ISA bus.

System Data Bus

These signals are used to transfer data between system devices.

Address Enable

This signal indicates address validation to I/O devices. When low this

signal indicates that an I/O slave may respond to addresses and I/O

commands on the bus. This signal is high during DMA cycles to prevent

I/O slaves from interpreting DMA cycles as valid I/O cycles.

I/O Write; active low.

This signal indicates to the addressed ISA I/O slave to latch data from

the ISA bus.

I/O Read; active low.

This signal indicates to the addressed ISA I/O slave to drive data on the

ISA bus.

Memory read; active low

This signal indicates to the addressed ISA memory slave to drive

data on the ISA bus.

Memory write; active low

This signal indicates to the addressed ISA memory slave to latch data

from the ISA bus.

External Bus master, active low

This signal forces the USB97C102 to immediately tri-state its external

bus, even if internal transactions are not complete. All shared ISA

signals are tri-stated, except 8237 nDACKs, which can be used in gang

mode to provide external bus-master handshaking. This pin must be

used with some handshake mechanism to avoid data corruption.

Interrupt Request 3-0; active high

These signals are driven by ISA devices on the ISA bus to interrupt the

8051.

BUFFER

TYPE

IP

I

O8

O8

O8

I/O8

O8

O8

O8

O8

O8

IP

I

SMSC DS – USB97C102

Page 5

Rev. 03/23/2000

5 Page

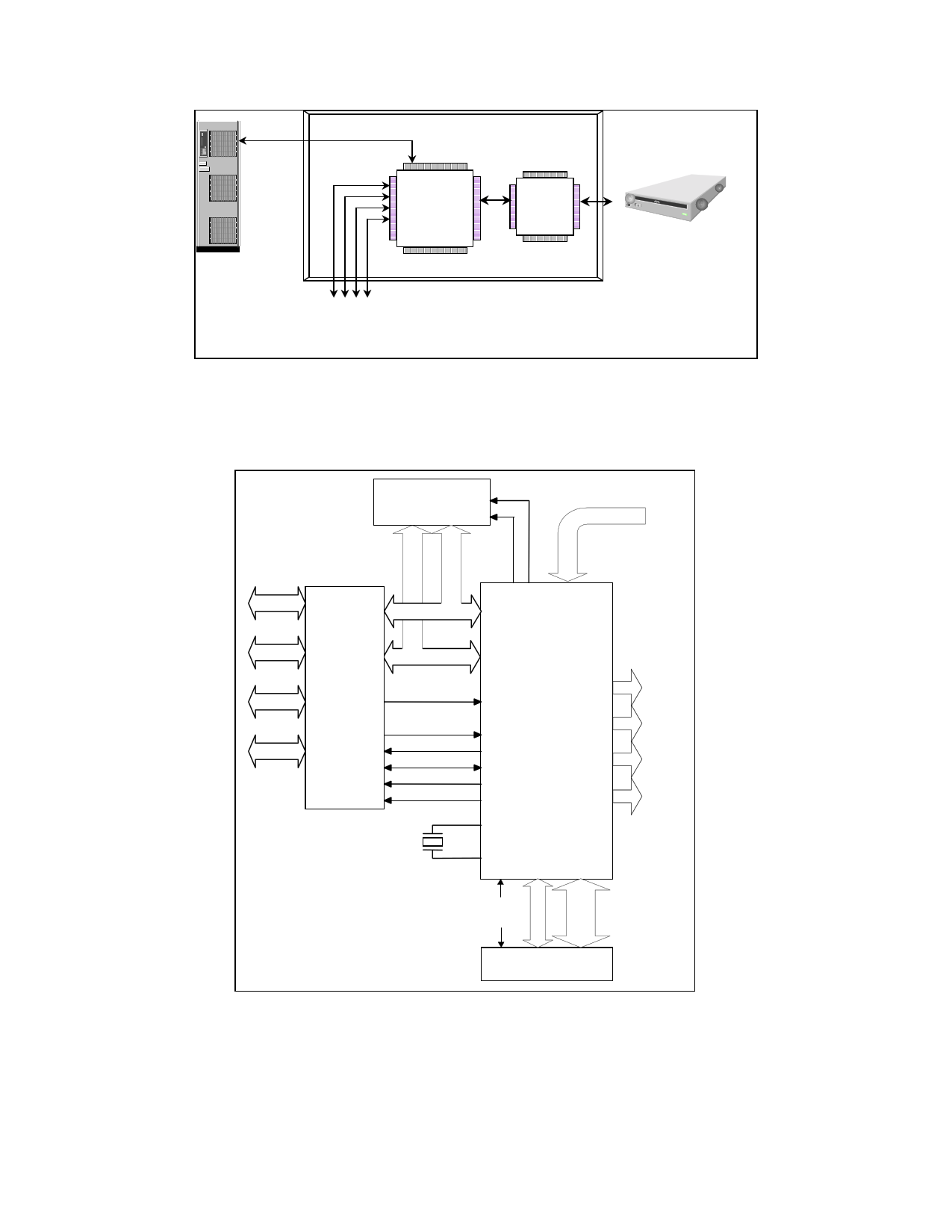

TYPICAL FLOPPY DRIVE APPLICATION

USB Upstream

97C102

37C78

FDC

USB Downstream

Walkup Ports

FIGURE 4 – USB97C102 CONFIGURED FOR FLOPPY DRIVE APPLICATION AND WALKUP PORTS

TYPICAL SIGNAL CONNECTIONS

SRAM

USB UPSTREAM

FDC

SD[7..0]

LPT SA[10..0]

UART FDC37C669FR

IR

IRQ[3..0]

nDACK[3..0]

DRQ[3..0]

TC

nIOR

nIOW

24MHz

USB97C102

FLASH

FIGURE 5 – USB97C102 CONFIGURED WITH FDC CONTROLLER AND WALKUP PORTS

SMSC DS – USB97C102

Page 11

Rev. 03/23/2000

11 Page | ||

| Páginas | Total 70 Páginas | |

| PDF Descargar | [ Datasheet USB97C102.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| USB97C100 | Multi-Endpoint USB Peripheral Controller | SMSC Corporation |

| USB97C102 | Multi-Endpoint USB Peripheral Controller | SMSC Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |