|

|

PDF DIX4192 Data sheet ( Hoja de datos )

| Número de pieza | DIX4192 | |

| Descripción | Integrated Digital Audio Interface Receiver and Transmitter | |

| Fabricantes | Burr-Brown | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de DIX4192 (archivo pdf) en la parte inferior de esta página. Total 60 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

BurrĆBrown Products

from Texas Instruments

DIX4192

DIX4192

SBFS031C – JANUARY 2006 – REVISED JUNE 2006

Integrated Digital Audio Interface Receiver and Transmitter

FEATURES

• Digital Audio Interface Transmitter (DIT)

– Supports Sampling Rates Up to 216kHz

– Includes Differential Line Driver and

CMOS Buffered Outputs

– Block-Sized Data Buffers for Both Channel

Status and User Data

– Status Registers and Interrupt Generation

for Flag and Error Conditions

• Digital Audio Interface Receiver (DIR)

– PLL Lock Range Includes Sampling Rates

from 20kHz to 216kHz

– Includes Four Differential Input Line

Receivers and an Input Multiplexer

– Bypass Multiplexer Routes Line Receiver

Outputs to Line Driver and Buffer Outputs

– Block-Sized Data Buffers for Both Channel

Status and User Data

– Automatic Detection of Non-PCM Audio

Streams (DTS CD/LD and IEC 61937

formats)

– Audio CD Q-Channel Sub-Code Decoding

and Data Buffer

– Status Registers and Interrupt Generation

for Flag and Error Conditions

– Low Jitter Recovered Clock Output

• User-Selectable Serial Host Interface: SPI™

or I2C™

– Provides Access to On-Chip Registers and

Data Buffers

• Two Audio Serial Ports (Ports A and B)

– Synchronous Serial Interface to External

Signal Processors, Data Converters, and

Logic

– Slave or Master Mode Operation with

Sampling Rates up to 216kHz

– Supports Left-Justified, Right-Justified, and

Philips I2S™ Data Formats

– Supports Audio Data Word Lengths Up to

24 Bits

• Four General-Purpose Digital Outputs

– Multifunction Programmable Via Control

Registers

• Extensive Power-Down Support

– Functional Blocks May Be Disabled

Individually When Not In Use

• Operates From +1.8V Core and +3.3V I/O

Power Supplies

• Small TQFP-48 Package, Compatible with the

SRC4382 and SRC4392

APPLICATIONS

• DIGITAL AUDIO RECORDERS AND

MIXING DESKS

• DIGITAL AUDIO INTERFACES FOR

COMPUTERS

• DIGITAL AUDIO ROUTERS AND

DISTRIBUTION SYSTEMS

• BROADCAST STUDIO EQUIPMENT

• DVD/CD RECORDERS

• SURROUND SOUND DECODERS AND

A/V RECEIVERS

• CAR AUDIO SYSTEMS

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

Dolby is a registered trademark of Dolby Laboratories, Inc.

I2C, I2S are trademarks of Koninklijke Philips Electronics N.V.

SPI is a trademark of Motorola.

All other trademarks are the property of their respective owners.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

Copyright © 2006, Texas Instruments Incorporated

1 page

DIX4192

www.ti.com

SBFS031C – JANUARY 2006 – REVISED JUNE 2006

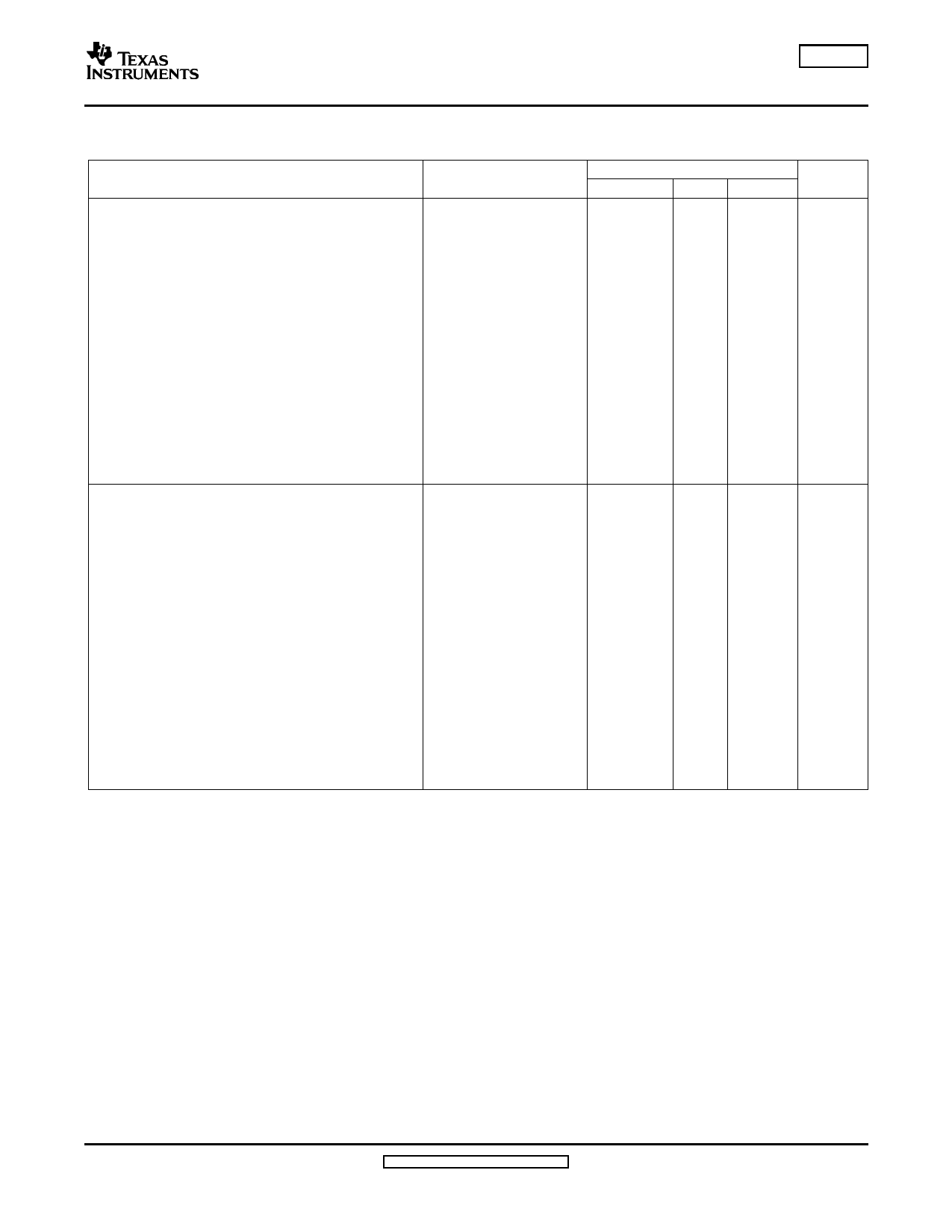

ELECTRICAL CHARACTERISTICS: I2C Standard and Fast Modes

All specifications are at TA = +25°C, VDD18 = +1.8V, VDD33 = +3.3V, VIO = +3.3V, and VCC = +3.3V, unless otherwise noted.

DIX4192

PARAMETER

CONDITIONS

MIN

TYP

MAX

HOST INTERFACE: I2C Standard Mode(1)

SCL clock frequency, fSCL

Hold time repeated START condition, tHDSTA

Low period of SCL clock, tLOW

High period of SCL clock, tHIGH

Setup time repeated START condition, tSUSTA

Data hold time, tHDDAT

Data setup time, tSUDAT

Rise time for Both SDA and SDL, tR

Fall time for Both SDA and SDL, tF

Setup time for STOP condition, tSUSTO

Bus free time between START and STOP, tBUF

Capacitive load for each bus Line, CB

Noise margin at low level (including hysteresis), VNL

Noise margin at high level (including hysteresis), VNH

HOST INTERFACE: I2C Fast Mode(1)

0

4

4.7

4

4.7

0 (2)

250

4

4.7

0.1 × VIO

0.2 × VIO

100

3.45 (3)

1000

300

400

SCL clock frequency, fSCL

Hold time repeated START condition, tHDSTA

Low period of SCL clock, tLOW

High period of SCL clock, tHIGH

Setup time repeated START condition, tSUSTA

Data hold time, tHDDAT

Data setup time, tSUDAT

Rise time for both SDA and SDL, tR

Fall time for both SDA and SDL, tF

Setup time for STOP condition, tSUSTO

Bus free time between START and STOP, tBUF

Spike pulse width suppressed by input filter, tSP

Capacitive load for Each bus Line, CB

Noise margin at low level (including hysteresis), VNL

Noise margin at high level (including hysteresis), VNH

0

0.6

1.3

0.6

0.6

0 (2)

100 (4)

20 + 0.2CB(5)

20 + 0.2CB(5)

0.6

1.3

0

0.1 × VIO

0.2 × VIO

400

0.9 (3)

300

300

50

400

UNITS

kHz

µs

µs

µs

µs

µs

ns

ns

ns

µs

µs

pF

V

V

kHz

µs

µs

µs

µs

µs

ns

ns

ns

µs

µs

ns

pF

V

V

(1) All values referred to the VIH minimum and VIL maximum levels listed in the Digital I/O Characteristics section of the Electrical

Characteristics: General, DIR, and DIT table.

(2) A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the VIH minimum input level) to bridge the

undefined region of the falling edge of SCL.

(3) The maximum tHDDAT has only to be met if the device does not stretch the Low period (tLOW) of the SCL signal.

(4) A Fast mode I2C bus device can be used in a Standard mode I2C bus system, but the requirement that tSUDAT be 250ns (minimum)

must then be met. For the DIX4192, this condition is automatically the case, since the device does not stretch the Low period of the SCL

signal.

(5) CB is defined as the total capacitance of one bus line in picofarads (pF). If mixed with High-Speed mode devices, faster fall times are

allowed.

Submit Documentation Feedback

5

5 Page

DIX4192

www.ti.com

SBFS031C – JANUARY 2006 – REVISED JUNE 2006

PRODUCT OVERVIEW (continued)

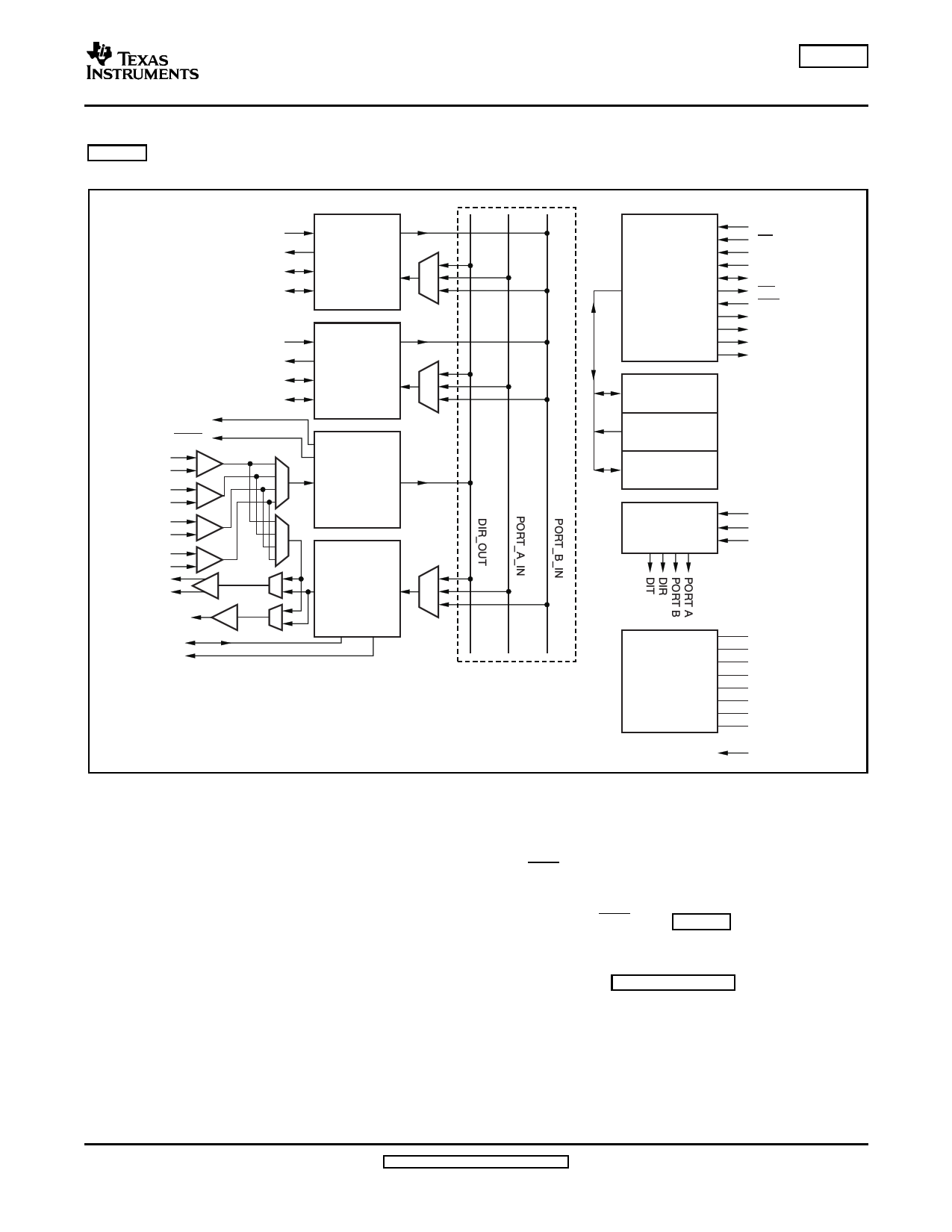

Figure 4 shows a simplified functional block diagram for the DIX4192. Additional details for each function block

will be covered in respective sections of this datasheet.

DIX4192

SDINA

SDOUTA

LRCKA

BCKA

RXCKO

LOCK

RX1+

RX1-

RX2+

RX2-

RX3+

RX3-

RX4+

RX4-

TX+

TX-

AESOUT

BLS

SYNC

SDINB

SDOUTB

LRCKB

BCKB

Audio Serial

Port A

Audio Serial

Port B

Digital

Interface

Receiver (DIR)

Digital

Interface

Transmitter

(DIT)

Host

Interface

(SPI or I2C)

and

General-

Purpose

Outputs

Control and Status

Registers

DIR C and U

Data Buffers

DIT C and U

Data Buffers

Master

Clock

Distribution

Power

Figure 4. Functional Block Diagram

Internally Tied

to Substrate

CPM

CS or A0

CCLK or SCL

CDIN or A1

CDOUT or SDA

INT

RST

GPO1

GPO2

GPO3

GPO4

MCLK

RXCKI

From RXCKO

VDD18

DGND1

VDD33

DGND2

VIO

DGND3

VCC

AGND

BGND

RESET OPERATION

The DIX4192 includes an asynchronous active low reset input, RST (pin 24), which may be used to initialize the

internal logic at any time. The reset sequence forces all registers and buffers to their default settings. The reset

low pulse width must be a minimum of 500ns in length. The user should not attempt a write or read operation

using either the SPI or I2C port for at least 500µs after the rising edge of RST. See Figure 5 for the reset timing

sequence of the DIX4192.

In addition to reset input, the RESET bit in control register 0x01 may be used to force an internal reset, whereby

all registers and buffers are forced to their default settings. Refer to the Control Registers section for details

regarding the RESET bit function.

Upon reset initialization, all functional blocks of the DIX4192 default to the power-down state, with the exception

of the SPI or I2C host interface and the corresponding control registers. The user may then program the

DIX4192 to the desired configuration, and release the desired function blocks from the power-down state

utilizing the corresponding bits in control register 0x01.

Submit Documentation Feedback

11

11 Page | ||

| Páginas | Total 60 Páginas | |

| PDF Descargar | [ Datasheet DIX4192.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DIX4192 | Integrated Digital Audio Interface Receiver and Transmitter (Rev. E) | Texas Instruments |

| DIX4192 | Integrated Digital Audio Interface Receiver and Transmitter | Burr-Brown |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |