|

|

PDF DM560P Data sheet ( Hoja de datos )

| Número de pieza | DM560P | |

| Descripción | V.90 Integrated Data/Fax/Voice/Speakerphone Modem Device Set | |

| Fabricantes | Davicom | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de DM560P (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

DM560P

V.90 Integrated Data/Fax/Voice/Speakerphone Modem Device Set

General Description

The DM560P integrated modem is a four chipset

design that provides a complete solution for state-

of-the-art, voice-band Plain Old Telephone Service

(POTS) communication. The modem provides for

Data (up to 56,000bps), Fax (up to 14,400bps),

Voice and Full Duplex Speaker-phone functions to

comply with various international standards.

The design of the DM560P is optimized for desktop

personal computer applications and it provides a low

cost, highly reliable, maximum integration, with the

minimum amount of support required. The DM560P

modem can operate over a dial-up network (PSTN)

or 2 wire leased lines.

The modem integrates auto dial and answer

capabilities, synchronous and asynchronous data

transmissions, serial and parallel interfaces, various

tone detection schemes and data test modes.

The DM560P modem reference design is pre-

approved for FCC part 68 and provides minimum

design cycle time, with minimum cost to insure the

maximum amount of success.

The simplified modem system, shown in figure

below, illustrates the basic interconnection between

the MCU, DSP, AFE and other basic components of

a modem. The individual elements of the DM560P

are:

• DM6580 Analog Front End (AFE). 28-pin PLCC

package

• DM6581 ITU-T V.90 Transmit Digital Signal

Processor (TX DSP). 100-pin QFP package

• DM6582 ITU-T V.90 Receive Digital Signal

Processor (RX DSP). 100-pin QFP package

• DM6583 Modem Controller (MCU) built in Plug &

Play (PnP). 100-pin QFP package

Block Diagram

LED

40.32MHz

Ring

Detector

29.4912

MHz

ISA Bus

DM658

3

Micro

Controller

Unit

PnP

V.24

Interface

Address &

Data Bus

MSCLK

DM658

1

TX DSP

TxD

RxD

DM658

2

RX DSP

SCLK

DIT

DOT

TFS

DIR

DOR

RFS

TxBCLK

TxSCLK*2

RxBCLK

RxSCLK

20.16MHz

TxDCLK

RxDCLK

DM658

0

RxIN

TxA1 DAA

Analog TxA2

Front End

Speaker

SPKR

Driver

Lin

e

Microphone

Driver

V.24

Interface

Preliminary

Version: DM560P-DS-P07

August 11, 2000

1

1 page

DM560P

V.90 Integrated Data/Fax/Voice/Speakerphone Modem Device Set

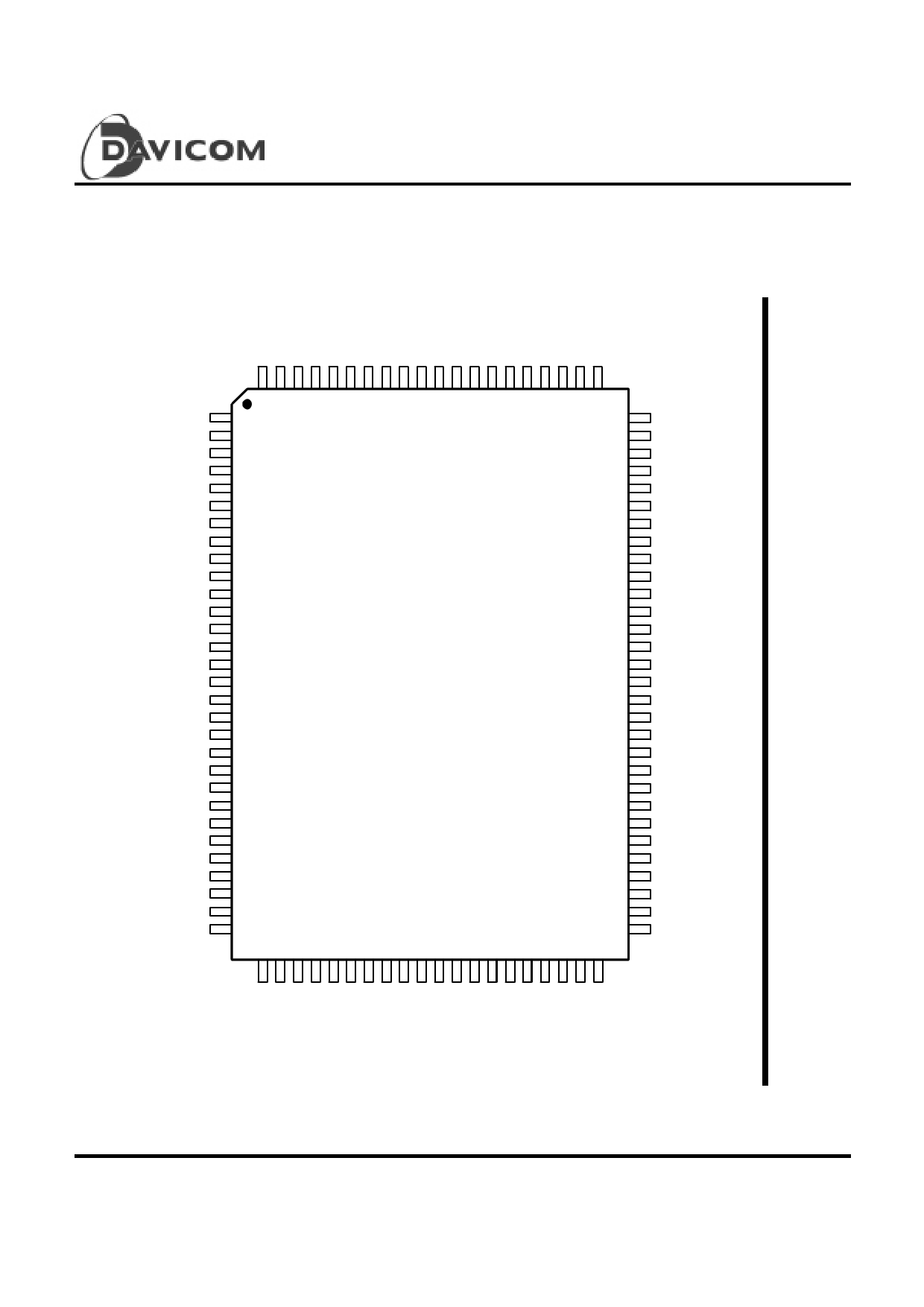

DM6583 Pin Configuration

UD0

UD1

UD2

UD3

UD4

UD5

UD6

UD7

/IOR

GND

/IOW

/AEN

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

VDD

IRQ4

IRQ5

IRQ7

IRQ10

RESET

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

DM6583

80 D4

79 D5

78 D6

77 D7

76 CA0

75 CA1

74 CA2

73 CA3

72 CA4

71 CA5

70 CA6

69 CA7

68 GND

67 CA8

66 CA9

65 CA10

64 CA11

63 CA12

62 CA13

61 CA14

60 CA15

59 IRQ3

58 /RD

57 /WR

56 /PSEN

55 ALE/P

54 TXD

53 RXD

52 VDD

51 /LCS

Preliminary

Version: DM560P-DS-P07

August 11, 2000

5

5 Page

DM560P

V.90 Integrated Data/Fax/Voice/Speakerphone Modem Device Set

1: In _ buffer empty (clear automatically by a

write to In _buffer)

0: In _ buffer not empty

Bit7: reset bit(write only)

1: software reset

(4)CRCL register: Address DC0AH (read only)

(5)CRCH register: Address DC0BH (read only)

UART (16550A) Emulation Registers

Receiver Buffer (Read), Transmitter Holding

Register (Write): Address: 0 (DLAB=0)

Reset State 00h

bit7 bit6 bit5 bit4 bit3 Bit2 bit1 bit0

dat7 dat6 dat5 dat4 dat3 Dat2 dat1 dat0

Interrupt Identification Register (IIR): Address 2

Reset State 01h, Read only

Bit7 Bit6 bit5 bit4 bit3 bit2 bit1 bit0

FIFO 0 0 0 D3: D2: D1: D0:

Enable

INTD2 INTD1 INTD0 int

Pending

In order to provide minimum software overhead

during data transfers, the virtual UART prioritizes

interrupts into four levels as follows: Receiver Line

Status (priority 1), Receiver Data Available (priority

2), Character Timeout Indication (priority 2, FIFO

mode only), Transmitter Holding Register Empty

(priority 3), and Modem Status (priority 4).

When this register address is read, it contains the

parallel received data. Data to be transmitted is

written to this register.

Interrupt Enable Register (IER): Address 1

The IIR register gives prioritized information

regarding the status of interrupt conditions. When

accessed, the IIR indicates the highest priority

interrupt that is pending.

Reset State 00h, Write Only

bit7 bit6 bit Bit4 bit3 bit2 bit1 bit0

5

000

0 Enable Enable Enable Enable

Modem Line TX

RX

Status Status Holding Data

Intr Intr Registe Intr

r

Intr

Bit 0: This bit can be used in either a prioritized

interrupt or polled environment to indicate

whether an interrupt is pending. When this bit

is a logic 0, an interrupt is pending, and the IIR

contents may be used as a pointer to the

appropriate interrupt service routine. When bit

0 is a logic 1, no interrupt is pending, and

polling (if used) continues.

This 8-bit register enables the four types of interrupts

as described below. Each interrupt source can

activate the INT output signal if enabled by this

register. Resetting bits 0 through 3 will disable all

UART interrupts.

Bit 0: This bit enables the Received Data Available

and timeout interrupts in the FIFO mode when

set to logic 1.

Bit 1-2: These two bits of the IIR are used to identify

the highest priority interrupt pending, as

indicated in the table below.

Bit 3: In character mode, this bit is 0. In FIFO mode,

this bit is set, along with bit 2, when a timeout

interrupt is pending.

Bit 4-6: Not used

Bit 1: This bit enables the Transmitter Holding

Register Empty Interrupt when set to logic 1.

Bit 7: FIFO always enabled.

Bit 2: This bit enables the Receiver Line Status

Interrupt when set to logic 1.

Bit 3: This bit enables the MODEM Status Interrupt

when set to logic 1.

Bit 4-7: Not used

Preliminary

Version: DM560P-DS-P07

August 11, 2000

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet DM560P.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DM560P | V.90 Integrated Data/Fax/Voice/Speakerphone Modem Device Set | Davicom |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |