|

|

PDF 82077AA Data sheet ( Hoja de datos )

| Número de pieza | 82077AA | |

| Descripción | CHMOS SINGLE-CHIP FLOPPY DISK CONTROLLER | |

| Fabricantes | Intel Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 82077AA (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

82077AA

CHMOS SINGLE-CHIP FLOPPY DISK CONTROLLER

Y Single-Chip Floppy Disk Solution

100% PC AT Compatible

100% PS 2 Compatible

100% PS 2 Model 30 Compatible

Integrated Drive and Data Bus

Buffers

Y Integrated Analog Data Separator

250 Kbits sec

300 Kbits sec

500 Kbits sec

1 Mbits sec

Y High Speed Processor Interface

Y Perpendicular Recording Support

Y Integrated Tape Drive Support

Y 12 mA Host Interface Drivers 40 mA

Disk Drivers

Y Four Fully Decoded Drive Select and

Motor Signals

Y Programmable Write Precompensation

Delays

Y Addresses 256 Tracks Directly

Supports Unlimited Tracks

Y 16 Byte FIFO

Y 68-Pin PLCC

(See Packaging Spec Order 240800 Package Type N)

The 82077AA floppy disk controller has completely integrated all of the logic required for floppy disk control

The 82077AA a 24 MHz crystal a resistor package and a device chip select implements a PC AT or PS 2

solution All programmable options default to compatible values The dual PLL data separator has better

performance than most board level discrete PLL implementations The FIFO allows better system perform-

ance in multi-master systems (e g PS 2 EISA) The 82077AA is available in three versions 82077AA-5

82077AA and 82077AA-1 82077AA-1 has all features listed in this data sheet It supports both tape drives and

4 Mb floppy drives The 82077AA supports 4 Mb floppy drives and is capable of operation at all data rates

through 1 Mbps The 82077AA-5 supports 500 300 250 Kbps data rates for high and low density floppy

drives

The 82077AA is fabricated with Intel’s CHMOS III technology and is available in a 68-lead PLCC (plastic)

package

PS 2 and PC AT are trademarks of IBM

Figure 1 82077AA Pinout

May 1994

290166 – 1

Order Number 290166-007

1 page

82077AA

Table 1 82077AA Pin Description (Continued)

Symbol Pin I O

Description

HOST INTERFACE (Continued)

IDENT

27 I IDENTITY Upon Hardware RESET this input (along with MFM pin) selects

between the three interface modes After RESET this input selects the type of

drive being accessed and alters the level on DENSEL The MFM pin is also

sampled at Hardware RESET and then becomes an output again Internal pull-

ups on MFM permit a no connect

IDENT MFM INTERFACE

1 1 or NC AT Mode

10

ILLEGAL

0 1 or NC PS 2 Mode

00

Model 30 Mode

AT MODE Major options are enables DMA Gate logic TC is active high

Status Registers A B not available

PS 2 MODE Major options are No DMA Gate logic TC is active low Status

Registers A B are available

MODEL 30 MODE Major options are enable DMA Gate logic TC is active

high Status Registers A B available

After Hardware reset this pin determines the polarity of the DENSEL pin IDENT

at a logic level of ‘‘1’’ DENSEL will be active high for high (500 Kbps 1 Mbps)

data rates (typically used for 5 25 drives) IDENT at a logic level of ‘‘0’’

DENSEL will be active low for high data rates (typically used for 3 5 drives)

INVERT is tied to ground

DISK CONTROL (All outputs have 40 mA drive capability)

INVERT 35 I INVERT Strapping option Determines the polartity of all signals in this section

Should be strapped to ground when using the internal buffers and these signals

become active LOW When strapped to VCC these signals become active high

and external inverting drivers and receivers are required

ME0

ME1

ME2

ME3

57 O ME0–3 Decoded Motor enables for drives 0 – 3 The motor enable pins are

61 directly controlled via the Digital Output Register

63

66

DS0 58 O DRIVE SELECT 0 – 3 Decoded drive selects for drives 0 – 3 These outputs are

DS1 62

DS2 64

decoded from the select bits in the Digital Output Register and gated by

ME0 – 3

DS3 67

HDSEL

51 O HEAD SELECT Selects which side of a disk is to be used An active level

selects side 1

STEP

55 O STEP Supplies step pulses to the drive

DIR 56 O DIRECTION Controls the direction the head moves when a step signal is

present The head moves toward the center if active

WRDATA 53

O WRITE DATA FM or MFM serial data to the drive Precompensation value is

selectable through software

WE 52 O WRITE ENABLE Drive control signal that enables the head to write onto the

disk

5

5 Page

82077AA

COMMAND BUSY This bit is set to a one when a

command is in progress This bit will go active after

the command byte has been accepted and goes in-

active at the end of the results phase If there is no

result phase (SEEK RECALIBRATE commands)

this bit is returned to a 0 after the last command

byte

DRV x BUSY These bits are set to ones when a

drive is in the seek portion of a command including

seeks and recalibrates

2 1 7 FIFO (DATA)

All command parameter information and disk data

transfers go through the FIFO The FIFO is 16 bytes

in size and has programmable threshold values

Data transfers are governed by the RQM and DIO

bits in the Main Status Register

The FIFO defaults to an 8272A compatible mode

after a ‘‘Hardware’’ reset (Reset via pin 32) ‘‘Soft-

ware’’ Resets (Reset via DOR or DSR register) can

also place the 82077AA into 8272A compatible

mode if the LOCK bit is set to ‘‘0’’ (See section 5 3 2

for the definition of the LOCK bit) This maintains

PC-AT hardware compatibility The default values

can be changed through the CONFIGURE com-

mand (enable full FIFO operation with threshold

control) The advantage of the FIFO is that it allows

the system a larger DMA latency without causing a

disk error Table 2 5 gives several examples of the

delays with a FIFO The data is based upon the fol-

lowing formula

1

Threshold c

c 8 b 1 5 ms e DELAY

DATA RATE

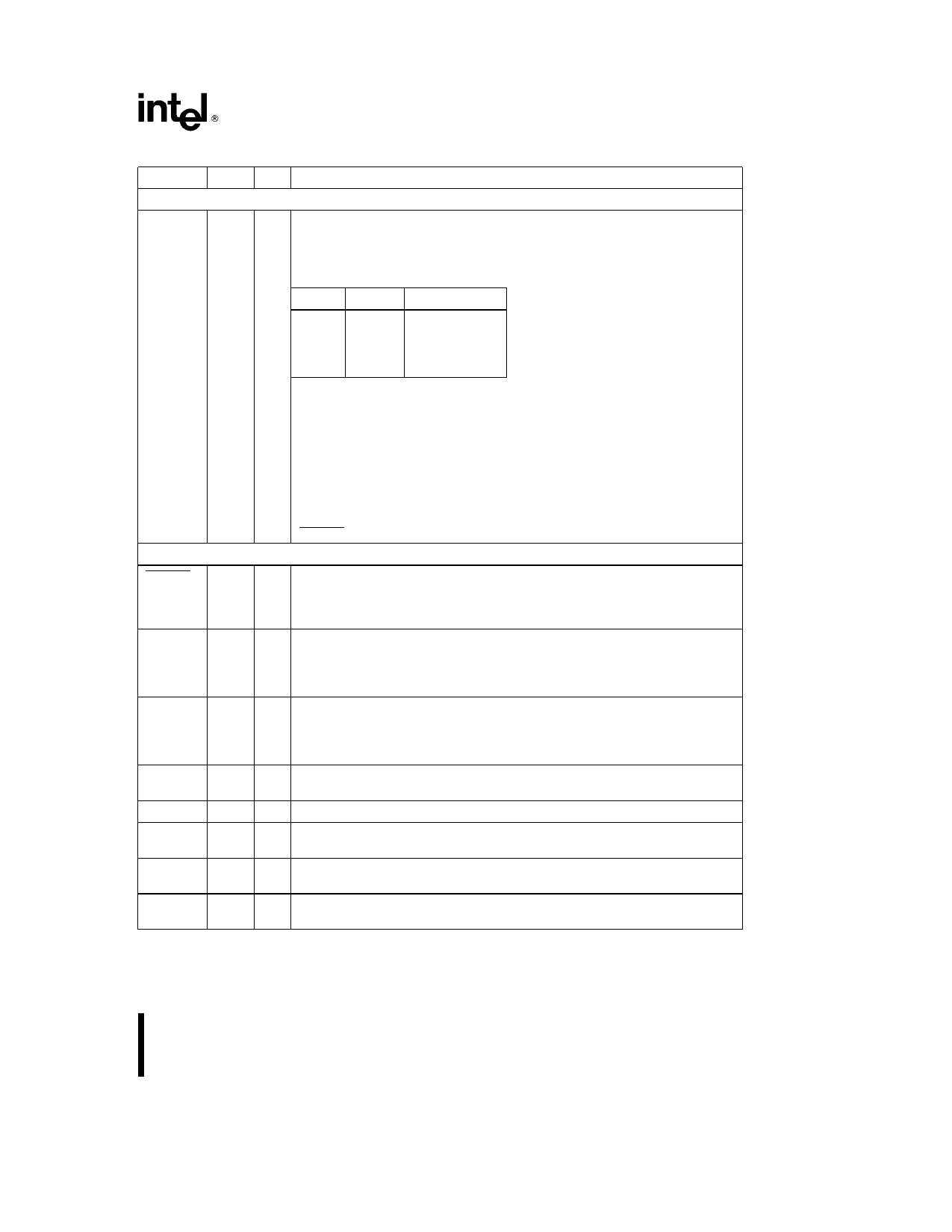

Table 2-5 FIFO Service Delay

FIFO Threshold Maximum Delay to Servicing

Examples

at 1 Mbps Data Rate

1 byte

2 bytes

8 bytes

15 bytes

1 c 8 ms b 1 5 ms e 6 5 ms

2 c 8 ms b 1 5 ms e 14 5 ms

8 c 8 ms b 1 5 ms e 62 5 ms

15 c 8 ms b 1 5 ms e 118 5 ms

FIFO Threshold Maximum Delay to Servicing

Examples

at 500 Kbps Data Rate

1 byte

2 bytes

8 bytes

15 bytes

1 c 16 ms b 1 5 ms e 14 5 ms

2 c 16 ms b 1 5 ms e 30 5 ms

8 c 16 ms b 1 5 ms e 126 5 ms

15 c 16 ms b 1 5 ms e 238 5 ms

At the start of a command the FIFO action is always

disabled and command parameters must be sent

based upon the RQM and DIO bit settings As the

82077AA enters the command execution phase it

clears the FIFO of any data to ensure that invalid

data is not transferred

An overrun or underrun will terminate the current

command and the transfer of data Disk writes will

complete the current sector by generating a 00 pat-

tern and valid CRC

2 1 8a DIGITAL INPUT REGISTER

(DIR PC-AT MODE)

This register is read only in all modes In PC-AT

mode only bit 7 is driven all other bits remain tristat-

ed

7 6 5 4 3 2 10

DSK

CHG

DSKCHG monitors the pin of the same name and

reflects the opposite value seen on the disk cable

regardless of the value of INVERT

2 1 8b DIGITAL INPUT REGISTER

(DIR PS 2 MODE)

76543

2

10

DSK

DRATE DRATE HIGH

1111

CHG

SEL1 SEL0 DENS

The following is changed in PS 2 Mode Bits 6 5 4

and 3 return a value of ‘‘1’’ and the DRATE SEL1-0

return the value of the current data rate selected

(see Table 2-4 for values)

HIGH DENS is low whenever the 500 Kbps or

1 Mbps data rates are selected This bit is indepen-

dent of the effects of the IDENT and INVERT pins

Table 2-6 shows the state of the DENSEL pin when

INVERT is low

Table 2-6 DENSEL Encoding

Data Rate

IDENT

DENSEL

1 Mbps

0

0

11

500 Kbps

0

0

11

300 Kbps

0

1

10

250 Kbps

0

1

1

After (‘‘Hardware’’) Chip Reset

0

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet 82077AA.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 82077AA | CHMOS SINGLE-CHIP FLOPPY DISK CONTROLLER | Intel Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |