|

|

PDF BGY284 Data sheet ( Hoja de datos )

| Número de pieza | BGY284 | |

| Descripción | Power amplifier with integrated control loop | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de BGY284 (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

DISCRETE SEMICONDUCTORS

DATA SHEET

BGY284

power amplifier with integrated

control loop for GSM850,

EGSM900, DCS1800 & PCS1900

Preliminary specification

2003 Aug 20

1 page

Philips Semiconductors

power amplifier with integrated control loop for

GSM850, EGSM900, DCS1800 & PCS1900

Preliminary specification

BGY284

FUNCTIONAL DESCRIPTION

Operating conditions

The BGY284 is designed to meet the 3GPP TS 45.005 technical specification for the European Telecommunication

Standards Institute (ETSI).

Power amplifier

The low band (GSM850 and EGSM900) and the high band (DCS1800 and PCS1900) power amplifiers both consist of 3

cascaded gain stages. Input and output matching as well as harmonic filters are integrated in the module. The output

power is controlled by means of an internal control signal (generated in the power controller block) that is used to adapt

the biasing of the 3 stages of an amplifier.

For every line-up the power amplifier block generates a detected output power signal, that is an input to the power control

block.

Control logic

In the control logic block the various signals are generated to control the complete BGY284 out of VTXon and Vband, as

indicated in the mode control table. The VSTAB is used as supply for the control logic. When VSTAB = 0 V the BGY284 is

in idle mode and the battery current consumption is almost zero.

The VTXon signal “HIGH” enables the power control block. When Vband signal is “LOW” the low band

(GSM850/EGSM900) line-up is enabled, when the Vband signal is “HIGH” the high band (DCS1800/PCS1900) channel

is enabled.

On both VTXon and Vband inputs there are pull down resistors of approximately 1 MΩ.

Power controller

Main inputs to the power controller block are the VDAC and the internal generated detected output power signals from the

power amplifier block.

The VDAC signal is the reference voltage for the requested output power level, and usualy is generated by an external

digital analog converter.

The VDAC signal is buffered and compared to the detected output power signal. The error signal is then further amplified

by the integrator.

Dependent on the Vband signal one of the integrators are selected. The output of the selected integrator is the internal

control signal that sets the biasing circuits of the selected channel.

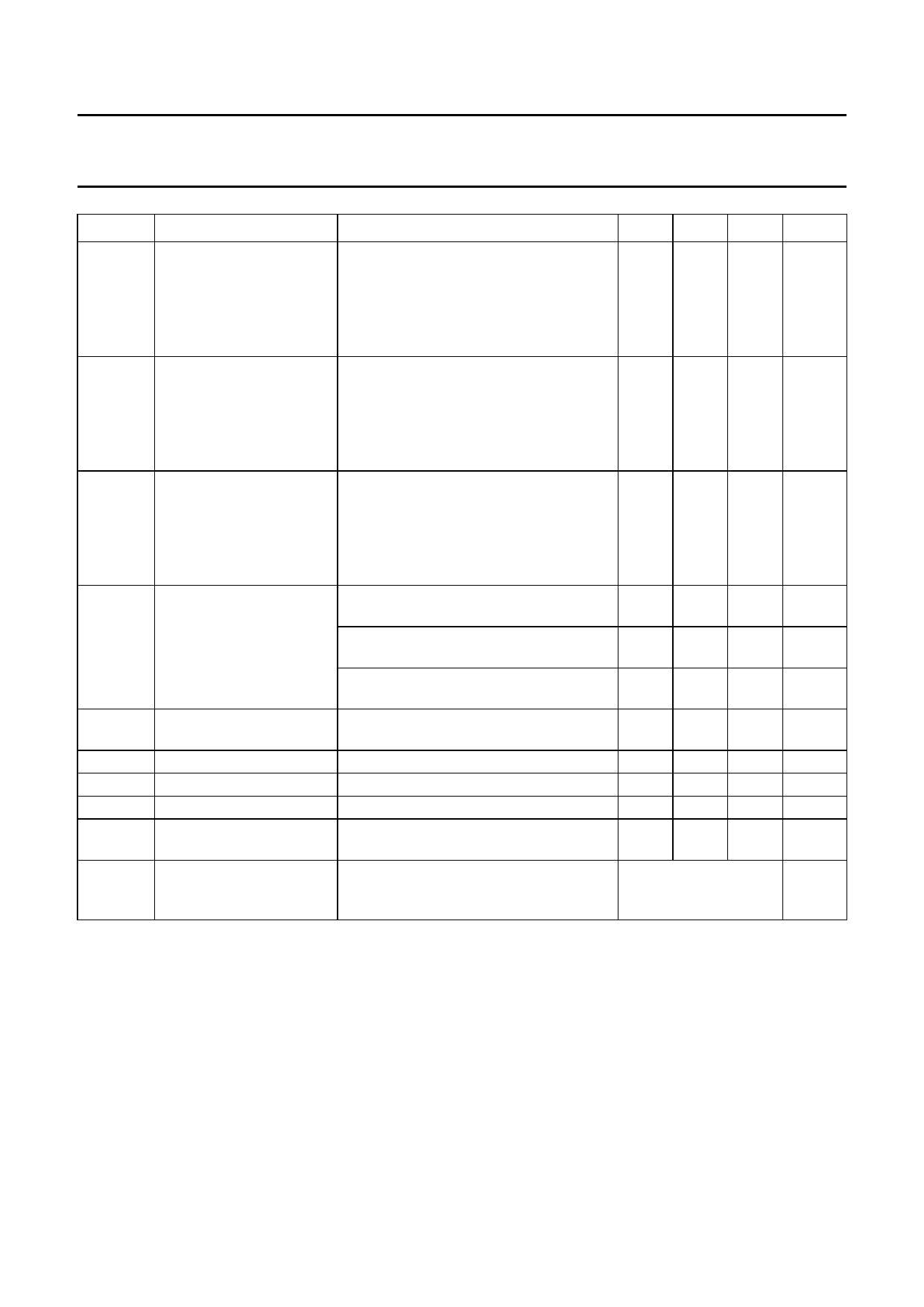

Mode control

MODE

Idle

Standby

LB TX

HB TX

Mode description

complete PA off, minimal leakage current

control logic functioning, PA off

low band transmit mode

high band transmit mode

VSTAB

(V)

0

2.6...3

2.6...3

2.6...3

VTXon

0

0

1

1

Vband

0

logic 1 or logic 0

0

1

VDAC

(V)

<0.15

<0.15

<2.5

<2.5

2003 Aug 20

5

5 Page

Philips Semiconductors

power amplifier with integrated control loop for

GSM850, EGSM900, DCS1800 & PCS1900

Preliminary specification

BGY284

SYMBOL

PARAMETER

CONDITIONS

MIN. TYP. MAX. UNIT

Pn

CG

SSG

AM/AM

AM/PM

tr , tf

fCL

noise power

conversion gain

small signal gain

AM/AM conversion

AM/PM conversion

maximum control slope

carrier rise and fall time

control loop bandwidth

stability

ruggedness

RBW = 100 kHz;

f0 = 897.5 MHz for EGSM900;

f0 = 836.5 MHz for GSM850;

f0 + 10 MHz; PL LB < 34 dBm;

f0 + 20 MHz; PL LB < 34 dBm;

f ≥ 1805 MHz; PL LB < 34 dBm;

f0 = 915 MHz for EGSM900;

f0 = 849 MHz for GSM850;

5 ≤ PL LB ≤ 34 dBm;

fSS1 = f0 − 20 MHz; PSS1 = −40 dBm;

CG = PL CON − PSS1;

see fig. 4

f0 = 915 MHz for EGSM900;

f0 = 849 MHz for GSM850;

5 ≤ PL LB ≤ 34 dBm;

fSS2 = f0 + 20 MHz; PSS2 = −40 dBm;

SSG = PL SS2 − PSS2;

see fig. 5

5 ≤ PL LB ≤ 34 dBm;6.5 % AM modulation

with fmod = 67 kHz at RFin LB

5 ≤ PL LB ≤ 34 dBm;6.5 % AM modulation

with fmod = 140 kHz at RFin LB

5 ≤ PL LB ≤ 34 dBm;6.5 % AM modulation

with fmod = 271 kHz at RFin LB

−0.5 ≤ PD LB ≤ 0.5 dBm;

5 ≤ PL LB ≤ 34 dBm

5 ≤ PL LB ≤ 34 dBm

PL LB 5 dBm to 34 dBm or vice versa

PL LB ≤ 34 dBm; VSWR ≤ 8 : 1 through all

phases; 3.2 ≤ VBAT ≤ 4.6 V

3.2 ≤ VBAT ≤ 4.6 V; PL LB ≤ 34 dBm;

δ = 4 : 8; VSWR ≤ 8 : 1 through all

phases

−

−

−

−

−

−

−

−

−

−

−

−

−

− −73

− −82

− −77

− 28

− 31

8 12

12 15

18 20

−4

− 250

−2

200 −

− −36

no degradation

dBm

dBm

dBm

dB

dB

%

%

%

deg/dB

dB/V

µs

kHz

dBm

Note

1. Condition to set VDAC: VBAT = 3.6 V; δ = 2 : 8; PD LB = 0 dBm; Tmb = 25 °C; f = 897.5 MHz for EGSM900;

f = 836.5 MHz for GSM850

2. Conditions for power variation: −2 ≤ PD LB ≤ +2 dBm; f = 824 to 849 MHz for GSM850;

f = 880 to 915 MHz for EGSM900; 15 ≤ Tmb ≤ 70 °C; 3.2 ≤ VBAT ≤ 4.2 V; VSTAB = 2.8 V ± 10 mV

3. Conditions for power variation: −2 ≤ PD LB ≤ +2 dBm; f = 824 to 849 MHz for GSM850;

f = 880 to 915 MHz for EGSM900; −10 ≤ Tmb ≤ 90 °C; 3.2 ≤ VBAT ≤ 4.2 V; VSTAB = 2.8 V ± 10 mV

4. Conditions for power variation: PD LB = 0 dBm; f = 824 to 849 MHz for GSM850;

f = 880 to 915 MHz for EGSM900; Tmb = 25 °C; VBAT = 3.6 V; VSTAB = 2.8 V ± 10 mV

2003 Aug 20

11

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet BGY284.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| BGY280 | UHF amplifier module | NXP Semiconductors |

| BGY282 | dual band UHF amplifier module for GSM900 and GSM1800 | NXP Semiconductors |

| BGY284 | Power amplifier with integrated control loop | NXP Semiconductors |

| BGY288 | Power amplifier | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |