|

|

PDF XC17S00A Data sheet ( Hoja de datos )

| Número de pieza | XC17S00A | |

| Descripción | Spartan-II/Spartan-IIE Family OTP Configuration PROMs | |

| Fabricantes | Xilinx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XC17S00A (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

R

0

DS078 (v1.8) November 18, 2002

05

Features

• Configuration one-time programmable (OTP) read-only

memory designed to store configuration bitstreams for

Spartan-II/Spartan-IIE FPGA devices

• Simple interface to the Spartan device

• Programmable reset polarity (active High or active

Low)

• Low-power CMOS floating gate process

• 3.3V PROM

Spartan-II/Spartan-IIE Family

OTP Configuration PROMs

(XC17S00A)

Advance Product Specification

• Available in compact plastic 8-pin DIP, 8-pin VOIC,

20-pin SOIC, or 44-pin VQFP packages.

• Programming support by leading programmer

manufacturers.

• Design support using the Xilinx Alliance and

Foundation series software packages.

• Guaranteed 20-year life data retention

Introduction

The XC17S00A family of PROMs provide an easy-to-use,

cost-effective method for storing Spartan-II/Spartan-IIE

device configuration bitstreams.

When the Spartan device is in Master Serial mode, it

generates a configuration clock that drives the Spartan

PROM. A short access time after the rising clock edge, data

appears on the PROM DATA output pin that is connected to

the Spartan device DIN pin. The Spartan device generates

the appropriate number of clock pulses to complete the

configuration. Once configured, it disables the PROM.

When a Spartan device is in Slave Serial mode, the PROM

and the Spartan device must both be clocked by an

incoming signal.

For device programming, either the Xilinx Alliance or the

Spartan device design file into a standard HEX format

which is then transferred to most commercial PROM

programmers.

Spartan-II/IIE FPGA

Configuration Bits

Compatible Spartan-II/IIE PROM

XC2S15

197,696

XC17S15A

XC2S30

336,768

XC17S30A

XC2S50

559,200

XC17S50A

XC2S100

781,216

XC17S100A

XC2S150

1,040,096

XC17S150A

XC2S200

1,335,840

XC17S200A

XC2S50E

630,048

XC17S50A

XC2S100E

XC2S150E(1)

863,840

1,134,496

XC17S100A

XC17S200A

XC2S200E

1,442,016

XC17S200A

XC2S300E

XC2S400E

XC2S600E

1,875,648

2,693,440

3,961,632

XC17S300A

XC17V04(2)

XC17V04(2)

Notes:

1. Due to the higher configuration bit requirements of the XC2S150E device, an XC17S200A PROM is required to configure this FPGA.

2. See XC17V00 series configuration PROMs data sheet at: http://direct.xilinx.com/bvdocs/publications/ds073.pdf

© 2002 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and further disclaimers are as listed at http://www.xilinx.com/legal.htm. All other

trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

NOTICE OF DISCLAIMER: Xilinx is providing this design, code, or information "as is." By providing the design, code, or information as one possible implementation of this feature,

application, or standard, Xilinx makes no representation that this implementation is free from any claims of infringement. You are responsible for obtaining any rights you may

require for your implementation. Xilinx expressly disclaims any warranty whatsoever with respect to the adequacy of the implementation, including but not limited to any warranties

or representations that this implementation is free from claims of infringement and any implied warranties of merchantability or fitness for a particular purpose.

DS078 (v1.8) November 18, 2002

Advance Product Specification

www.xilinx.com

1-800-255-7778

1

1 page

R Spartan-II/Spartan-IIE Family OTP Configuration PROMs (XC17S00A)

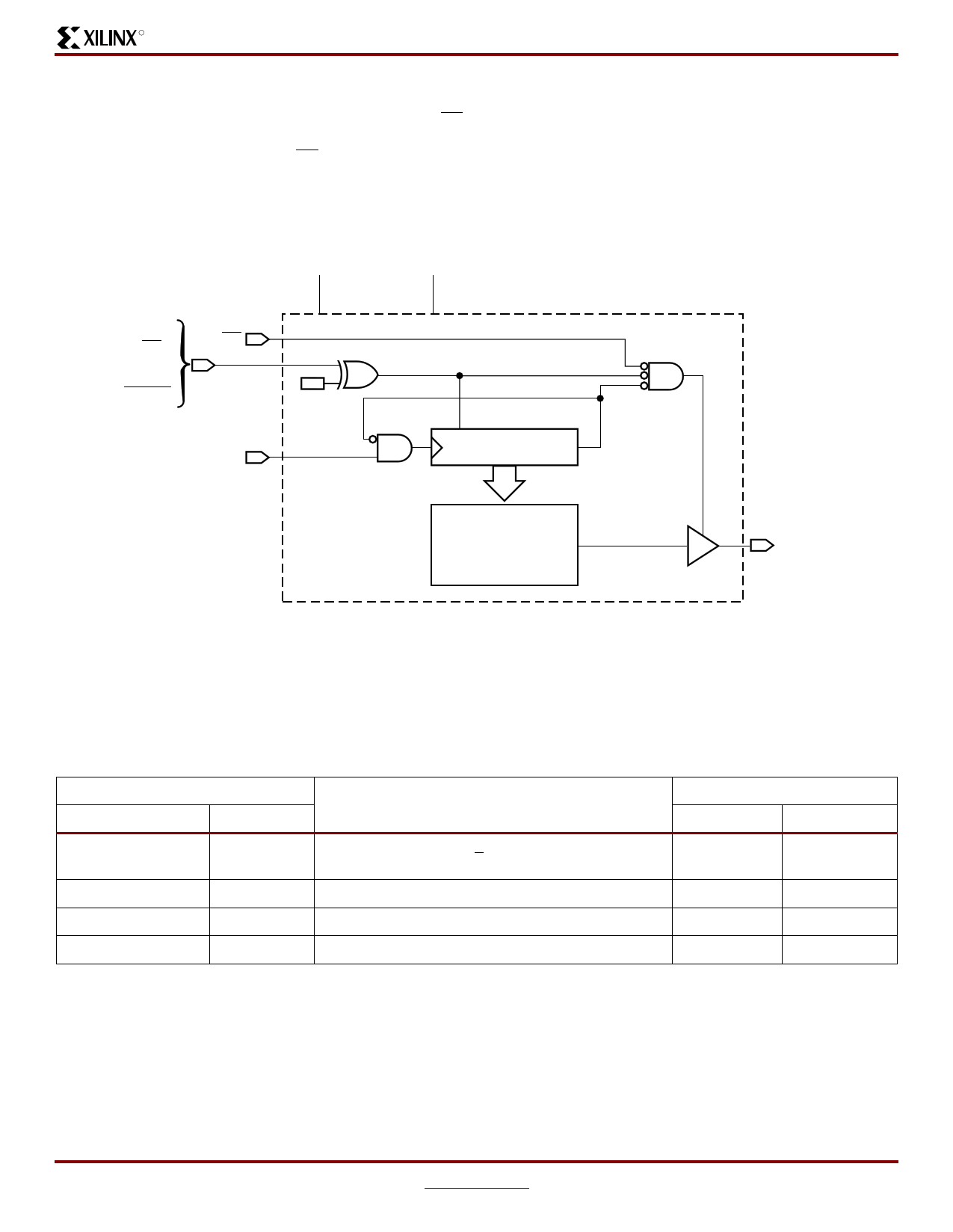

Standby Mode

The PROM enters a low-power standby mode whenever CE

is asserted High. The output remains in a high-impedance

state regardless of the state of the OE input.

Programming Spartan-II/Spartan-IIE

Family PROMs

The devices can be programmed on programmers supplied

by Xilinx or qualified third-party vendors. The user must

ensure that the appropriate programming algorithm and the

latest version of the programmer software are used. The

wrong choice can permanently damage the device.

VCC

GND

RESET/

OE

or

OE/

RESET

CE

CLK

Address Counter

TC

EPROM

Cell

Matrix

Output

OE

DATA

DS030_02_011300

Figure 2: Simplified Block Diagram (does not show programming circuit)

Important: Always tie the two VCC pins together in your application.

Table 2: Truth Table for XC17S00A Control Inputs

Control Inputs

RESET(1)

CE

Internal Address(2)

Inactive

Low

If address < TC: increment

If address > TC: don’t change

Active

Low

Held reset

Inactive

High

Not changing

Active

High

Held reset

Notes:

1. The XC17S00A RESET input has programmable polarity

2. TC = Terminal Count = highest address value. TC + 1 = address 0.

Outputs

DATA

Active

High-Z

ICC

Active

Reduced

High-Z

Active

High-Z

Standby

High-Z

Standby

DS078 (v1.8) November 18, 2002

Advance Product Specification

www.xilinx.com

1-800-255-7778

5

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet XC17S00A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XC17S00 | Spartan Family of One-Time Programmable Configuration PROMs | Xilinx |

| XC17S00A | Spartan-II/Spartan-IIE Family OTP Configuration PROMs | Xilinx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |