|

|

PDF SC18IS600 Data sheet ( Hoja de datos )

| Número de pieza | SC18IS600 | |

| Descripción | (SC18IS600 / SC18IS601) SPI to IC-bus interface | |

| Fabricantes | NXP Semiconductors | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de SC18IS600 (archivo pdf) en la parte inferior de esta página. Total 28 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

SC18IS600/601

SPI to I2C-bus interface

Rev. 03 — 13 December 2006

Product data sheet

1. General description

The SC18IS600/601 is designed to serve as an interface between the standard SPI of a

host (microcontroller, microprocessor, chip set, etc.) and the serial I2C-bus. This allows

the host to communicate directly with other I2C-bus devices. The SC18IS600/601 can

operate as an I2C-bus master-transmitter or master-receiver. The SC18IS600/601

controls all the I2C-bus specific sequences, protocol, arbitration and timing.

The key distinction between the SC18IS600 and the SC18IS601 lies in the clock source:

internal (SC18IS600) versus external (SC18IS601).

2. Features

I SPI slave interface

I SPI Mode 3

I Master I2C-bus controller

I General Purpose Input/Output (GPIO) pins: 4 (SC18IS600); 3 (SC18IS601)

I Two quasi-bidirectional I/O pins

I 5 V tolerant I/O pins

I High-speed SPI:

N Up to 3 Mbit/s (SC18IS601)

N Up to 1.2 Mbit/s (SC18IS600)

I High-speed I2C-bus: 400 kbit/s

I 96-byte transmit buffer

I 96-byte receive buffer

I 2.4 V to 3.6 V operation

I Power-down mode with WAKEUP pin

I Oscillator: internal (SC18IS600); external (SC18IS601)

I Active LOW interrupt output

I Available in very small TSSOP16 package

3. Ordering information

Table 1. Ordering information

Type number Package

Name

Description

SC18IS600IPW TSSOP16 plastic thin shrink small outline package; 16 leads;

SC18IS601IPW

body width 4.4 mm

Version

SOT403-1

1 page

NXP Semiconductors

SC18IS600/601

SPI to I2C-bus interface

6. Functional description

The SC18IS600/601 acts as a bridge between a SPI interface and an I2C-bus. It allows a

SPI master device to communicate with I2C-bus slave devices. The SPI interface supports

Mode 3 of the SPI specification and can operate up to 3 Mbit/s (SC18IS601).

6.1 Internal registers

The SC18IS600/601 provides internal registers for monitoring and control. These

registers are shown in Table 3. Register functions are more fully described in the following

paragraphs.

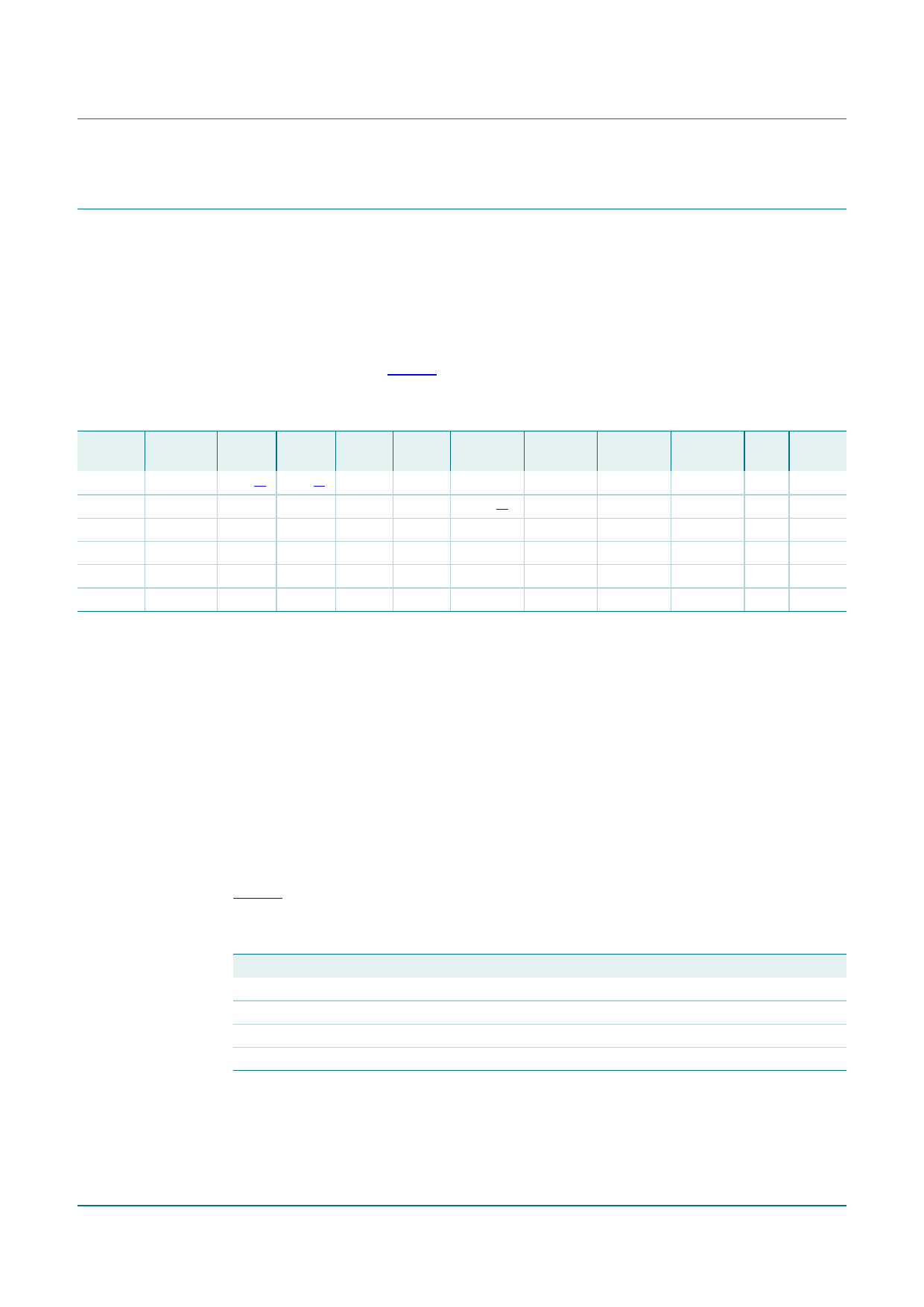

Table 3. Internal registers summary

Register Register Bit 7

address

Bit 6

Bit 5

0x00

IOConfig IO3.1[1] IO3.0[1] IO2.1

0x01

IOState 0

0

GPIO5

0x02

I2CClock CR7 CR6 CR5

0x03

I2CTO TO6 TO5 TO4

0x04

I2CStat 1

1

1

0x05

I2CAdr ADR7 ADR6 ADR5

Bit 4

IO2.0

GPIO4

CR4

TO3

1

ADR4

Bit 3

Bit 2

Bit 1

Bit 0

R/W

IO1.1

IO1.0

IO0.1

IO0.0

R/W

GPIO3[2] GPIO2 GPIO1 GPIO0 R/W

CR3

CR2

CR1

CR0

R/W

TO2 TO1 TO0 TE

R/W

I2CSTAT3 I2CSTAT2 I2CSTAT1 I2CSTAT0 R

ADR3

ADR2

ADR1

X

R/W

Default

value

0x00

0x3F

0x19

0xFE

0xF0

0x00

[1] For SC18IS601, these bits are ‘Don’t care’.

[2] For SC18IS601 GPIO3 is not used.

6.2 Register descriptions

6.2.1 Programmable IO port configuration register (IOConfig)

Pins GPIO0 to GPIO3 may be configured by software to one of four types. These are:

quasi-bidirectional, push-pull, open-drain, and input-only. Two configuration bits per pin,

located in the IOConfig register, select the IO type for each pin. Each pin has

Schmitt-triggered input that also has a glitch suppression circuit. IO4 and IO5 are

quasi-bidirectional pins and are not user-configurable. For SC18IS601, GPIO3 is

non-existent.

Table 4 shows the configurations for the programmable I/O pins. IOx.1 and IOx.0

correspond to GPIOx.

Table 4.

IOx.1

0

0

1

1

Pin configurations

IOx.0

Pin configuration

0 quasi-bidirectional output configuration

1 input-only configuration

0 push-pull output configuration

1 open-drain output configuration

SC18IS600_601_3

Product data sheet

Rev. 03 — 13 December 2006

© NXP B.V. 2006. All rights reserved.

5 of 28

5 Page

NXP Semiconductors

SC18IS600/601

SPI to I2C-bus interface

6.3 External clock input (SC18IS601)

In this device, the processor clock is derived from an external source driving the CLKIN

pin. The clock rate may be from 0 Hz up to 18 MHz.

6.4 I2C-bus serial interface

I2C-bus uses two wires (SDA and SCL) to transfer information between devices connected

to the bus, and it has the following features:

• Bidirectional data transfer between masters and slaves

• Multi-master bus (no central master)

• Arbitration between simultaneously transmitting masters without corruption of serial

data on the bus

• Serial clock synchronization allows devices with different bit rates to communicate via

one serial bus

• Serial clock synchronization can be used as a handshake mechanism to suspend and

resume serial transfer

• The I2C-bus may be used for test and diagnostic purposes.

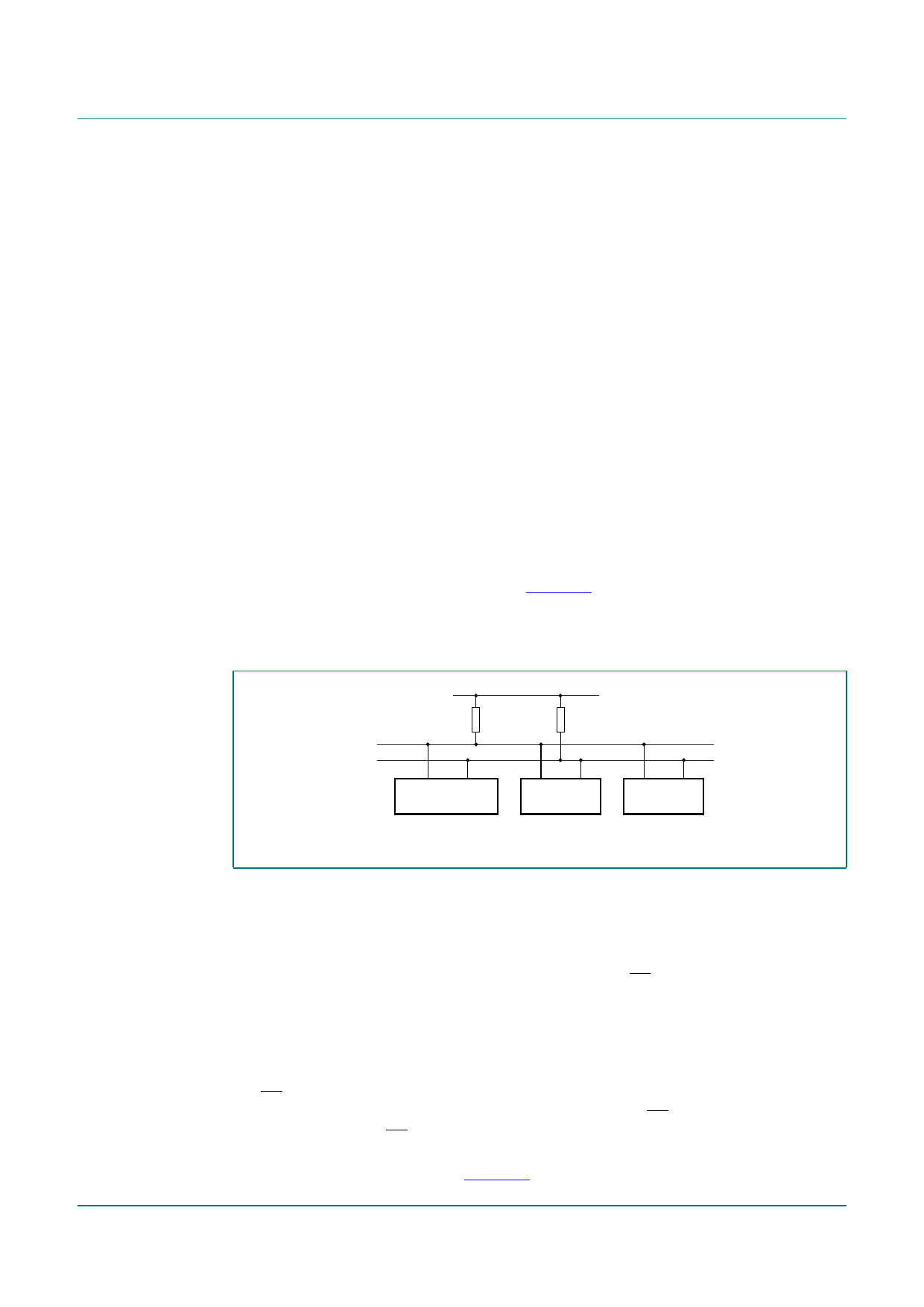

A typical I2C-bus configuration is shown in Figure 10. The SC18IS600/601 device

provides a byte-oriented I2C-bus interface that supports data transfers up to 400 kHz.

(Refer to Philips Semiconductors The I2C-bus specification, document order number

9398 393 40011.)

I2C-bus

VDD

RPU

SC18IS600/601

RPU

I2C-BUS

DEVICE

Fig 10. I2C-bus configuration

SDA

SCL

I2C-BUS

DEVICE

002aab716

6.5 Serial Peripheral Interface (SPI)

The host communicates with the SC18IS600/601 via the SPI interface. The

SC18IS600/601 operates in Slave mode up to 3 Mbit/s.

The SPI interface has four pins: SCLK, MOSI, MISO, and CS.

• SCLK, MOSI and MISO are typically tied together between two or more SPI devices.

Data flows from the master to the SC18IS600/601 on the MOSI (Master Out Slave In)

pin and flows from SC18IS600/601 to the master on the MISO (Master In Slave Out)

pin. The SCLK signal is an input to the SC18IS600/601.

• CS is the slave select pin. In a typical configuration, an SPI master selects one SPI

device as the current slave. An SPI slave device uses its CS pin to determine whether

it is selected. The CS pin may be tied LOW if it is the only device on the bus.

Typical connections are shown in Figure 11.

SC18IS600_601_3

Product data sheet

Rev. 03 — 13 December 2006

© NXP B.V. 2006. All rights reserved.

11 of 28

11 Page | ||

| Páginas | Total 28 Páginas | |

| PDF Descargar | [ Datasheet SC18IS600.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SC18IS600 | (SC18IS600 / SC18IS601) SPI to IC-bus interface | NXP Semiconductors |

| SC18IS601 | (SC18IS600 / SC18IS601) SPI to IC-bus interface | NXP Semiconductors |

| SC18IS602 | I2C-bus to SPI bridge | NXP Semiconductors |

| SC18IS602B | I2C-bus to SPI bridge | NXP Semiconductors |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |