|

|

PDF W942508CH Data sheet ( Hoja de datos )

| Número de pieza | W942508CH | |

| Descripción | DDR SDRAM | |

| Fabricantes | Winbond | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de W942508CH (archivo pdf) en la parte inferior de esta página. Total 47 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

W942508CH

8M × 4 BANKS × 8 BIT DDR SDRAM

Table of Contents-

1. GENERAL DESCRIPTION .................................................................................................. 3

2. FEATURES .......................................................................................................................... 3

3. KEY PARAMETERS ............................................................................................................ 4

4. PIN CONFIGURATION ........................................................................................................ 5

5. PIN DESCRIPTION.............................................................................................................. 6

6. BLOCK DIAGRAM ............................................................................................................... 7

7. ELECTRICAL CHARACTERISTICS .................................................................................... 8

7.1 Absolute Maximum Ratings ................................................................................................. 8

7.2 Recommended DC Operating Conditions............................................................................ 8

7.3 Capacitance ......................................................................................................................... 9

7.4 Leakage and Output Buffer Characteristics ......................................................................... 9

7.5 DC Characteristics ............................................................................................................. 10

7.6 AC Characteristics and Operating Condition ..................................................................... 11

7.7 AC Test Conditions ............................................................................................................ 13

8. Operation Mode ................................................................................................................. 15

8.1 Simplified Truth Table ........................................................................................................ 15

8.2 Function Truth Table .......................................................................................................... 16

8.3 Function Truth Table for CKE ............................................................................................ 19

8.4 Simplified State Diagram.................................................................................................... 20

9. FUNCTIONAL DESCRIPTION........................................................................................... 21

9.1 Power Up Sequence .......................................................................................................... 21

9.2 Command Function............................................................................................................ 21

9.3 Read Operation.................................................................................................................. 24

9.4 Write Operation .................................................................................................................. 24

9.5 Precharge........................................................................................................................... 24

9.6 Burst Termination............................................................................................................... 25

9.7 Refresh Operation.............................................................................................................. 25

9.8 Power Down Mode............................................................................................................. 25

9.9 Mode Register Operation ................................................................................................... 25

10. TIMING WAVEFORMS ............................................................................................................. 29

10.1 Command Input Timing...................................................................................................... 29

10.2 Timing of the CLK Signals.................................................................................................. 29

10.3 Read Timing (Burst Length = 4) ......................................................................................... 30

10.4 Write Timing (Burst Length = 4) ......................................................................................... 31

10.5 DM, DATA MASK (W942508CH/W942504CH) ................................................................. 32

Publication Release Date: May 21, 2003

- 1 - Revision A3

1 page

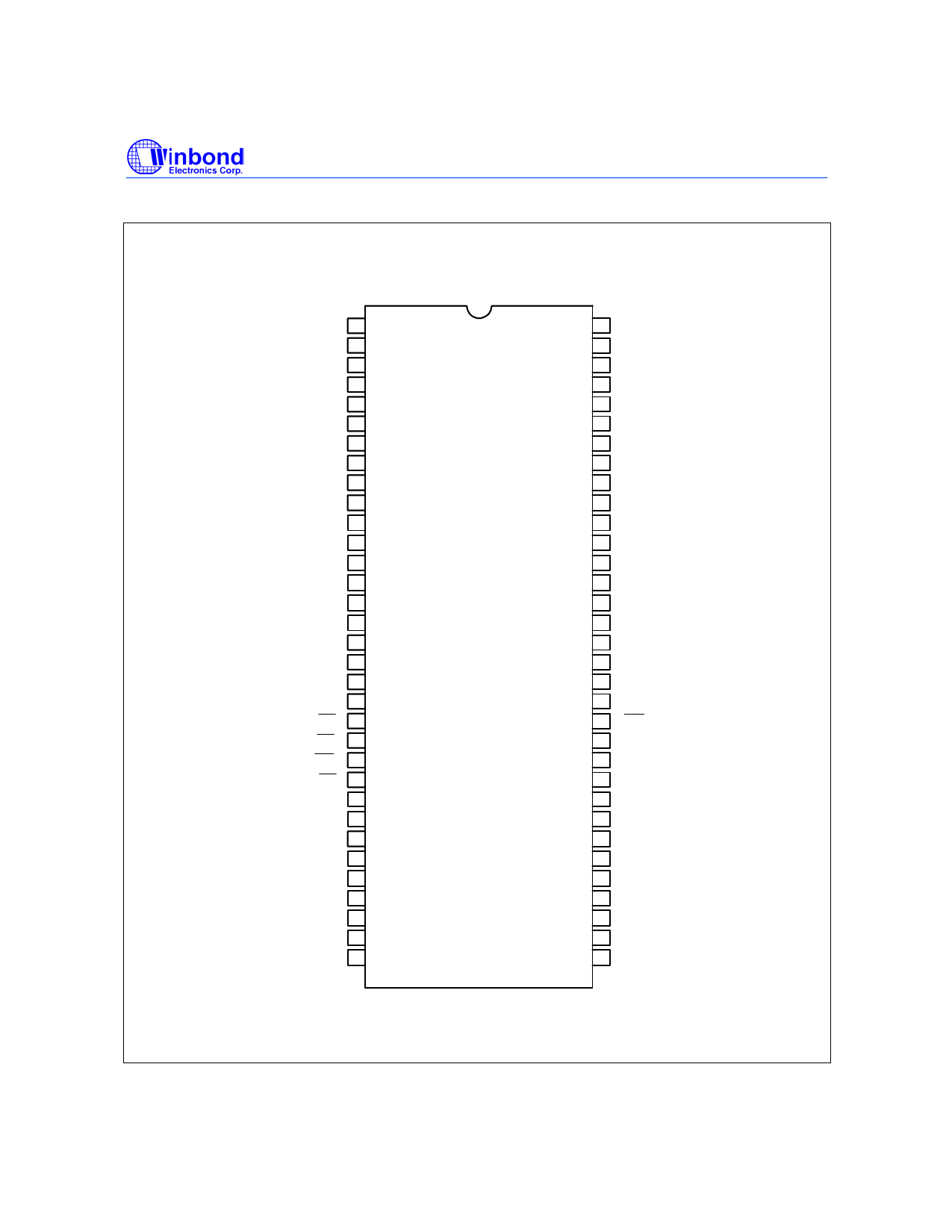

4. PIN CONFIGURATION

VDD

DQ0

VDDQ

NC2

DQ1

VSSQ

NC2

DQ2

VDDQ

NC2

DQ3

VSSQ

NC2

NC1

VDDQ

NC2

NC1

VDD

NC1

NC2

WE

CAS

RAS

CS

NC1

BS0

BS1

A10/AP

A0

A1

A2

A3

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

W942508CH

66 VSS

65 DQ7

64 VSSQ

63 NC2

62 DQ6

61 VDDQ

60 NC2

59 DQ5

58 VSSQ

57 NC2

56 DQ4

55 VDDQ

54 NC2

53 NC1

52 VSSQ

51 DQS

50 NC1

49 VREF

48 VSS

47 DM

46 CLK

45 CLK

44 CKE

43 NC1

42 A12

41 A11

40 A9

39 A8

38 A7

37 A6

36 A5

35 A4

34 VSS

Publication Release Date: May 21, 2003

- 5 - Revision A3

5 Page

W942508CH

7.6 AC Characteristics and Operating Condition

(Notes: 10, 12)

SYM.

tRC

tRFC

tRAS

tRCD

tRAP

tCCD

tRP

tRRD

tWR

tDAL

tCK

PARAMETER

Active to Ref/Active Command Period

Ref to Ref/Active Command Period

Active to Precharge Command Period

Active to Read/Write Command Delay Time

Active to Read with Auto Precharge Enable

Read/Write(a) to Read/Write(b) Command Period

Precharge to Active Command Period

Active(a) to Active(b) Command Period

Write Recovery Time

Auto Precharge Write Recovery + Precharge Time

CLK Cycle Time

CL = 2

CL = 2.5

-7

MIN. MAX.

65

75

45 100000

20

15

1

20

15

15

30

7.5 15

7 15

tAC Data Access Time from CLK, CLK

-0.75 0.75

tDQSCK

tDQSQ

tCH

tCL

tHP

tQH

tRPRE

tRPST

tDS

tDH

tDIPW

tDQSH

tDQSL

tDSS

tDSH

tWPRES

tWPRE

tWPST

tDQSS

tDSSK

tIS

tIH

tIPW

tHZ

DQS Output Access Time from CLK, CLK

Data Strobe Edge to Output Data Edge Skew

CLk High Level Width

CLK Low Level Width

CLK Half Period (minimum of actual tCH, tCL)

DQ Output Data Hold Time from DQS

DQS Read Preamble Time

DQS Read Postamble Time

DQ and DM Setup Time

DQ and DM Hold Time

DQ and DM Input Pulse Width (for each input)

DQS Input High Pulse Width

DQS Input Low Pulse Width

DQS Falling Edge to CLK Setup Time

DQS Falling Edge Hold Time from CLK

Clock to DQS Write Preamble Set-up Time

DQS Write Preamble Time

DQS Write Postamble Time

Write Command to First DQS Latching Transition

UDQS – LDQS Skew (x 16)

Input Setup Time

Input Hold Time

Control & Address Input Pulse Width (for each input)

Data-out High-impedance Time from CLK, CLK

-0.75

0.45

0.45

Min.

(tCL,tCH)

THP

-0.75

0.9

0.4

0.5

0.5

1.75

0.35

0.35

0.2

0.2

0

0.25

0.4

0.75

-0.25

0.9

0.9

2.2

-0.75

0.75

0.5

0.55

0.55

1.1

0.6

1.25

0.25

0.75

tLZ

tT(SS)

tWTR

tXSNR

tXSRD

tREF

tMRD

Data-out Low-impedance Time from CLK, CLK

SSTL Input Transition

Internal Write to Read Command Delay

Exit Self Refresh to non-Read Command

Exit Self Refresh to Read Command

Refresh Time (8k)

Mode Register Set Cycle Time

-0.75

0.5

1

75

10

15

0.75

1.5

64

-75

MIN.

65

75

45

20

15

1

20

15

15

30

8

7.5

MAX.

100000

15

15

-0.75 0.75

-0.75

0.45

0.45

Min.

(tCL,tCH)

THP

-0.75

0.9

0.4

0.5

0.5

1.75

0.35

0.35

0.2

0.2

0

0.25

0.4

0.75

-0.25

0.9

0.9

2.2

-0.75

0.75

0.5

0.55

0.55

1.1

0.6

1.25

0.25

0.75

-0.75

0.5

1

75

10

15

0.75

1.5

64

UNITS NOTES

nS

tCK

nS

16

tCK 11

nS

tCK 11

nS

tCK 11

nS

tCK 11

nS

tCK

ns

tCK

mS

nS

- 11 -

Publication Release Date: May 21, 2003

Revision A3

11 Page | ||

| Páginas | Total 47 Páginas | |

| PDF Descargar | [ Datasheet W942508CH.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| W942508CH | DDR SDRAM | Winbond |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |