|

|

PDF IDT72T40118 Data sheet ( Hoja de datos )

| Número de pieza | IDT72T40118 | |

| Descripción | (IDT72T40xxx) 2.5 VOLT HIGH-SPEED TeraSync DDR/SDR FIFO 40-BIT CONFIGURATION | |

| Fabricantes | Integrated Device Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de IDT72T40118 (archivo pdf) en la parte inferior de esta página. Total 52 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

2.5 VOLT HIGH-SPEED TeraSync™ DDR/SDR FIFO 40-BIT CONFIGURATION

16,384 x 40, 32,768 x 40,

65,536 x 40, 131,072 x 40

IDT72T4088, IDT72T4098

IDT72T40108, IDT72T40118

FEATURES

• Choose among the following memory organizations:

IDT72T4088 16,384 x 40

IDT72T4098 32,768 x 40

IDT72T40108 65,536 x 40

IDT72T40118 131,072 x 40

• Up to 250MHz Operation of Clocks

- 4ns read/write cycle time, 3.2ns access time

• Users selectable input port to output port data rates, 500Mb/s

Data Rate

-DDR to DDR

-DDR to SDR

-SDR to DDR

-SDR to SDR

• User selectable HSTL or LVTTL I/Os

• Read Enable & Read Clock Echo outputs aid high speed operation

• 2.5V LVTTL or 1.8V, 1.5V HSTL Port Selectable Input/Ouput voltage

• 3.3V Input tolerant

• Mark & Retransmit, resets read pointer to user marked position

• Write Chip Select (WCS) input enables/disables Write

Operations

• Read Chip Select (RCS) synchronous to RCLK

• Programmable Almost-Empty and Almost-Full flags, each flag

can default to one of four preselected offsets

• Dedicated serial clock input for serial programming of flag offsets

• User selectable input and output port bus sizing

-x40 in to x40 out

-x40 in to x20 out

-x40 in to x10 out

-x20 in to x40 out

-x10 in to x40 out

• Auto power down minimizes standby power consumption

• Master Reset clears entire FIFO

• Partial Reset clears data, but retains programmable settings

• Empty and Full flags signal FIFO status

• Select IDT Standard timing (using EF and FF flags) or First

Word Fall Through timing (using OR and IR flags)

• Output enable puts data outputs into High-Impedance state

• JTAG port, provided for Boundary Scan function

• 208 Ball Grid array (PBGA), 17mm x 17mm, 1mm pitch

• Easily expandable in depth and width

• Independent Read and Write Clocks (permit reading and writing

simultaneously)

• High-performance submicron CMOS technology

• Industrial temperature range (-40°C to +85°C) is available

FUNCTIONAL BLOCK DIAGRAM

WEN

WCLK

D0 -Dn (x40, x20, x10)

SREN SEN SCLK

WCS WSDR

INPUT REGISTER

OFFSET REGISTER

SI

SO

WRITE CONTROL

LOGIC

WRITE POINTER

RAM ARRAY

16,384 x 40,

32,768 x 40

65,536 x 40

131,072 x 40

FLAG

LOGIC

READ POINTER

FF/IR

PAF

EF/OR

PAE

FWFT

FSEL0

FSEL1

BM

IW

OW

MRS

PRS

TCK

TRST

TMS

TDO

TDI

BUS

CONFIGURATION

RESET

LOGIC

JTAG CONTROL

(BOUNDARY SCAN)

OUTPUT REGISTER

READ

CONTROL

LOGIC

Vref

HSTL

HSTL I/0

CONTROL

OE

Q0 -Qn (x40, x20, x10)

EREN

ERCLK

IDT and the IDT logo are registered trademarks of Integrated Device Technology, Inc. The TeraSync is a trademark of Integrated Device Technology, Inc.

COMMERCIAL AND INDUSTRIAL TEMPERATURE RANGES

1

2003 Integrated Device Technology, Inc. All rights reserved. Product specifications subject to change without notice.

RT

MARK

RSDR

RCLK

REN

RCS

5995 drw01

DECEMBER 2003

DSC-5995/8

1 page

IDT72T4088/98/108/118 2.5V HIGH-SPEED TeraSync™ DDR/SDR FIFO 40-BIT

CONFIGURATION 16,384 x 40, 32,768 x 40, 65,536 x 40 and 131,072 x 40

PARTIAL RESET (PRS) MASTER RESET (MRS)

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

WRITE CLOCK (WCLK)

WRITE ENABLE (WEN)

WRITE CHIP SELECT (WCS)

WRITE SINGLE DATA RATE (WSDR)

(x40, x20, x10) DATA IN (D0 - Dn)

SERIAL CLOCK (SCLK)

SERIAL ENABLE(SEN)

SERIAL READ ENABLE(SREN)

FIRST WORD FALL THROUGH (FWFT)

SERIAL INPUT (SI)

SERIAL OUTPUT (SO)

FULL FLAG/INPUT READY (FF/IR)

PROGRAMMABLE ALMOST-FULL (PAF)

IDT

72T4088

72T4098

72T40108

72T40118

READ CLOCK (RCLK)

READ ENABLE (REN)

OUTPUT ENABLE (OE)

READ CHIP SELECT (RCS)

READ SINGLE DATA RATE (RSDR)

(x40, x20, x10) DATA OUT (Q0 - Qn)

RCLK ECHO (ERCLK)

REN ECHO (EREN)

MARK

RETRANSMIT (RT)

EMPTY FLAG/OUTPUT READY (EF/OR)

PROGRAMMABLE ALMOST-EMPTY (PAE)

INPUT WIDTH (IW) OUTPUT WIDTH (OW)

5995 drw03

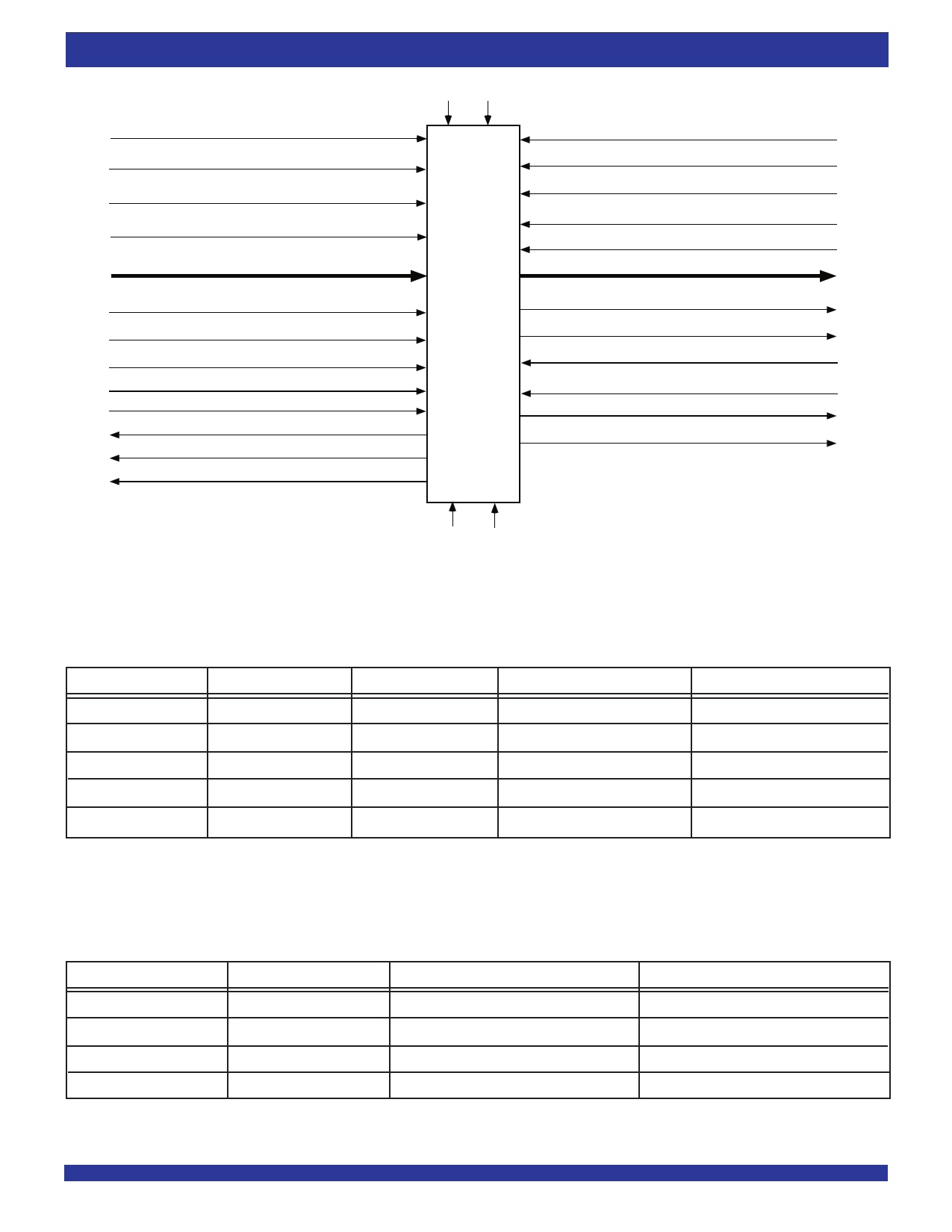

Figure 1. Single Device Configuration Signal Flow Diagram

TABLE 1 — BUS-MATCHING CONFIGURATION MODES

BM I W OW Write Port Width

LL

HL

HL

HH

HH

L

L

H

L

H

x40

x40

x40

x20

x10

NOTE:

1. Pin status during Master Reset.

Read Port Width

x40

x20

x10

x40

x40

TABLE 2 — DATA RATE-MATCHING CONFIGURATION MODES

WSDR

RSDR

Write Port Width

Read Port Width

HH

HL

LH

LL

NOTE:

1. Pin status during Master Reset.

2. Data Rate Matching can be used in conjunction with Bus-Matching modes.

Double Data Rate

Double Data Rate

Single Data Rate

Single Data Rate

Double Data Rate

Single Data Rate

Double Data Rate

Single Data Rate

5

5 Page

IDT72T4088/98/108/118 2.5V HIGH-SPEED TeraSync™ DDR/SDR FIFO 40-BIT

CONFIGURATION 16,384 x 40, 32,768 x 40, 65,536 x 40 and 131,072 x 40

HSTL

1.5V AC TEST CONDITIONS

Input Pulse Levels

Input Rise/Fall Times

Input Timing Reference Levels

Output Reference Levels

0.25 to 1.25V

0.4ns

0.75

VDDQ/2

I/O

NOTE:

1. VDDQ = 1.5V±.

COMMERCIAL AND INDUSTRIAL

TEMPERATURE RANGES

AC TEST LOADS

VDDQ/2

50Ω

Z0 = 50Ω

5995 drw04

Figure 2a. AC Test Load

EXTENDED HSTL

1.8V AC TEST CONDITIONS

Input Pulse Levels

Input Rise/Fall Times

Input Timing Reference Levels

Output Reference Levels

0.4 to 1.4V

0.4ns

0.9

VDDQ/2

NOTE:

1. VDDQ = 1.8V±.

2.5V LVTTL

2.5V AC TEST CONDITIONS

Input Pulse Levels

Input Rise/Fall Times

Input Timing Reference Levels

Output Reference Levels

GND to 2.5V

1ns

VCC/2

VDDQ/2

NOTE:

1. For LVTTL VCC = VDDQ.

6

5

4

3

2

1

20 30 50 80 100

Capacitance (pF)

200

5995 drw04a

Figure 2b. Lumped Capacitive Load, Typical Derating

11

11 Page | ||

| Páginas | Total 52 Páginas | |

| PDF Descargar | [ Datasheet IDT72T40118.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| IDT72T40118 | (IDT72T40xxx) 2.5 VOLT HIGH-SPEED TeraSync DDR/SDR FIFO 40-BIT CONFIGURATION | Integrated Device Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |