|

|

PDF LC5256MC Data sheet ( Hoja de datos )

| Número de pieza | LC5256MC | |

| Descripción | In-System Programmable eXpanded Programmable Logic Device | |

| Fabricantes | Lattice Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de LC5256MC (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

ispXPLDTM 5000MX Family

3.3V, 2.5V and 1.8V In-System Programmable

eXpanded Programmable Logic Device XPLD™ Family

August 2004

Data Sheet

Features

■ Flexible Multi-Function Block (MFB)

Architecture

• SuperWIDE™ logic (up to 136 inputs)

• Arithmetic capability

• Single- or Dual-port SRAM

• FIFO

• Ternary CAM

■ sysCLOCK™ PLL Timing Control

• Multiply and divide between 1 and 32

• Clock shifting capability

• External feedback capability

■ sysIO™ Interfaces

• LVCMOS 1.8, 2.5, 3.3V

– Programmable impedance

– Hot-socketing

– Flexible bus-maintenance (Pull-up, pull-

down, bus-keeper, or none)

– Open drain operation

• SSTL 2, 3 (I & II)

• HSTL (I, III, IV)

• PCI 3.3

• GTL+

• LVDS

• LVPECL

• LVTTL

Table 1. ispXPLD 5000MX Family Selection Guide

■ Expanded In-System Programmability (ispXP™)

• Instant-on capability

• Single chip convenience

• In-System Programmable via IEEE 1532

Interface

• Infinitely reconfigurable via IEEE 1532 or

sysCONFIG™ microprocessor interface

• Design security

■ High Speed Operation

• 4.0ns pin-to-pin delays, 300MHz fMAX

• Deterministic timing

■ Low Power Consumption

• Typical static power: 20 to 50mA (1.8V),

30 to 60mA (2.5/3.3V)

• 1.8V core for low dynamic power

■ Easy System Integration

• 3.3V (5000MV), 2.5V (5000MB) and 1.8V

(5000MC) power supply operation

• 5V tolerant I/O for LVCMOS 3.3 and LVTTL

interfaces

• IEEE 1149.1 interface for boundary scan testing

• sysIO quick configuration

• Density migration

• Multiple density and package options

• PQFP and fine pitch BGA packaging

• Lead-free package options

Macrocells

Multi-Function Blocks

Maximum RAM Bits

Maximum CAM Bits

sysCLOCK PLLs

tPD (Propagation Delay)

tS (Register Set-up Time)

tCO (Register Clock to Out Time)

fMAX (Maximum Operating Frequency)

System Gates

I/Os

Packages

ispXPLD 5256MX

256

8

128K

48K

2

4.0ns

2.2ns

2.8ns

300MHz

75K

141

256 fpBGA

ispXPLD 5512MX

512

16

256K

96K

2

4.5ns

2.8ns

3.0ns

275MHz

150K

149/193/253

208 PQFP

256 fpBGA

484 fpBGA

ispXPLD 5768MX ispXPLD 51024MX

768 1,024

24 32

384K

512K

144K

192K

22

5.0ns

5.2ns

2.8ns

3.0ns

3.2ns

3.7ns

250MHz

250MHz

225K

300K

193/317

317/381

256 fpBGA

484 fpBGA

484 fpBGA

672 fpBGA

© 2004 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

www.latticesemi.com

1

5kmx_10

DataSheet4 U .com

1 page

www.DataSheet4U.com

Lattice Semiconductor

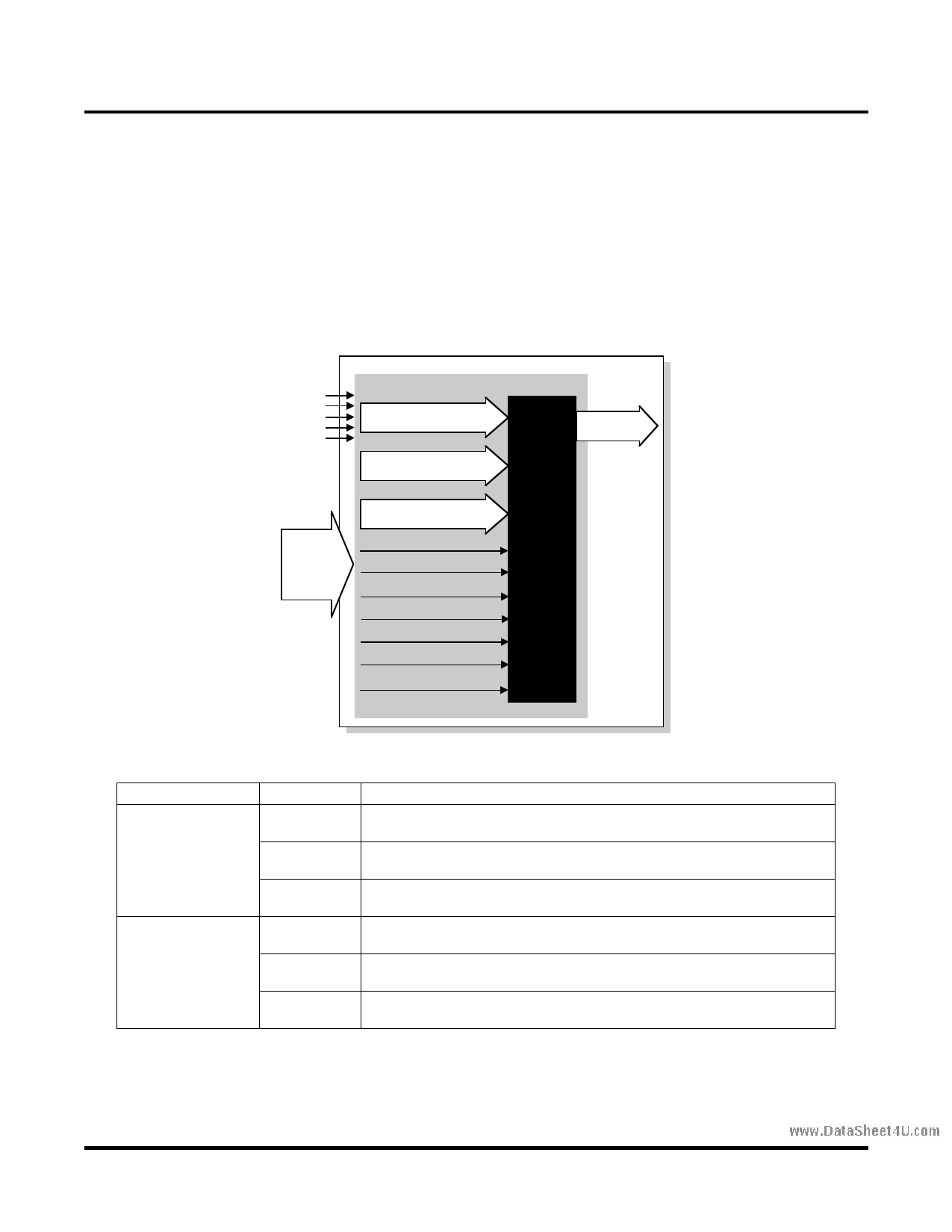

Figure 3. MFB in SuperWIDE Logic Mode

ispXPLD 5000MX Family Data Sheet

To Routing

68 Inputs

from

Routing

68 Inputs

from

Adjacent

MFB

Shared PT Clk

Shared PT Clk En

Shared PT Reset

Carry Out

Figure 4. Macrocell Slice in Logic Mode AND-Array

From

GRP

From Carry-in

n-7

PTOE

Sharing

68

AND Array

PTSA Bypass

PTSA

PT Clock

Shared

PT CE

Dual-OR Array

Shared PTCLK

CLK0

CLK1

CLK2

CLK3

PT Preset

PT Reset

Shared PT Reset

Global Reset

To Carry-out

n+7

DQ

Clk En

R/L

Clk

PR

Macrocell

DataSheet4 U .com

5

PT OE to

I/O Block

From

I/O Cell

Output

to I/O Block

GRP

5 Page

www.DataSheet4U.com

Lattice Semiconductor

ispXPLD 5000MX Family Data Sheet

Pseudo Dual-Port SRAM Mode

In Pseudo Dual-Port SRAM Mode the multi-function array is configured as a SRAM with an independent read and

write ports that access the same 16,384-bits of memory. Data widths of 1, 2, 4, 8, 16 and 32 are supported by the

MFB. Figure 10 shows the block diagram of the Pseudo Dual-Port SRAM.

Write data, write address, chip select and write enable signals are always synchronous (registered). The read data

and read address signals can be synchronous or asynchronous. Reset is asynchronous. All write signals share the

same clock, and clock enable. All read signals share the same clock and clock enable. Reset is shared by both

read and write signals. Table 6 shows the possible sources for the clock, clock enable and initialization signals for

the various registers.

Figure 10. Pseudo Dual-Port SRAM Block Diagram

CLK0

CLK1

CLK2

CLK3

RESET

Read Address

(RAD[0:8-13])

Write Address

(WAD[0:8-13])

Read Data

(RD[0:0-15])

68 Inputs

From

Routing

Write Data

(WD[0:0,1,3,7,15,31])

16,384 bit

Pseudo

Write Enable (WE)

Write Clock (WCLK)

‘ ‘ Dual

Port

SRAM

Write Chip Sel (WCS[0,1]) Array

Write Clk Enable (WCEN)

Read Clk Enable (RCEN)

Read Clock (RCLK)

Reset (RST)

Table 6. Register Clock, Clock Enable, and Reset in Pseudo Dual-Port SRAM Mode

Register

Input

Clock

Write Address, Write

Data, Write Enable,

Clock Enable

and Write Chip Select

Reset

Clock

Read Data and Read Clock Enable

Address

Reset

Source

WCLK or one of the global clocks (CLK0 - CLK3). The selected signal can

be inverted if desired.

WCEN or one of the global clocks (CLK1 - CLK2). The selected signal can

be inverted if desired.

Created by the logical OR of the global reset signal and RST. RST may have

inversion if desired.

RCLK or one of the global clocks (CLK0 - CLK3). The selected signal can be

inverted if desired.

RCEN or one of the global clocks (CLK1 - CLK2). The selected signal can

be inverted if desired.

Created by the logical OR of the global reset signal and RST. RST may have

inversion if desired.

DataSheet4 U .com

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet LC5256MC.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LC5256MC | In-System Programmable eXpanded Programmable Logic Device | Lattice Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |