|

|

PDF EPF6016 Data sheet ( Hoja de datos )

| Número de pieza | EPF6016 | |

| Descripción | (EPF6000 Series) Programmable Logic Device | |

| Fabricantes | Altera Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de EPF6016 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

March 2001, ver. 4.1

®

FLEX 6000

Programmable Logic

Device Family

Data Sheet

Features...

s Provides an ideal low-cost, programmable alternative to high-

volume gate array applications and allows fast design changes

during prototyping or design testing

s Product features

– Register-rich, look-up table- (LUT-) based architecture

– OptiFLEX® architecture that increases device area efficiency

– Typical gates ranging from 5,000 to 24,000 gates (see Table 1)

– Built-in low-skew clock distribution tree

– 100% functional testing of all devices; test vectors or scan chains

are not required

s System-level features

– In-circuit reconfigurability (ICR) via external configuration

device or intelligent controller

– 5.0-V devices are fully compliant with peripheral component

interconnect Special Interest Group (PCI SIG) PCI Local Bus

Specification, Revision 2.2

– Built-in Joint Test Action Group (JTAG) boundary-scan test

(BST) circuitry compliant with IEEE Std. 1149.1-1990, available

without consuming additional device logic

– MultiVoltTM I/O interface operation, allowing a device to bridge

between systems operating at different voltages

– Low power consumption (typical specification less than 0.5 mA

in standby mode)

– 3.3-V devices support hot-socketing

Table 1. FLEX 6000 Device Features

Feature

EPF6010A

EPF6016

EPF6016A

EPF6024A

Typical gates (1)

10,000

16,000

16,000

24,000

mLogic elements (LEs)

880

1,320

1,320

1,960

oMaximum I/O pins

102 204 171 218

.cSupply voltage (VCCINT)

3.3 V

5.0 V

3.3 V

3.3 V

UNote:

t4(1) The embedded IEEE Std. 1149.1 JTAG circuitry adds up to 14,000 gates in addition to the listed typical gates.

ataSheeAltera Corporation

www.DA-DS-F6000-04.1

1

1 page

www.DataSheet4U.com

FLEX 6000 Programmable Logic Device Family Data Sheet

Functional

Description

The FLEX 6000 OptiFLEX architecture consists of logic elements (LEs).

Each LE includes a 4-input look-up table (LUT), which can implement any

4-input function, a register, and dedicated paths for carry and cascade

chain functions. Because each LE contains a register, a design can be easily

pipelined without consuming more LEs. The specified gate count for

FLEX 6000 devices includes all LUTs and registers.

LEs are combined into groups called logic array blocks (LABs); each LAB

contains 10 LEs. The Altera software automatically places related LEs into

the same LAB, minimizing the number of required interconnects. Each

LAB can implement a medium-sized block of logic, such as a counter or

multiplexer.

Signal interconnections within FLEX 6000 devices—and to and from

device pins—are provided via the routing structure of the FastTrack

Interconnect. The routing structure is a series of fast, continuous row and

column channels that run the entire length and width of the device. Any

LE or pin can feed or be fed by any other LE or pin via the FastTrack

Interconnect. See “FastTrack Interconnect” on page 17 of this data sheet

for more information.

Each I/O pin is fed by an I/O element (IOE) located at the end of each row

and column of the FastTrack Interconnect. Each IOE contains a

bidirectional I/O buffer. Each IOE is placed next to an LAB, where it can

be driven by the local interconnect of that LAB. This feature allows fast

clock-to-output times of less than 8 ns when a pin is driven by any of the

10 LEs in the adjacent LAB. Also, any LE can drive any pin via the row and

column interconnect. I/O pins can drive the LE registers via the row and

column interconnect, providing setup times as low as 2 ns and hold times

of 0 ns. IOEs provide a variety of features, such as JTAG BST support,

slew-rate control, and tri-state buffers.

Figure 1 shows a block diagram of the FLEX 6000 OptiFLEX architecture.

Each group of ten LEs is combined into an LAB, and the LABs are

arranged into rows and columns. The LABs are interconnected by the

FastTrack Interconnect. IOEs are located at the end of each FastTrack

Interconnect row and column.

wwAwlter.aDCoarpotraatSionheet4U.com

5

5 Page

www.DataSheet4U.com

FLEX 6000 Programmable Logic Device Family Data Sheet

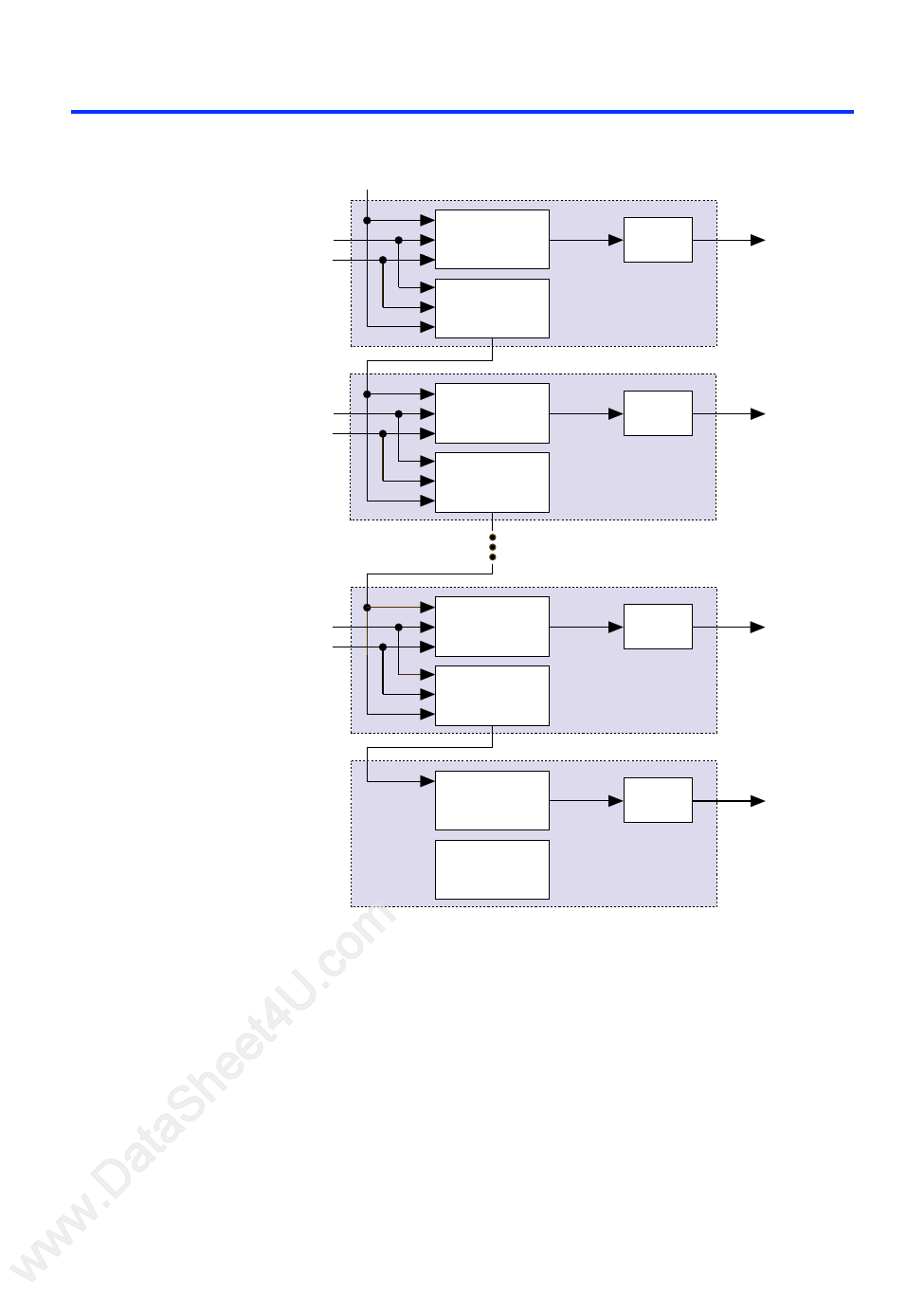

Figure 5. Carry Chain Operation

Carry-In

a1

LUT

Register

s1

b1

Carry Chain

LE 2

a2

LUT

Register

s2

b2

Carry Chain

LE 3

an LUT

bn

Carry Chain

wwAwlter.aDCoarpotraatSionheet4U.com

LUT

Carry Chain

Register

sn

LE n + 1

Register

Carry-Out

LE n + 2

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet EPF6016.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EPF6010A | (EPF6000 Series) Programmable Logic Device | Altera Corporation |

| EPF6016 | (EPF6000 Series) Programmable Logic Device | Altera Corporation |

| EPF6016A | (EPF6000 Series) Programmable Logic Device | Altera Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |