|

|

PDF UPD43257B Data sheet ( Hoja de datos )

| Número de pieza | UPD43257B | |

| Descripción | 256K-BIT CMOS STATIC RAM 32K-WORD BY 8-BIT | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPD43257B (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

DATA SHEET

MOS INTEGRATED CIRCUIT

µPD43257B

256K-BIT CMOS STATIC RAM

32K-WORD BY 8-BIT

Description

The µPD43257B is a high speed, low power, and 262,144 bits (32,768 words by 8 bits) CMOS static RAM.

Battery backup is available. And the µPD43257B has two chip enable pins (/CE1, CE2) to extend the capacity.

The µPD43257B is packed in 28-pin plastic DIP and 28-pin plastic SOP.

Features

• 32,768 words by 8 bits organization

• Fast access time: 70, 85 ns (MAX.)

• Low VCC data retention: 2.0 V (MIN.)

• Two Chip Enable inputs: /CE1, CE2

Part number

Access time Operating supply Operating ambient

ns (MAX.)

voltage

temperature

At operating

V °C mA (MAX.)

µPD43257B-xxL

70, 85

4.5 to 5.5

0 to 70

45

µPD43257B-xxLL

45

Note TA ≤ 40 °C, VCC = 3.0 V

Supply current

At standby

µA (MAX.)

At data retention

µA (MAX.) Note

50 3

15 2

Version X

This Data sheet can be applied to the version X. This version is identified with its lot number. Letter X in the fifth

character position in a lot number signifies version X.

D43257B

JAPAN

X

Lot number

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. M10693EJ7V0DS00 (7th edition)

Date Published June 2000 NS CP (K)

Printed in Japan

The mark 5 shows major revised points.

©

1992

1 page

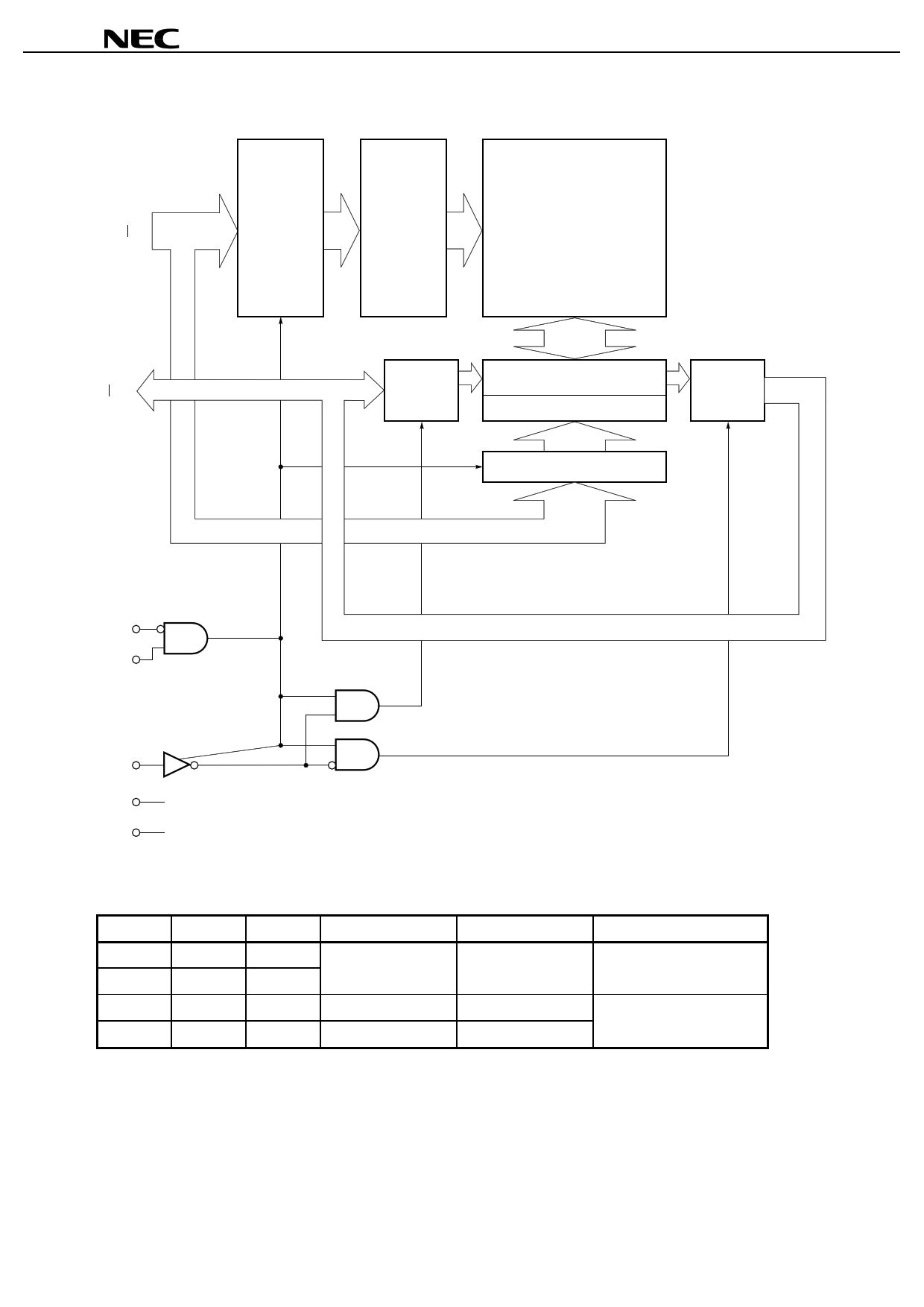

Block Diagram

A0

Address

Row

Memory cell array

buffer

decoder

262,144 bits

A14

µPD43257B

I/O1 Sense amplifier /

Input data

Switching circuit

Output data

I/O8

controller

Column decoder

controller

Address buffer

/CE1

CE2

/WE

VCC

GND

Truth Table

/CE1

H

×

L

L

CE2

×

L

H

H

Remark × : VIH or VIL

/WE

×

×

H

L

Mode

Not selected

Read

Write

I/O

High impedance

DOUT

DIN

Supply current

ISB

ICCA

Data Sheet M10693EJ7V0DS00

5

5 Page

µPD43257B

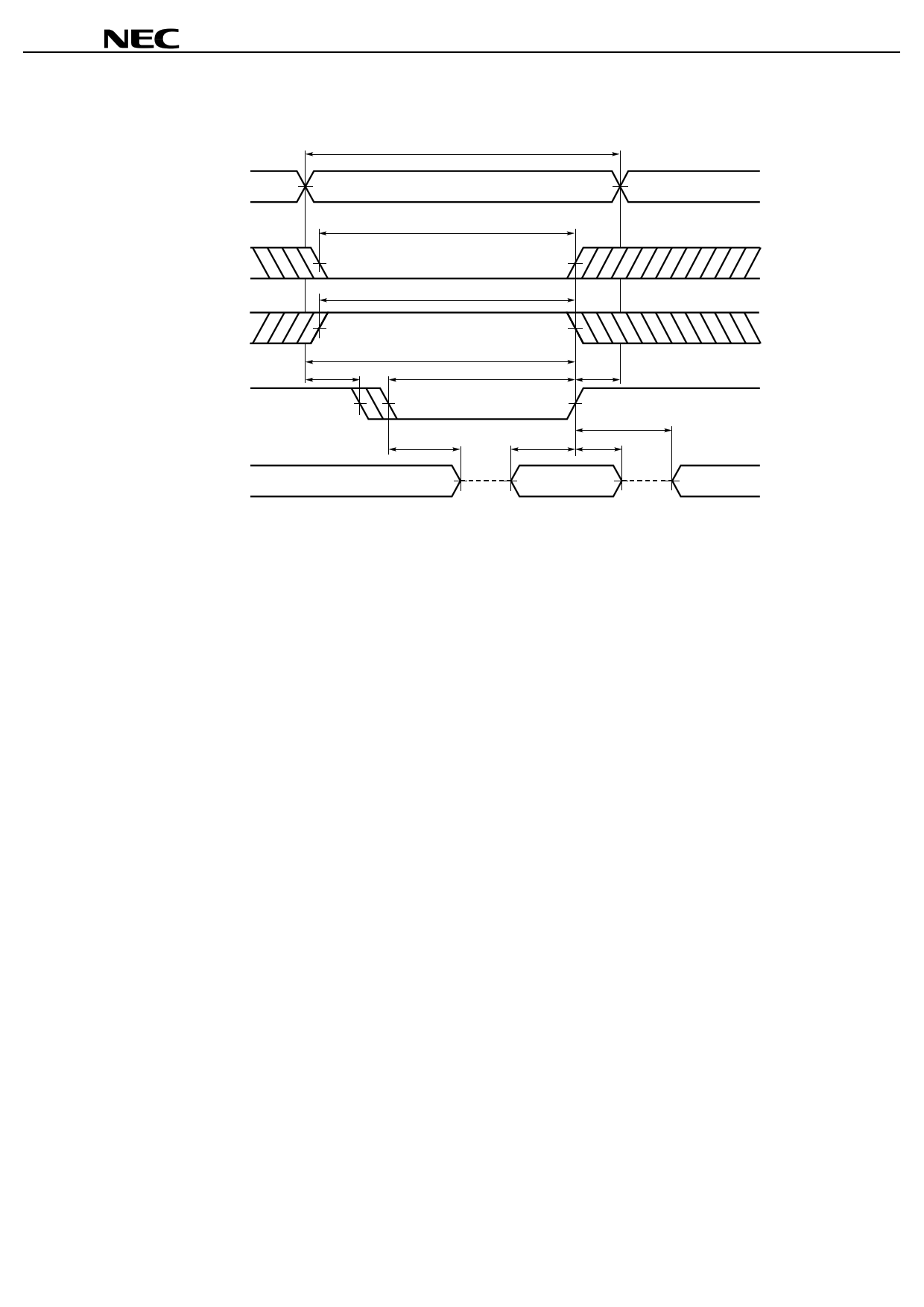

Write Cycle Timing Chart 1 (/WE Controlled)

Address (Input)

/CE1 (Input)

CE2 (Input)

/WE (Input)

I/O (Input / Output)

tWC

tCW1

tCW2

tAW

tAS tWP

tWR

tWHZ

Indefinite data out

High

impe-

dance

tOW

tDW tDH

Data in

High

impe-

dance

Indefinite data out

Cautions 1. During address transition, at least one of pins /CE1, CE2, /WE should be inactivated.

5 2. When I/O pins are in the output state, therefore the input signals must not be applied to

the output.

Remarks 1. Write operation is done during the overlap time of a low level /CE1, /WE and a high level CE2.

2. If /CE1 changes to low level at the same time or after the change of /WE to low level, or if CE2

changes to high level at the same time or after the change of /WE to low level, the I/O pins will

remain high impedance state.

3. When /WE is at low level, the I/O pins are always high impedance. When /WE is at high level,

read operation is executed. Therefore /OE should be at high level to make the I/O pins high

impedance.

Data Sheet M10693EJ7V0DS00

11

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet UPD43257B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPD43257A | 256K CMOS RAM | NEC Electronics |

| UPD43257B | 256K-BIT CMOS STATIC RAM 32K-WORD BY 8-BIT | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |