|

|

PDF RGE7500 Data sheet ( Hoja de datos )

| Número de pieza | RGE7500 | |

| Descripción | Memory Controller Hub | |

| Fabricantes | Intel | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de RGE7500 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

( DataSheet : www.DataSheet4U.com )

Intel® E7500 Chipset

Datasheet

Intel® E7500 Memory Controller Hub (MCH)

February 2002

www.DataSheet4U.com

Document Number: 290730-001

www.DataSheet4U.com

1 page

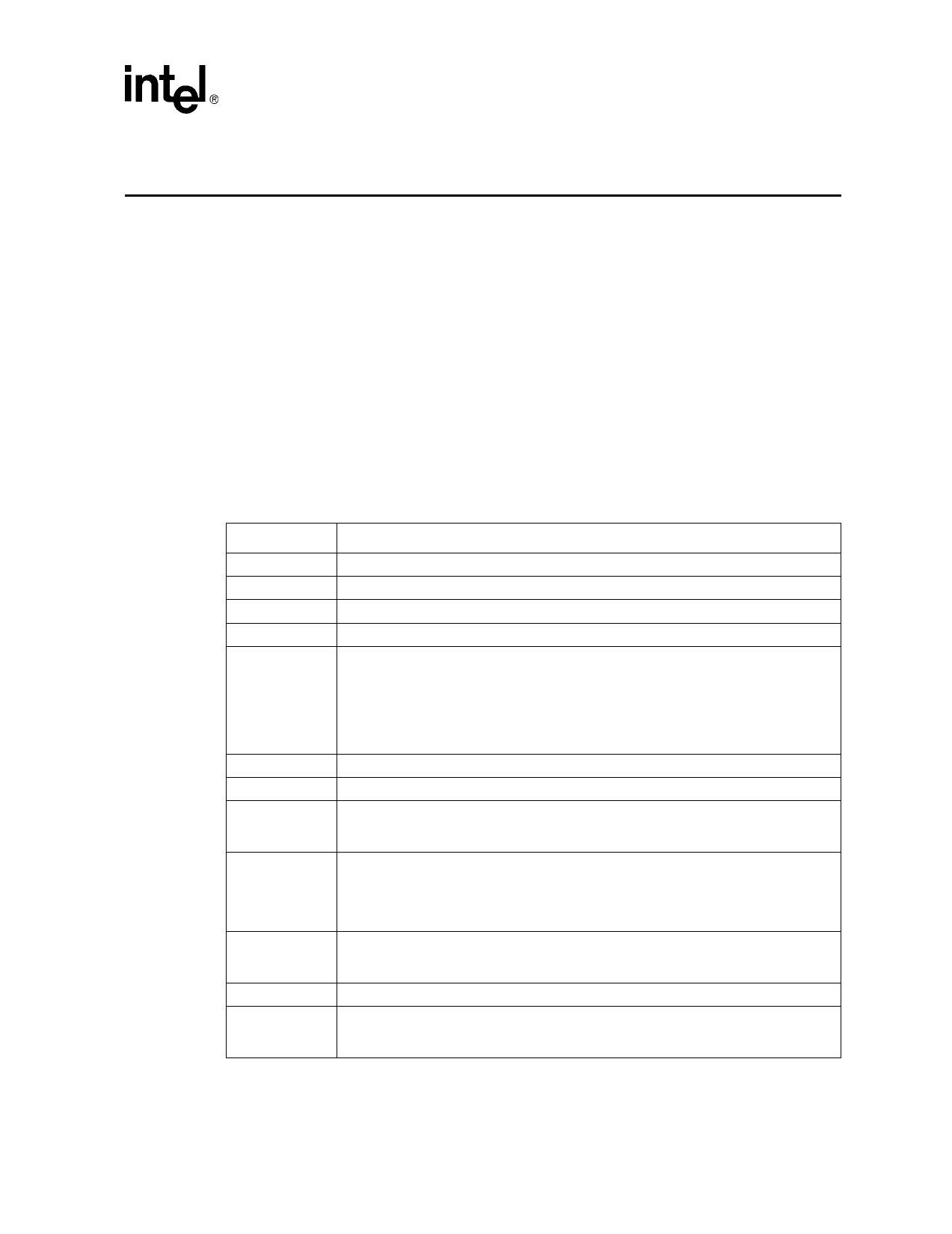

3.8

3.9

3.10

3.11

3.7.29 DRAM_CELOG_ADD—DRAM First Correctable Memory Error

Address Register (D0:F1).......................................................................80

3.7.30 DRAM_UELOG_ADD—DRAM First Uncorrectable Memory Error

Address Register (D0:F1).......................................................................81

3.7.31 DRAM_CELOG_SYNDROME—DRAM First Correctable Memory

Error Register (D0:F1) ............................................................................81

HI_B Virtual PCI-to-PCI Bridge Registers (Device 2, Function 0) .......................82

3.8.1 VID2—Vendor Identification Register (D2:F0) .......................................83

3.8.2 DID2—Device Identification Register (D2:F0) ........................................83

3.8.3 PCICMD2—PCI Command Register (D2:F0) ........................................84

3.8.4 PCISTS2—PCI Status Register (D2:F0) ................................................85

3.8.5 RID2—Revision Identification Register (D2:F0) .....................................86

3.8.6 SUBC2—Sub-Class Code Register (D2:F0) ..........................................86

3.8.7 BCC2—Base Class Code Register (D2:F0) ...........................................87

3.8.8 MLT2—Master Latency Timer Register (D2:F0) ....................................87

3.8.9 HDR2—Header Type Register (D2:F0)..................................................88

3.8.10 PBUSN2—Primary Bus Number Register (D2:F0) ................................88

3.8.11 BUSN2—Secondary Bus Number Register (D2:F0) ..............................89

3.8.12 SUBUSN2—Subordinate Bus Number Register (D2:F0) .......................89

3.8.13 SMLT2—Secondary Bus Master Latency Timer Register (D2:F0) ........90

3.8.14 IOBASE2—I/O Base Address Register (D2:F0).....................................91

3.8.15 IOLIMIT2—I/O Limit Address Register (D2:F0)......................................91

3.8.16 SEC_STS2—Secondary Status Register (D2:F0) .................................92

3.8.17 MBASE2—Memory Base Address Register (D2:F0) .............................93

3.8.18 MLIMIT2—Memory Limit Address Register (D2:F0) ..............................94

3.8.19 PMBASE2—Prefetchable Memory Base Address Register (D2:F0)......95

3.8.20 PMLIMIT2—Prefetchable Memory Limit Address Register (D2:F0).......95

3.8.21 BCTRL2—Bridge Control Register (D2:F0) ...........................................96

HI_B Virtual PCI-to-PCI Bridge Registers (Device 2, Function 1) .......................97

3.9.1 VID—Vendor Identification Register (D2:F1) .........................................98

3.9.2 DID—Device Identification Register (D2:F1) ..........................................98

3.9.3 PCICMD—PCI Command Register (D2:F1) ..........................................99

3.9.4 PCISTS—PCI Status Register (D2:F1) ..................................................99

3.9.5 RID—Revision Identification Register (D2:F1) .....................................100

3.9.6 SUBC—Sub-Class Code Register (D2:F1) ..........................................100

3.9.7 BCC—Base Class Code Register (D2:F1)...........................................101

3.9.8 HDR—Header Type Register (D2:F1)..................................................101

3.9.9 SVID—Subsystem Vendor Identification Register (D2:F1) ..................102

3.9.10 SID—Subsystem Identification Register (D2:F1) .................................102

3.9.11 HIB_FERR—Hub Interface_B First Error Register (D2:F1) .................103

3.9.12 HIB_NERR—Hub Interface_B Next Error Register (D2:F1).................104

3.9.13 SERRCMD2—SERR Command Register (D2:F1) ..............................105

3.9.14 SMICMD2—SMI Command Register (D2:F1)......................................106

3.9.15 SCICMD2—SCI Command Register (D2:F1) ......................................107

HI_C Virtual PCI-to-PCI Bridge Registers (Device 3, Function 0,1)..................108

3.10.1 DID—Device Identification Register (D3:F0) ........................................108

3.10.2 DID—Device Identification Register (D3:F1) ........................................108

HI_D Virtual PCI-to-PCI Bridge Registers (Device 4, Function 0,1)..................109

3.11.1 DID—Device Identification Register (D4:F0) ........................................109

3.11.2 DID—Device Identification Register (D4:F1) ........................................109

Datasheet

5

5 Page

Introduction

Introduction

1

1.1

The Intel® E7500 chipset is targeted for the server market, both front-end and general purpose low-

to mid-range. It is intended to be used with the Intel® Xeon™ processor with 512-KB L2 cache.

The E7500 chipset consists of three major components: the Intel® E7500 Memory Controller Hub

(MCH), the Intel® I/O Controller Hub 3 (ICH3-S), and the PCI/PCI-X 64-bit Hub 2.0 (P64H2).

The MCH provides the system bus interface, memory controller, hub interface for legacy I/O, and

three high-performance hub interfaces for PCI/PCI-X bus expansion.

This document describes the E7500 Memory Controller Hub (MCH). Section 1.3, “Intel® E7500

Chipset System Architecture” on page 1-12 provides an overview of each of the components of the

E7500 chipset. For details on other components of the chipset, refer to that component’s datasheet.

Glossary of Terms

Term

Description

DBI Dynamic Bus Inversion.

DDR

Double Data Rate memory technology.

DP Dual Processor.

Full Reset

The term “a full MCH reset” is used in this document when RSTIN# is asserted.

Hub Interface. The proprietary hub interconnect that ties the MCH to the ICH3-S and

P64H2. In this document HI cycles originating from or destined for the primary PCI

interface on the ICH3-S are generally referred to as HI/PCI_A or simply HI_A cycles.

HI Cycles originating from or destined for any target on the second, third or fourth HI

interfaces are described as HI_B, HI_C, and HI_D cycles respectively. Note that there are

two versions of HI used on the Intel® E7500 MCH: an 8-bit HI 1.5 protocol is implemented

on HI_A and a 16-bit HI 2.0 protocol is used for the HI_B, HI_C and HI_D.

Host

This term is used synonymously with processor.

IB Inbound, refers to traffic moving from PCI or other I/O toward DRAM or the system bus.

ICH3-S

Intel® Xeon™

processor with

512-KB L2 cache

The I/O Controller Hub 3-S component that contains the primary PCI interface, LPC

interface, USB, ATA-100, and other legacy functions. It communicates with the MCH over

a proprietary interconnect called the hub interface.

The processor supported by the Intel® E7500 chipset. This processor is the second

generation of processors based on the Intel® NetBurst™ microarchitecture. This

processor delivers performance levels that are significantly higher than previous

generations of IA-32 processors. This processor supports 1-2 processors on a single

system bus and has a 512 KB integrated L2 cache.

MCH

The Memory Controller Hub component that contains the processor interface and DRAM

interface. It communicates with the I/O Controller Hub 3-S (ICH3-S) and P64H2 over a

proprietary interconnect called the Hub Interface (HI).

OB Outbound, refers to traffic moving from the system bus to PCI or other I/O.

Intel® P64H2

PCI/PCI-X 64-bit Hub 2.0 component. The Bus Controller Hub component has a 16-bit

hub interconnect 2.0 on its primary side and two, 64-bit PCI-X bus segments on the

secondary side.

Datasheet

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet RGE7500.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| RGE7500 | Memory Controller Hub | Intel |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |