|

|

PDF KU80960CF Data sheet ( Hoja de datos )

| Número de pieza | KU80960CF | |

| Descripción | 32-Bit High Performance Superscalar Embedded Processor | |

| Fabricantes | Intel | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de KU80960CF (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ww.DataSh83Ee20me-9tB4b6Uei0t.dCcHodFmieg-4dh0-M,P-ie3cr3rfoo, p-r2mr5oacnecsesoSruperscalarProduct Features

w s Socket and Object Code Compatible with 80960CA

ms Two Instructions/Clock Sustained Execution

s Four 71 Mbytes/s DMA Channels with Data Chaining

os Demultiplexed 32-Bit Burst Bus with Pipelining

Datasheet

.cs 32-Bit Parallel Architecture

— Two Instructions/clock Execution

U—Load/Store Architecture

t4—Sixteen 32-Bit Global Registers

— Sixteen 32-Bit Local Registers

e—Manipulates 64-Bit Bit Fields

— 11 Addressing Modes

e—Full Parallel Fault Model

h—Supervisor Protection Model

s Fast Procedure Call/Return Model

S—Full Procedure Call in 4 Clocks

tas On-Chip Register Cache

— Caches Registers on Call/Ret

— Minimum of 6 Frames Provided

a—Up to 15 Programmable Frames

.Ds On-Chip Instruction Cache

— 4 Kbyte Two-Way Set Associative

— 128-Bit Path to Instruction Sequencer

w—Cache-Lock Modes

— Cache-Off Mode

ws High Bandwidth On-Chip Data RAM

m— 1 Kbyte On-Chip Data RAM

w o—Sustains 128 bits per Clock Access

.cs Selectable Big or Little Endian Byte

UOrdering

s Four On-Chip DMA Channels

— 71 Mbytes/s Fly-by Transfers

— 40 Mbytes/s Two-Cycle Transfers

— Data Chaining

— Data Packing/Unpacking

— Programmable Priority Method

s 32-Bit Demultiplexed Burst Bus

— 128-Bit Internal Data Paths to and from

Registers

— Burst Bus for DRAM Interfacing

— Address Pipelining Option

— Fully Programmable Wait States

— Supports 8-, 16- or 32-Bit Bus Widths

— Supports Unaligned Accesses

— Supervisor Protection Pin

s High-Speed Interrupt Controller

— Up to 248 External Interrupts

— 32 Fully Programmable Priorities

— Multi-mode 8-Bit Interrupt Port

— Four Internal DMA Interrupts

— Separate, Non-maskable Interrupt Pin

— Context Switch in 625 ns Typical

s On-Chip Data Cache

— 1 Kbyte Direct-Mapped, Write Through

— 128 bits per Clock Access on Cache Hit

.DataSheet4Order Number: 272886-002

www September 2002

1 page

Contents

12 80960CF PQFP Package Thermal Characteristics ....................................................................24

13 Die Stepping Cross Reference ...................................................................................................25

14 Absolute Maximum Ratings ........................................................................................................26

15 Operating Conditions ..................................................................................................................26

16 D.C. Specifications .....................................................................................................................28

17 80960CF AC Characteristics (40 MHz) ......................................................................................29

18 80960CF AC Characteristics (33 MHz) ......................................................................................31

19 80960CF AC Characteristics (25 MHz) ......................................................................................33

20 Reset Conditions ........................................................................................................................42

21 Hold Acknowledge and Backoff Conditions ................................................................................42

Revision History

Date

September 2002

June 1996

Revision

Description

002 References to the -16 MHz product have been removed from the datasheet.

001 Initial release of the datasheet.

Datasheet

5

5 Page

80960-40, -33, -25

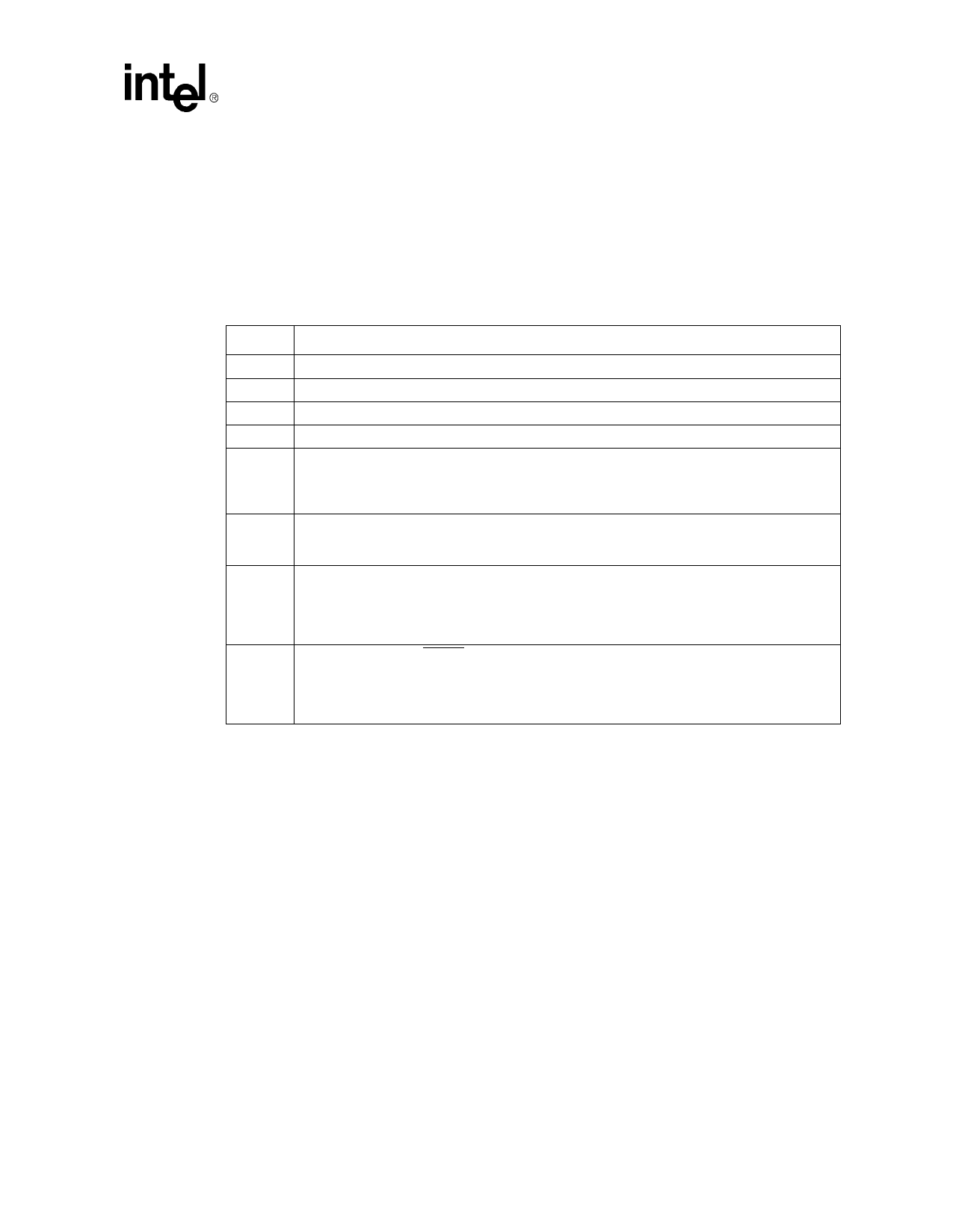

3.2 Pin Descriptions

This section defines the 80960CF pins. Table 2 presents the legend for interpreting the pin

descriptions in Tables 3 through 5. Table 3 presents the external bus signals. Table 4 presents

processor control signals. Table 5 presents the DMA and Interrupt Unit control signals.

Note: All pins float while the processor is in the ONCE mode.

Table 2. Symbol Legend

Symbol

Description

I

O

I/O

–

S(...)

A(...)

H(...)

R(...)

Input only pin

Output only pin

Pin may be either an input or output

Pins “must be” connected as described

Synchronous. Inputs must meet setup and hold times relative to PCLK2:1 for proper operation.

Outputs are synchronous to PCLK2:1.

S(E) Edge sensitive input

S(L) Level sensitive input

Asynchronous. Inputs may be asynchronous to PCLK2:1.

A(E)Edge sensitive input

A(L)Level sensitive input

While the bus is in the Hold Acknowledge or Bus Backoff state, the pin:

H(1) is driven to VCC

H(0)is driven to VSS

H(Z) floats

H(Q)continues to be a valid input

While the processor’s RESET pin is low, the pin:

R(1) is driven to VCC

R(0)is driven to VSS

R(Z) floats

R(Q)continues to be a valid output

Datasheet

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet KU80960CF.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| KU80960CA | 32-Bit High Performance Embedded Processor | Intel |

| KU80960CF | 32-Bit High Performance Superscalar Embedded Processor | Intel |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |