|

|

PDF XCR5128 Data sheet ( Hoja de datos )

| Número de pieza | XCR5128 | |

| Descripción | 128 Macrocell CPLD | |

| Fabricantes | Xilinx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XCR5128 (archivo pdf) en la parte inferior de esta página. Total 20 Páginas | ||

|

No Preview Available !

APPLICATION NOTE

0

mR

t4U.co XCR5128: 128 Macrocell CPLDDS041 (v1.2) August 10, 2000

0 14* Product Specification

heeFeatures

taS• Industry's first TotalCMOS™ PLD - both CMOS design

aand process technologies

.D• Fast Zero Power (FZP™) design technique provides

ultra-low power and very high speed

w• IEEE 1149.1-compliant, JTAG Testing Capability

w- Four pin JTAG interface (TCK, TMS, TDI, TDO)

w m- IEEE 1149.1 TAP Controller

- JTAG commands include: Bypass, Sample/Preload,

oExtest, Usercode, Idcode, HighZ

• 5V, In-System Programmable (ISP) using the JTAG

.cinterface

- On-chip supervoltage generation

- ISP commands include: Enable, Erase, Program,

UVerify

t4- Supported by multiple ISP programming platforms

• High speed pin-to-pin delays of 7.5 ns

• Ultra-low static power of less than 100 µA

e• 100% routable with 100% utilization while all pins and

eall macrocells are fixed

• Deterministic timing model that is extremely simple to

huse

• Four clocks available

S• Programmable clock polarity at every macrocell

• Support for asynchronous clocking

ta• Innovative XPLA™ architecture combines high speed

with extreme flexibility

a• 1000 erase/program cycles guaranteed

• 20 years data retention guaranteed

.D• Logic expandable to 37 product terms

• PCI compliant

• Advanced 0.5µ E2CMOS process

w• Security bit prevents unauthorized access

• Design entry and verification using industry standard

wand Xilinx CAE tools

m• Reprogrammable using industry standard device

w oprogrammers

.c• Innovative Control Term structure provides either sum

Uterms or product terms in each logic block for:

t4- Programmable 3-state buffer

e- Asynchronous macrocell register preset/reset

e• Programmable global 3-state pin facilitates "bed of

hnails" testing without using logic resources

S• Available in PLCC, VQFP, and PQFP packages

www.Data• Available in both Commercial and Industrial grades

Description

The XCR5128 CPLD (Complex Programmable Logic

Device) is the third in a family of CoolRunner® CPLDs from

Xilinx. These devices combine high speed and zero power

in a 128 macrocell CPLD. With the FZP design technique,

the XCR5128 offers true pin-to-pin speeds of 7.5 ns, while

simultaneously delivering power that is less than 100 µA at

standby without the need for ‘turbo bits' or other power

down schemes. By replacing conventional sense amplifier

methods for implementing product terms (a technique that

has been used in PLDs since the bipolar era) with a cas-

caded chain of pure CMOS gates, the dynamic power is

also substantially lower than any competing CPLD. These

devices are the first TotalCMOS PLDs, as they use both a

CMOS process technology and the patented full CMOS

FZP design technique. For 3V applications, Xilinx also

offers the high-speed XCR3128 CPLD that offers these

features in a full 3V implementation.

The Xilinx FZP CPLDs utilize the patented XPLA

(eXtended Programmable Logic Array) architecture. The

XPLA architecture combines the best features of both PLA

and PAL type structures to deliver high speed and flexible

logic allocation that results in superior ability to make

design changes with fixed pinouts. The XPLA structure in

each logic block provides a fast 7.5 ns PAL path with five

dedicated product terms per output. This PAL path is joined

by an additional PLA structure that deploys a pool of 32

product terms to a fully programmable OR array that can

allocate the PLA product terms to any output in the logic

block. This combination allows logic to be allocated effi-

ciently throughout the logic block and supports as many as

37 product terms on an output. The speed with which logic

is allocated from the PLA array to an output is only 2 ns,

regardless of the number of PLA product terms used, which

results in worst case tPD's of only 9.5 ns from any pin to any

other pin. In addition, logic that is common to multiple out-

puts can be placed on a single PLA product term and

shared across multiple outputs via the OR array, effectively

increasing design density.

The XCR5128 CPLDs are supported by industry standard

CAE tools (Cadence/OrCAD, Exemplar Logic, Mentor, Syn-

opsys, Synario, Viewlogic, and Synplicity), using text

(ABEL, VHDL, Verilog) and/or schematic entry. Design ver-

ification uses industry standard simulators for functional

and timing simulation. Development is supported on per-

sonal computer, Sparc, and HP platforms. Device fitting

DS041 (v1.2) August 10, 2000

www.xilinx.com

1

1-800-255-7778

1 page

XCR5128: 128 Macrocell CPLD

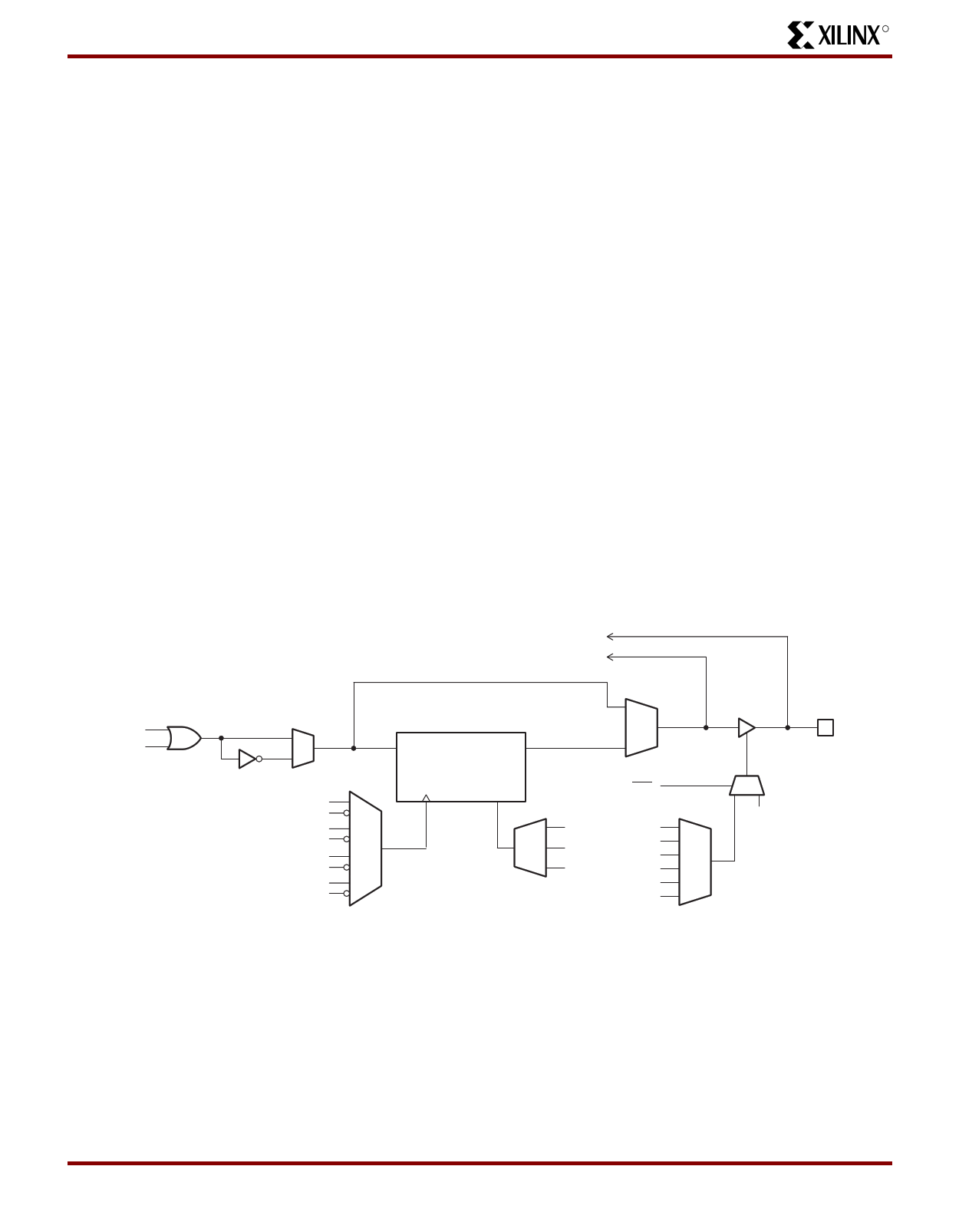

Macrocell Architecture

Figure 3 shows the architecture of the macrocell used in

the CoolRunner family. The macrocell consists of a flip-flop

that can be configured as either a D- or T- type. A D-type

flip-flop is generally more useful for implementing state

machines and data buffering. A T-type flip-flop is generally

more useful in implementing counters. All CoolRunner fam-

ily members provide both synchronous and asynchronous

clocking and provide the ability to clock off either the falling

or rising edges of these clocks. These devices are

designed such that the skew between the rising and falling

edges of a clock are minimized for clocking integrity. There

are four clocks available on the XCR5128 device. Clock 0

(CLK0) is designated as the "synchronous" clock and must

be driven by an external source. Clock 1 (CLK1), Clock 2

(CLK2), and Clock 3 (CLK3) can either be used as a syn-

chronous clock (driven by an external source) or as an

asynchronous clock (driven by a macrocell equation). The

timing for asynchronous clocks is different in that the tCO

time is extended by the amount of time that it takes for the

signal to propagate through the array and reach the clock

network, and the tSU time is reduced.

Two of the control terms (CT0 and CT1) are used to control

the Preset/Reset of the macrocell’s flip-flop. The Pre-

set/Reset feature for each macrocell can also be disabled.

Note that the Power-on Reset leaves all macrocells in the

"zero" state when power is properly applied. The other four

R

control terms (CT2-CT5) can be used to control the Output

Enable of the macrocell’s output buffers. The reason there

are as many control terms dedicated for the Output Enable

of the macrocell is to insure that all CoolRunner devices are

PCI compliant. The macrocell’s output buffers can also be

always enabled or disabled. All CoolRunner devices also

provide a Global 3-State (GTS) pin, which, when enabled

and pulled Low, will 3-state all the outputs of the device.

This pin is provided to support "In-Circuit Testing" or

"Bed-of-Nails Testing".

There are two feedback paths to the ZIA: one from the mac-

rocell, and one from the I/O pin. The ZIA feedback path

before the output buffer is the macrocell feedback path,

while the ZIA feedback path after the output buffer is the I/O

pin ZIA path. When the macrocell is used as an output, the

output buffer is enabled, and the macrocell feedback path

can be used to feedback the logic implemented in the mac-

rocell. When the I/O pin is used as an input, the output

buffer will be 3-stated and the input signal will be fed into

the ZIA via the I/O feedback path, and the logic imple-

mented in the buried macrocell can be fed back to the ZIA

via the macrocell feedback path. It should be noted that

unused inputs or I/Os should be properly terminated (see

the section on Terminations in this data sheet and the appli-

cation note: Terminating Unused I/O Pins in xilinx XPLA1

and XPLA2 CPLDs).

TO ZIA

PAL

PLA D/T

CLK0

CLK0

CLK1

CLK1

CLK2

CLK2

CLK3

CLK3

Figure 3: XCR5128 Macrocell Architecture

Q

INIT

(P or R)

CT0

CT1

GND

GTS

CT2

CT3

CT4

CT5

VCC

GND

GND

SP00457

5

www.xilinx.com

DS041 (v1.2) August 10, 2000

1-800-255-7778

5 Page

XCR5128: 128 Macrocell CPLD

Programming Specifications

R

Symbol

DC Parameters

VCCP

VCC supply program/verify

ICCP

ICC limit program/verify

VIH Input voltage (High)

VIL Input voltage (Low)

VSOL

Output voltage (Low)

VSOH

Output voltage (High)

TDO_IOL Output current (Low)

TDO_IOH Output current (High)

AC Parameters

fMAX

PWE

CLK maximum frequency

Pulse width erase

PWP

Pulse width program

PWV

Pulse width verify

INIT Initialization time

TMS_SU TMS setup time before TCK ↑

TDI_SU TDI setup time before TCK ↑

TMS_H TMS hold time after TCK ↑

TDI_H TDI hold time after TCK ↑

TDO_CO TDO valid after TCK ↓

Parameter

Absolute Maximum Ratings1

Min.

4.5

2.0

2.4

12

-12

10

100

10

10

100

10

10

20

20

Max.

5.5

200

0.8

0.5

30

Unit

V

mA

V

V

V

V

mA

mA

MHz

ms

ms

µs

µs

ns

ns

ns

ns

ns

Symbol

Parameter

Min.

Max.

VCC Supply voltage2

-0.5 7.0

VI Input voltage

-1.2 VCC +0.5

VOUT Output voltage

-0.5 VCC +0.5

IIN Input current

-30 30

IOUT Output current

-100

100

TJ Maximum junction temperature

-40 150

Tstr Storage temperature

-65 150

Notes:

1. Stresses above those listed may cause malfunction or permanent damage to the device. This is a stress rating only.

Functional operation at these or any other condition above those indicated in the operational and programming

specification is not implied.

2. The chip supply voltage must rise monotonically.

Unit

V

V

V

mA

mA

5C

5C

Operating Range

Product Grade

Commercial

Industrial

Temperature

0 to +70°C

-40 to +85°C

Voltage

5.0V +5%

5.0V +10%

11

www.xilinx.com

DS041 (v1.2) August 10, 2000

1-800-255-7778

11 Page | ||

| Páginas | Total 20 Páginas | |

| PDF Descargar | [ Datasheet XCR5128.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XCR5128 | 128 Macrocell CPLD | Xilinx |

| XCR5128C | 128 Macrocell CPLD | Xilinx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |