|

|

PDF ICS9148B-04 Data sheet ( Hoja de datos )

| Número de pieza | ICS9148B-04 | |

| Descripción | Frequency Generator & Integrated Buffers | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS9148B-04 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

Integrated

Circuit

Systems, Inc.

ICS9148 B -04

Frequency Generator & Integrated Buffers for PENTIUM/ProTM

General Description

The ICS9148B-04 generates all clocks required for high

speed RISC or CISC microprocessor systems such as Intel

PentiumPro or Cyrix. Eight different reference frequency

multiplying factors are externally selectable with smooth

frequency transitions.

Features include four CPU, seven PCI and Twelve SDRAM

clocks. Two reference outputs are available equal to the

crystal frequency. Plus the IOAPIC output powered byVDDL1.

One 48 MHz for USB, and one 24 MHz clock for Super IO.

Spread Spectrum built in - ±1.5% modulation to reduce the

EMI. Serial programming I2C interface allows changing

functions, stop clock programing and Frequency selection.

Rise time adjustment for VDD at 3.3V or 2.5V CPU.

Additionally, the device meets the Pentium power-up

stabilization, which requires that CPU and PCI clocks be

stable within 2ms after power-up. It is not recommended to

use I/O dual function pin for the slots (ISA, PCI, CPU, DIMM).

The add on card might have a pull up or pull down.

Features

3.3V outputs: SDRAM, PCI, REF, 48/24MHz

2.5V or 3.3V outputs: CPU, IOAPIC

20 ohm CPU clock output impedance

20 ohm PCI clock output impedance

Skew from CPU (earlier) to PCI clock - 1 to 4 ns, center

2.6 ns.

No external load cap for CL=18pF crystals

±250 ps CPU, PCI clock skew

400ps (cycle to cycle) CPU jitter

Smooth frequency switch, with selections from 50 to 83.3

MHz CPU.

I2C interface for programming

2ms power up clock stable time

Clock duty cycle 45-55%.

48 pin 300 mil SSOP package

3.3V operation, 5V tolerant input.

Pin Configuration

Block Diagram

9148-04 Rev B 01/20/98

48-Pin SSOP

* Internal Pull-up Resistor of

240K to 3.3V on indicated inputs

Power Groups

VDD1 = REF (0:1), X1, X2

VDD2 = PCICLK_F, PCICLK(0:5)

VDD3 = SDRAM (0:11), supply for PLL core,

24MHz, 48MHz

VDDL1 = IOAPIC

VDDL2 = CPUCLK (0:3)

Pentium is a trademark of Intel Corporation

I2C is a trademark of Philips Corporation

ICS reserves the right to make changes in the device data identified in this

publication without further notice. ICS advises its customers to obtain the latest

version of all device data to verify that any information being relied upon by the

customer is current and accurate.

1 page

ICS9148 B -04

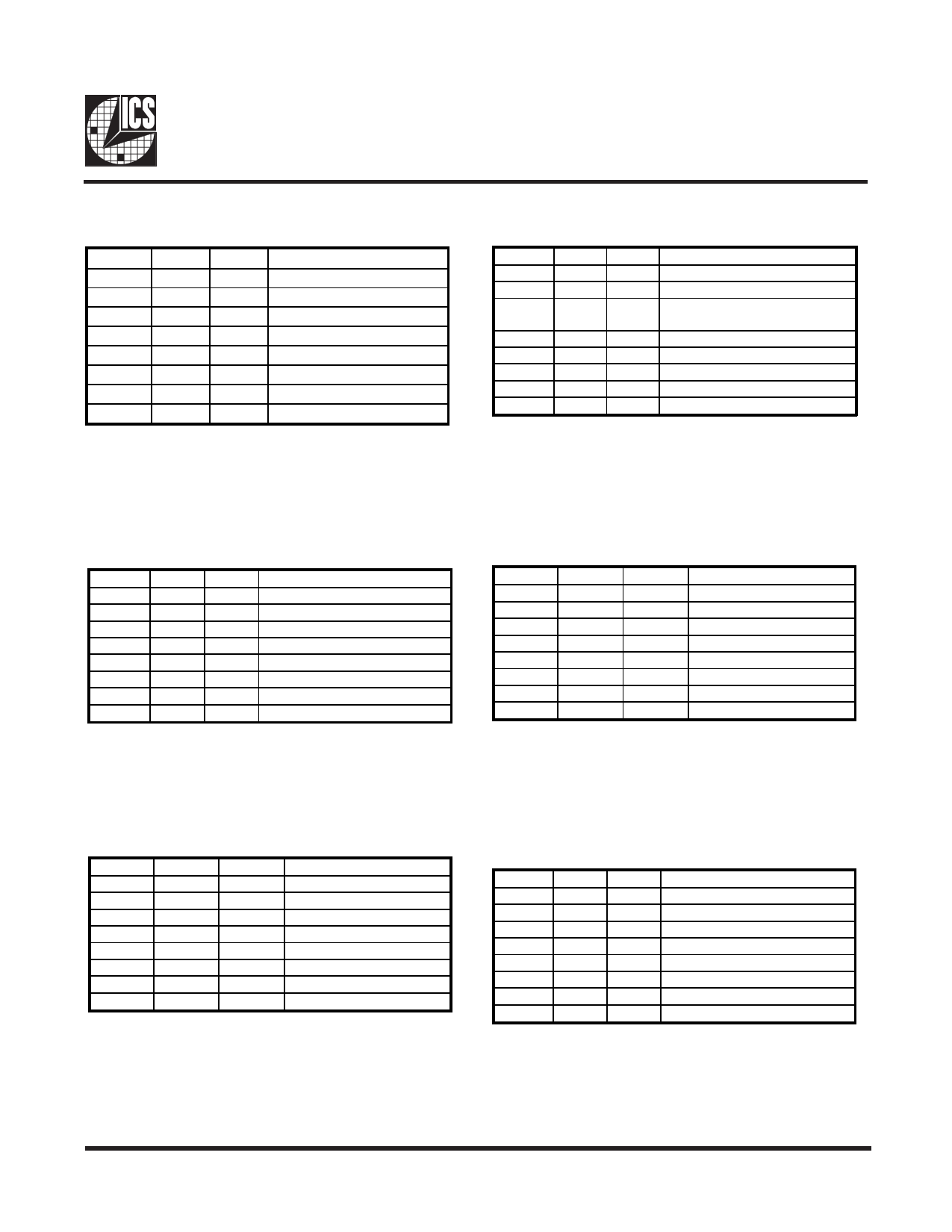

Byte 1: CPU,Active/Inactive Register

(1 = enable, 0 = disable)

Bit

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Pin #

-

-

-

-

40

41

43

44

PWD

1

1

1

1

1

1

1

1

Description

(Reserved)

(Reserved)

(Reserved)

(Reserved)

CPUCLK3 (Act/Inact)

CPUCLK2 (Act/Inact)

CPUCLK1 (Act/Inact)

CPUCLK0 (Act/Inact)

Notes:

1. Inactive means outputs are held LOW and are disabled

from switching.

Byte 3: SDRAMActive/Inactive Register

(1 = enable, 0 = disable)

Bit

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Pin #

28

29

31

32

34

35

37

38

PWD

1

1

1

1

1

1

1

1

Description

SDRAM7 (Act/Inact)

SDRAM6 (Act/Inact)

SDRAM5 (Act/Inact)

SDRAM4 (Act/Inact)

SDRAM3 (Act/Inact)

SDRAM2 (Act/Inact)

SDRAM1 (Act/Inact)

SDRAM0 (Act/Inact)

Notes:

1. Inactive means outputs are held LOW and are disabled

from switching.

Byte 5: Peripheral Active/Inactive Register

(1 = enable, 0 = disable)

Bit

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Pin #

-

-

-

47

-

-

46

2

PWD

1

1

1

1

1

1

1

1

Description

(Reserved)

(Reserved)

(Reserved)

IOAPIC (Act/Inact)

(Reserved)

(Reserved)

REF1 (Act/Inact)

REF0 (Act/Inact)

Notes:

1. Inactive means outputs are held LOW and are disabled from

switching. These outputs are designed to be configured at

power-on and are not expected to be configured during the

normal modes of operation.

2. REF1 only in Desktop Mode

Byte 2: PCIActive/Inactive Register (1 = enable, 0 = disable)

Bit

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Pin #

-

7

15

14

12

11

10

8

PWD

1

1

1

1

1

1

1

1

Description

(Reserved)

PCICLK_F (Act/Inact)

PCICLK5 (Act/Inact)

(Desktop only)

PCICLK4 (Act/Inact)

PCICLK3 (Act/Inact)

PCICLK2 (Act/Inact)

PCICLK1 (Act/Inact)

PCICLK0 (Act/Inact)

Notes:

1. Inactive means outputs are held LOW and are disabled

from switching.

2. PCICLK5 only in Desktop Mode

Byte 4: SDRAM Active/Inactive Register

(1 = enable, 0 = disable)

Bit

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Pin #

-

-

-

-

17

18

20

21

PWD

1

1

1

1

1

1

1

1

Description

(Reserved)

(Reserved)

(Reserved)

(Reserved)

SDRAM11 (Act/Inact)

SDRAM10 (Act/Inact)

SDRAM9 (Act/Inact)

SDRAM8 (Act/Inact)

Notes:

1. Inactive means outputs are held LOW and are disabled

from switching. These outputs are designed to be

configured at power-on and are not expected to be

configured during the normal modes of operation.

Byte 6: Optional Register For Possible Future Requirements

Bit

Bit 7

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

Bit 0

Pin #

-

-

-

-

-

-

-

-

PWD

1

1

1

1

1

1

1

1

Description

(Reserved)

(Reserved)

(Reserved)

(Reserved)

(Reserved)

(Reserved)

(Reserved)

(Reserved)

Notes:

1. Byte 6 is reserved by Integrated Circuit Systems for

future applications.

Note: PWD = Power-Up Default

5

5 Page

Electrical Characteristics - CPU

TA = 0 - 70C; VDD = 3.3 V +/-5%, VDDL = 2.5 V +/-5%; CL = 20 pF

PARAMETER

Output Impedance1

Output Impedance1

SYMBOL

CONDITIONS

RDSP2B VO = VDD*(0.5)

RDSN2B VO = VDD*(0.5)

Output High Voltage VOH2B IOH = -8 mA

Output Low Voltage VOL2B IOL = 12 mA

Output High Current

IOH2B VOH = 1.7 V

Output Low Current

Rise Time1

Fall Time1

Duty Cycle1

Skew1

Jitter, Cycle-to-cycle1

Jitter, One Sigma1

Jitter, Absolute1

IOL2B

tr2B

tf2B

dt2B

tsk2B

tjcyc-cyc2B

tj1s2B

tjabs2B

VOL = 0.7 V

VOL = 0.4 V, VOH = 2.0 V

VOH = 2.0 V, VOL = 0.4 V

VT = 1.25 V

VT = 1.25 V

VT = 1.25 V

VT = 1.25 V

VT = 1.25 V

1Guaranteed by design, not 100% tested in production.

Electrical Characteristics - PCI

TA = 0 - 70C; VDD = VDDL = 3.3 V +/-5%; CL = 30 pF

PARAMETER

Output Impedance1

Output Impedance1

SYMBOL

CONDITIONS

RDSP1 VO = VDD*(0.5)

RDSN1 VO = VDD*(0.5)

Output High Voltage

VOH1 IOH = -28 mA

Output Low Voltage

VOL1 IOL = 23 mA

Output High Current

IOH1 VOH = 2.0 V

Output Low Current

Rise Time1

Fall Time1

Duty Cycle1

Skew1

Jitter, One Sigma1

IOL1 VOL = 0.8 V

tr1 VOL = 0.4 V, VOH = 2.4 V

tf1 VOH = 2.4 V, VOL = 0.4 V

dt1 VT = 1.5 V

tsk1 VT = 1.5 V

tj1s1 VT = 1.5 V, synchronous

Jitter, Absolute1

tj1s1a

tjabs1

VT = 1.5 V, asynchronous

VT = 1.5 V, synchronous

tjabs1a VT = 1.5 V, asynchronous

1Guaranteed by design, not 100% tested in production.

11

ICS9148 B -04

MIN

13.5

13.5

2

19

45

-300

TYP MAX UNITS

45 Ohm

45 Ohm

2.2 V

0.3 0.4 V

-20 -16 mA

26 mA

2.2 2.5 ns

1.1 1.6 ns

55 %

250 ps

200 400 ps

50 150 ps

300 ps

MIN TYP MAX UNITS

10 24 Ohm

10 24 Ohm

2.4 3

V

0.2 0.4 V

-60 -40 mA

41 50

mA

1.6 2 ns

1.2 2 ns

45 51 55 %

100 250 ps

100 300 ps

200 400 ps

-500

-1000

500 ps

1000 ps

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet ICS9148B-04.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS9148B-04 | Frequency Generator & Integrated Buffers | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |