|

|

PDF ILA8842 Data sheet ( Hoja de datos )

| Número de pieza | ILA8842 | |

| Descripción | I2C BUS Controlled PAL/NTSC/Secam TV processor | |

| Fabricantes | IK Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de ILA8842 (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

TECHNICAL DATA

I2C BUS CONTROLLED SINGLE CHIP TV-RECEIVER

The ILA 8842 is I2C-bus controlled single chip TV processor which is intended to be applied in PAL,

NTSC, PAL/NTSC and multi-standard television receivers.

FEATURES

The following features are available:

• Multi-standard vision IF circuit with an alignment-free PLL

demodulator without external components

• Alignment-free multi-standard FM sound demodulator (4.5 MHz

mto 6.5 MHz)

• Audio switch

o• Automatic Volume Limiting

.c• Flexible source selection with CVBS switch and Y(CVBS)/C input

so that a comb filter can be applied

• Integrated chrominance trap circuit

U• Integrated luminance delay line

t4• Asymmetrical peaking in the luminance channel with a

(defeatable) noise coring function

• PAL/SECAM/NTSC decoder

e• Base-band delay line for PAL and SECAM or chroma comb filter

efor NTSC

• Black stretching of non-standard CVBS or luminance signals

h• Integrated chroma band-pass filter with switchable centre

frequency

S• Dynamic skin tone control circuit

ta• Blue stretch circuit which offsets colours near white towards blue

• RGB control circuit with "Continuous Cathode Calibration" and

awhite point adjustment

• Possibility to insert a "blue back" option when no video signal is

.Davailable

• Horizontal synchronization with two control loops and alignment-

free horizontal oscillator

w• Vertical count-down circuit

• Vertical driver optimised for DC-coupled vertical output stages

ww• I2C-bus control of various functions

1

1 page

ILA8842

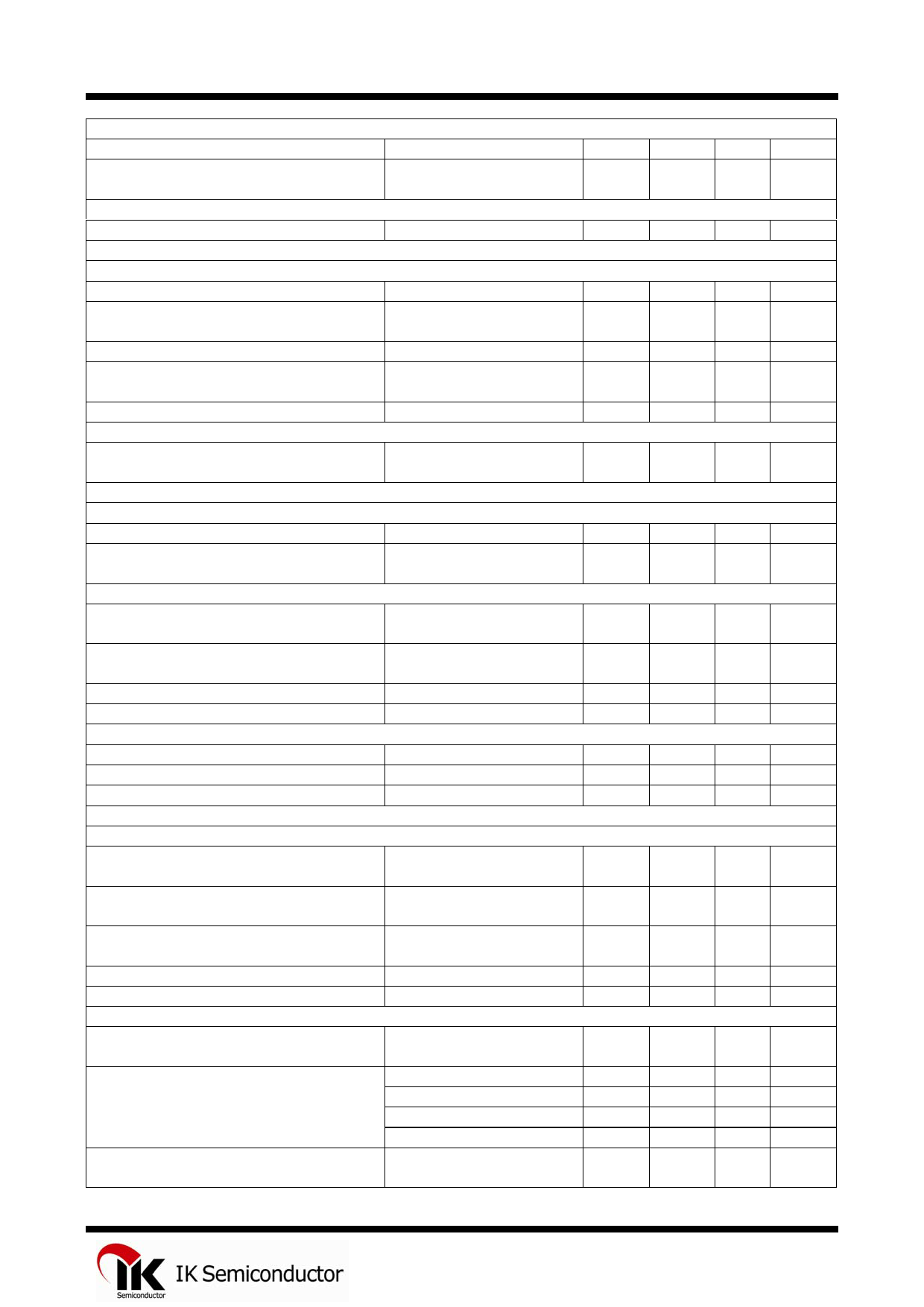

Table 2 Output status bits.

FUNCTION

Output status bytes

SUB DATA BYTE

ADDRE D7 D6 D5 D4 D3 D2 D1 D0

SS

(HEX)

00 POR FSI X SL XPR CD2 CD1 CD

0

01 NDF IN1 X IFI AFA AFB SXA SX

B

02 N2 X BCF IVW ID3 ID2 ID1 ID0

Table 3 Characteristics

Parameter

Conditions

min Typ. max unit

Supplies

POWER SUPPLY (PINS 12 AND 37)

supply voltage

supply current pin 12

supply current pin 37

total power dissipation

IF circuit

VISION IF AMPLIFIER INPUTS (PINS 48 AND 49)

input sensitivity (RMS value)

fi = 38.90 MHz

7,2 8 8,8 V

- 70 - mA

- 60 - mA

- 1040 - mW

10 35 100 µV

fi = 45.75 MHz

10 35 100 µV

fi = 58.75 MHz

10 35 100 µV

input resistance (differential)

input capacitance (differential)

gain control range

maximum input signal (RMS value)

PLL DEMODULATOR (PLL FILTER ON PIN 5);

Free-running frequency of VCO

PLL not locked, deviation

from nominal setting

Catching range PLL

-

-

64

150

-500

-

2 -k

3 - pF

75 - dB

- - mV

- +500 kHz

2 - MHz

Acquisition time PLL

VIDEO AMPLIFIER OUTPUT (PIN 6);

zero signal output level

negative modulation;

positive modulation;

top sync level

negative modulation

white level

positive modulation

Difference in amplitude between

negative and positive modulation

video output impedance

Internal bias current of NPN emitter

follower output transistor

maximum source current

- - 20 ms

- 4,2 - V

- 2,2 - V

1,8 1,9 2 V

- 4,4 - V

- 0 15 %

- 50 -

1 - - mA

- - 5 mA

5

5 Page

ILA8842

VERTICAL SHIFT

control range

63 steps

equivalent differential vertical drive

output current (peak-to-peak value)

S-CORRECTION

control range

63 steps

Colour demodulation part

CHROMINANCE AMPLIFIER

ACC control range

change in amplitude of the output

signals over the ACC range

threshold colour killer ON

hysteresis colour killer OFF

strong signal conditions;

S/N>40 dB;

noisy input signals;

ACL CIRCUIT;

chrominance burst ratio at which the

ACL starts to operate

REFERENCE PART

Phase-locked loop;

catching range

phase shift for a ±400 Hz deviation of

the oscillator frequency

Oscillator

temperature coefficient of the oscillator

frequency

oscillator frequency deviation with

VP = 8 V ±10%

respect to the supply

minimum negative resistance

maximum load capacitance

HUE CONTROL

hue control range

63 steps;

hue variation for ±10% VP

hue variation with temperature

Tamb = 0 to 70 °C;

DEMODULATORS (PINS 29 AND 30)

General

(R-Y) output signal amplitude (peak-to-

peak value)

(B-Y) output signal amplitude (peak-to-

peak value)

spread of signal amplitude ratio

between standards

output impedance (R-Y)/(B-Y) output

bandwidth of demodulators

-3 dB;

PAL/NTSC demodulator

gain between both demodulators G(B-

Y) and G(R-Y)

residual carrier output (peak-to-peak f = fosc; (R-Y) output

value); only valid for PAL and NTSC f = fosc; (B-Y) output

signals

f = 2fosc; (R-Y) output

f = 2fosc; (B-Y) output

H/2 ripple at (R-Y) output (peak-to-

peak value)

-5

-50

0

26

-

-30

-

-

-

±360

-

-

-

-

-

±35

-

-

-

-

-1,5

-

-

1,6

-

-

-

-

-

- +5 %

- +50 µA

- 30 %

- - dB

- 2 dB

- - dB

+3 - dB

+1 - dB

3-

±600

-

- Hz

2 deg

- 1 Hz/K

- 25 Hz

- 1k

- 15 pF

±40 - deg

0 - deg

0 - deg

1,05 - V

1,33 - V

- 1,5 dB

500 -

650 - kHz

1,78 1,96

- 10 mV

- 10 mV

- 10 mV

- 10 mV

- 25 mV

11

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet ILA8842.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ILA8842 | I2C BUS Controlled PAL/NTSC/Secam TV processor | IK Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |