|

|

PDF ICS9250-30 Data sheet ( Hoja de datos )

| Número de pieza | ICS9250-30 | |

| Descripción | Frequency Generator & Integrated Buffers for Celeron & PII/III | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS9250-30 (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

Integrated

Circuit

Systems, Inc.

ICS9250-30

Preliminary Product Preview

Frequency Generator & Integrated Buffers for Celeron & PII/III™

Recommended Application:

810/810E and Solano type chipset

Output Features:

• 2 - CPUs @ 2.5V, up to 200MHz.

• 13 - SDRAM @ 3.3V, up to 200MHz.

• 3 - 3V66 @ 3.3V, 2x PCI MHz.

• 8 - PCI @3.3V.

• 1 - 48MHz, @3.3V fixed.

• 1 - 24/48MHz @ 3.3V

• 1 - REF @3.3V, 14.318MHz.

Features:

• Support PC133 SDRAM.

• Up to 200MHz frequency support

• Support power management through PD#.

• Spread spectrum for EMI control

(± 0.25% Center Spread or 0 to -0.5% down spread)

• Uses external 14.318MHz crystal

• FS pins for frequency select

Key Specifications:

• CPU Output Jitter: <250ps

• CPU Output Skew: <175ps

• PCI Output Skew: <500ps

• 3V66 Output Skew <175ps

• For group skew timing, please refer to the

Group Timing Relationship Table.

Block Diagram

PLL2

X1 XTAL

X2 OSC

PLL1

Spread

Spectrum

FS[4:0]

PD#

SEL24_48#

SDATA

SCLK

Control

Logic

Config.

Reg.

/2

CPU

DIVDER

SDRAM

DIVDER

IOAPIC

DIVDER

PCI

DIVDER

3V66

DIVDER

48MHz

24_48MHz

REF0

2 CPUCLK [1:0]

12 SDRAM [11:0]

SDRAM_F

IOAPIC

PCICLK [7:0]

8

3V66 [2:0]

3

VDDREF

X1

X2

GNDREF

GND3V66

3V66-0

3V66-1

3V66-2

VDD3V66

VDDPCI

1*FS0/PCICLK0

1*FS1/PCICLK1

1*SEL24_48#/PCICLK2

GNDPCI

PCICLK3

PCICLK4

PCICLK5

VDDPCI

PCICLK6

PCICLK7

GNDPCI

PD#

SCLK

SDATA

VDDSDR

SDRAM11

SDRAM10

GNDSDR

Pin Configuration

1 56 REF0/FS4*1

2 55 VDDLAPIC

3 54 IOAPIC

4 53 VDDLCPU

5 52 CPUCLK0

6 51 CPUCLK1

7 50 GNDLCPU

8 49 GNDSDR

9 48 SDRAM0

10 47 SDRAM1

11 46 SDRAM2

12 45 VDDSDR

13 44 SDRAM3

14 43 SDRAM4

15 42 SDRAM5

16 41 GNDSDR

17 40 SDRAM6

18 39 SDRAM7

19 38 SDRAM_F

20 37 VDDSDR

21 36 GND48

22 35 24_48MHz/FS21*

23 34 48MHz/FS3*1

24 33 VDD48

25 32 VDDSDR

26 31 SDRAM8

27 30 SDRAM9

28 29 GNDSDR

56-Pin 300 mil SSOP

1. These pins will have 1.5 to 2X drive strength.

* 120K ohm pull-up to VDD on indicated inputs.

Functionality

FS4 FS3 FS2 FS1 FS0

00000

00011

00110

00111

01000

01011

01110

01111

10000

10001

10011

10111

11000

11001

11011

11111

CPU

66.67

68.33

80.00

83.00

100.00

103.00

115.00

200.00

133.33

166.67

137.00

160.00

133.33

166.67

137.00

160.00

SDRAM

100.00

102.50

120.00

124.50

100.00

103.00

115.00

200.00

133.33

166.67

137.00

160.00

100.00

125.00

102.75

120.00

3V66

66.67

68.33

80.00

83.00

66.67

68.67

76.67

66.67

66.67

83.34

68.50

80.00

66.67

83.34

68.50

80.00

PCI

33.33

34.17

40.00

41.50

33.33

34.33

38.33

33.33

33.33

41.67

34.25

40.00

33.33

41.67

34.25

40.00

For other hardware/I2C selectable frequencies please refer to

Byte 0 frequency select register.

9250-30 Rev A 10/03/00

Third party brands and names are the property of their respective owners.

PRODUCT PREVIEW documents contain information on new products

in the sampling or preproduction phase of development. Characteristic

data and other specifications are subject to change without notice.

1 page

ICS9250-30

Preliminary Product Preview

Absolute Maximum Ratings

Core Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . 4.6 V

I/O Supply Voltage . . . . . . . . . . . . . . . . . . . . . . . . . 3.6V

Logic Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . GND 0.5 V to VDD +0.5 V

Ambient Operating Temperature . . . . . . . . . . . . . . 0°C to +70°C

Storage Temperature . . . . . . . . . . . . . . . . . . . . . . . . 65°C to +150°C

Case Temperature . . . . . . . . . . . . . . . . . . . . . . . . . . 115°C

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. These ratings are stress

specifications only and functional operation of the device at these or any other conditions above those listed in the operational sections

of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect product

reliability.

Group Timing Relationship Table1

Group

CPU to SDRAM

CPU to 3V66

CPU 66MHz

SDRAM 100MHz

Offset Tolerance

2.5ns 500ps

7.5ns 500ps

CPU 100MHz

SDRAM 100MHz

Offset Tolerance

5.0ns 500ps

5.0ns 500ps

CPU 133MHz

SDRAM 100MHz

Offset Tolerance

0.0ns 500ps

0.0ns 500ps

CPU 133MHz

SDRAM 133MHz

Offset Tolerance

3.75ns 500ps

0.0ns 500ps

SDRAM to 3V66 0.0ns 500ps 0.0ns 500ps 0.0ns 500ps 3.75ns 500ps

3V66 to PCI

PCI to PCI

USB & DOT

1.5-3.5ns

0.0ns

Asynch

500ps

1.0ns

N/A

1.5-3.5ns

0.0ns

Asynch

500ps

1.0ns

N/A

1.5-3.5ns

0.0ns

Asynch

500ps

1.0ns

N/A

1.5 -3.5ns

0.0ns

Asynch

500ps

1.0ns

N/A

Electrical Characteristics - Input/Supply/Common Output Parameters

TA = 0 - 70C; Supply Voltage VDD = 3.3 V +5%, VDDL=2.5 V+ 5%(unless otherwise stated)

PARAMETER SYMBOL

CONDITIONS

MIN TYP MAX UNITS

Input High Voltage

Input Low Voltage

Input High Current

Input Low Current

Input Low Current

Operating

Supply Current

Power Down

Supply Current

VIH

VIL

IIH

IIL1

IIL2

IDD3.3OP

VIN = VDD

VIN = 0 V; Inputs with no pull-up resistors

VIN = 0 V; Inputs with pull-up resistors

CL = 0 pF; Select @ 66M

2

VSS-0.3

-5

-5

-200

IDD3.3PD CL = 0 pF; With input address to Vdd or GND

VDD+0.3

0.8

5

100

V

V

µA

µA

µA

mA

600 µA

Input frequency

Fi VDD = 3.3 V;

Pin Inductance

Input Capacitance1

Lpin

CIN Logic Inputs

Cout Out put pin capacitance

Transition Time1

Settling Time1

Clk Stabilization1

CINX

Ttrans

Ts

TSTAB

X1 & X2 pins

To 1st crossing of target Freq.

From 1st crossing to 1% target Freq.

From VDD = 3.3 V to 1% target Freq.

Delay

tPZH,tPZH output enable delay (all outputs)

tPLZ,tPZH output disable delay (all outputs)

1Guarenteed by design, not 100% tested in production.

14.318

7

5

6

27 45

3

3

3

1 10

1 10

MHz

nH

pF

pF

pF

mS

mS

mS

nS

nS

Third party brands and names are the property of their respective owners.

5

5 Page

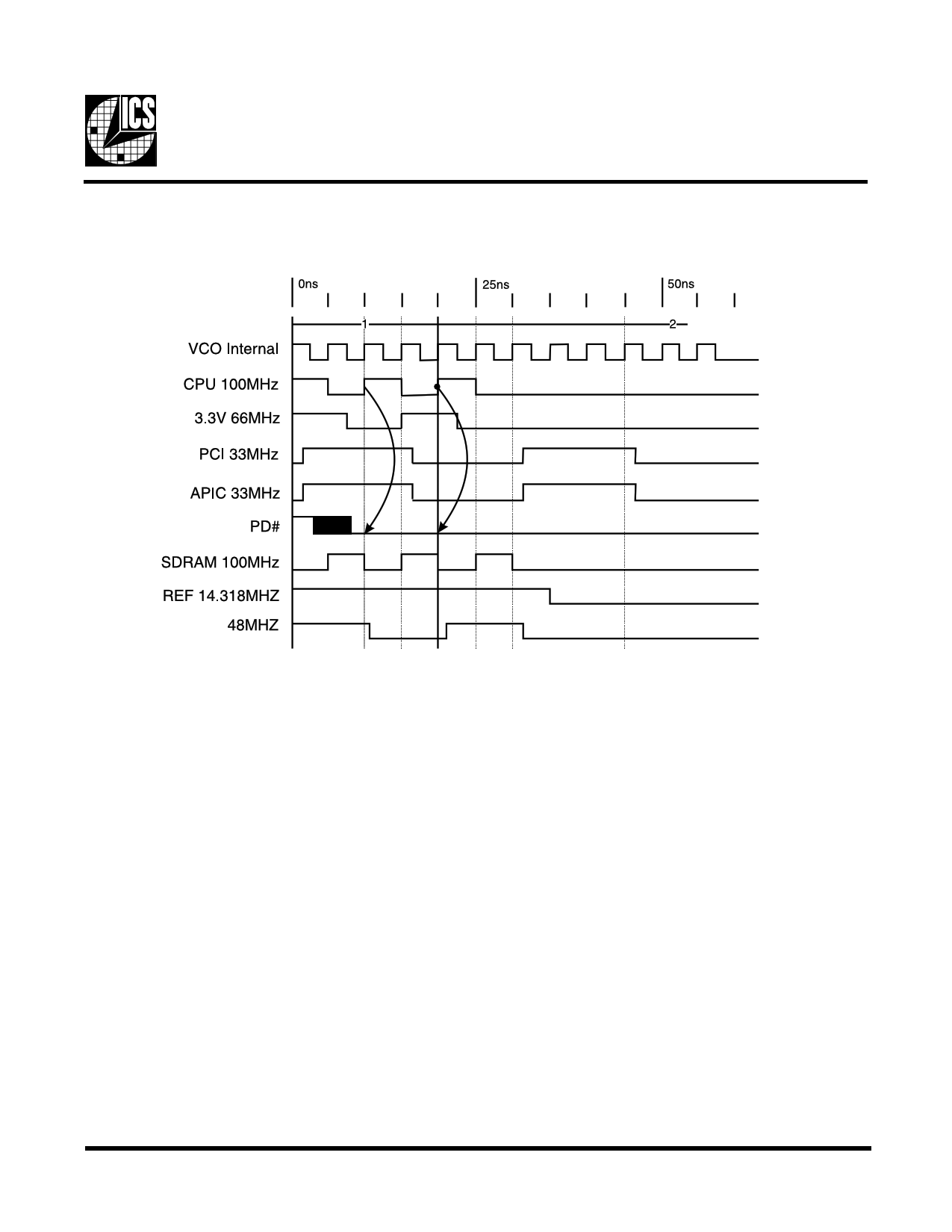

Power Down Waveform

ICS9250-30

Preliminary Product Preview

Note

1. After PD# is sampled active (Low) for 2 consective rising edges of CPUCLKs, all the

output clocks are driven Low on their next High to Low tranistiion.

2. Power-up latency <3ms.

3. Waveform shown for 100MHz

Third party brands and names are the property of their respective owners.

11

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet ICS9250-30.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS9250-30 | Frequency Generator & Integrated Buffers for Celeron & PII/III | Integrated Circuit Systems |

| ICS9250-32 | Frequency Generator & Integrated Buffers for PII/III | Integrated Circuit Systems |

| ICS9250-38 | Frequency Generator with 200MHz Differential CPU Clocks | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |