|

|

PDF XC2C64 Data sheet ( Hoja de datos )

| Número de pieza | XC2C64 | |

| Descripción | (XC2C32 - XC2C512) Coolrunner-ii CPLD Family | |

| Fabricantes | Xilinx | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de XC2C64 (archivo pdf) en la parte inferior de esta página. Total 14 Páginas | ||

|

No Preview Available !

0

R CoolRunner-II CPLD Family

DS090 (v1.7) October 2, 2003

0 0 Preliminary Product Specification

Features

• Optimized for 1.8V systems

- Industry’s fastest low power CPLD

- Static Icc of less than 100 microamps at all times

- Densities from 32 to 512 macrocells

• Industry’s best 0.18 micron CMOS CPLD

- Optimized architecture for effective logic synthesis

- Multi-voltage I/O operation — 1.5V to 3.3V

• Advanced system features

- Fastest in system programming

· 1.8V ISP using IEEE 1532 (JTAG) interface

- On-The-Fly Reconfiguration (OTF)

- IEEE1149.1 JTAG Boundary Scan Test

- Optional Schmitt trigger input (per pin)

- Unsurpassed low power management

- FZP 100% CMOS product term generation

- DataGATE external signal control

- Flexible clocking modes

· Optional DualEDGE triggered registers

· Clock divider (÷ 2,4,6,8,10,12,14,16)

· CoolCLOCK

- Global signal options with macrocell control

· Multiple global clocks with phase selection per

macrocell

· Multiple global output enables

· Global set/reset

- Abundant product term clocks, output enables and

set/resets

- Efficient control term clocks, output enables and

set/resets for each macrocell and shared across

function blocks

- Advanced design security

- Open-drain output option for Wired-OR and LED

drive

- Optional bus-hold or weak pullup on select I/O pins

- Optional configurable grounds on unused I/Os

- Mixed I/O voltages compatible with 1.5V, 1.8V,

2.5V, and 3.3V logic levels on all parts

· SSTL2-1,SSTL3-1, and HSTL-1 on 128 macro-

cell and denser devices

- PLA architecture

· Superior pinout retention

· 100% product term routability across function

block

- Hot pluggable

- Wide package availability including fine pitch:

· Chip Scale Package (CSP) BGA, Fine Line BGA,

TQFP, PQFP, VQFP, and PLCC packages

- Design entry/verification using Xilinx and industry

standard CAE tools

- Free software support for all densities using Xilinx

WebPACK™ or WebFITTER™ tools

- Industry leading nonvolatile 0.18 micron CMOS

process

- Guaranteed 1,000 program/erase cycles

- Guaranteed 20 year data retention

Family Overview

Xilinx CoolRunner™-II CPLDs deliver the high speed and

ease of use associated with the XC9500/XL/XV CPLD fam-

ily with the extremely low power versatility of the XPLA3™

family in a single CPLD. This means that the exact same

parts can be used for high-speed data communications/

computing systems and leading edge portable products,

with the added benefit of In System Programming. Low

power consumption and high-speed operation are com-

bined into a single family that is easy to use and cost effec-

tive. Xilinx patented Fast Zero Power™ (FZP) architecture

inherently delivers very low power performance without the

need for any special design measures. Clocking techniques

and other power saving features extend the users’ power

budget. The design features are supported starting with Xil-

inx ISE 4.1i, WebFITTER, and ISE WebPACK. Additional

details can be found in Further Reading, page 13.

Table 1 shows the macrocell capacity and key timing

parameters for the CoolRunner-II CPLD family.

Table 1: CoolRunner-II CPLD Family Parameters

XC2C32

XC2C64

omMacrocells

32 64

.cMax I/O

33 64

uTPD (ns)

t4TSU (ns)

eeTCO (ns)

hFSYSTEM1 (MHz)

3.5

1.7

2.8

333

4.0

2.0

3.0

270

XC2C128

128

100

4.5

2.1

3.4

263

XC2C256

256

184

5.0

2.2

3.8

238

XC2C384

384

240

5.5

2.3

4.2

217

XC2C512

512

270

6.0

2.4

4.6

217

atas© 2002 Xilinx, Inc. All rights reserved. All Xilinx trademarks, registered trademarks, patents, and disclaimers are as listed at http://www.xilinx.com/legal.htm.

.d All other trademarks and registered trademarks are the property of their respective owners. All specifications are subject to change without notice.

wDS090 (v1.7) October 2, 2003

wwPreliminary Product Specification

www.xilinx.com

1-800-255-7778

1

1 page

R CoolRunner-II CPLD Family

From AIM

40

49 P-terms

4 P-terms

To PTA, PTB, PTC of

other macrocells

CTC, CTR,

CTS, CTE

Fast Input

from

I/O Block

PTA

PTB

PTC

VCC

PTA

CTS

GSR

GND

GND

PLA OR Term

CTC

PTC

GCK0

GCK1

GCK2

PTA

CTR

GSR

GND

Feedback

to AIM

S

D/T

Q

PTC CE FIF

Latch

CK DualEDGE

R

To I/O Block

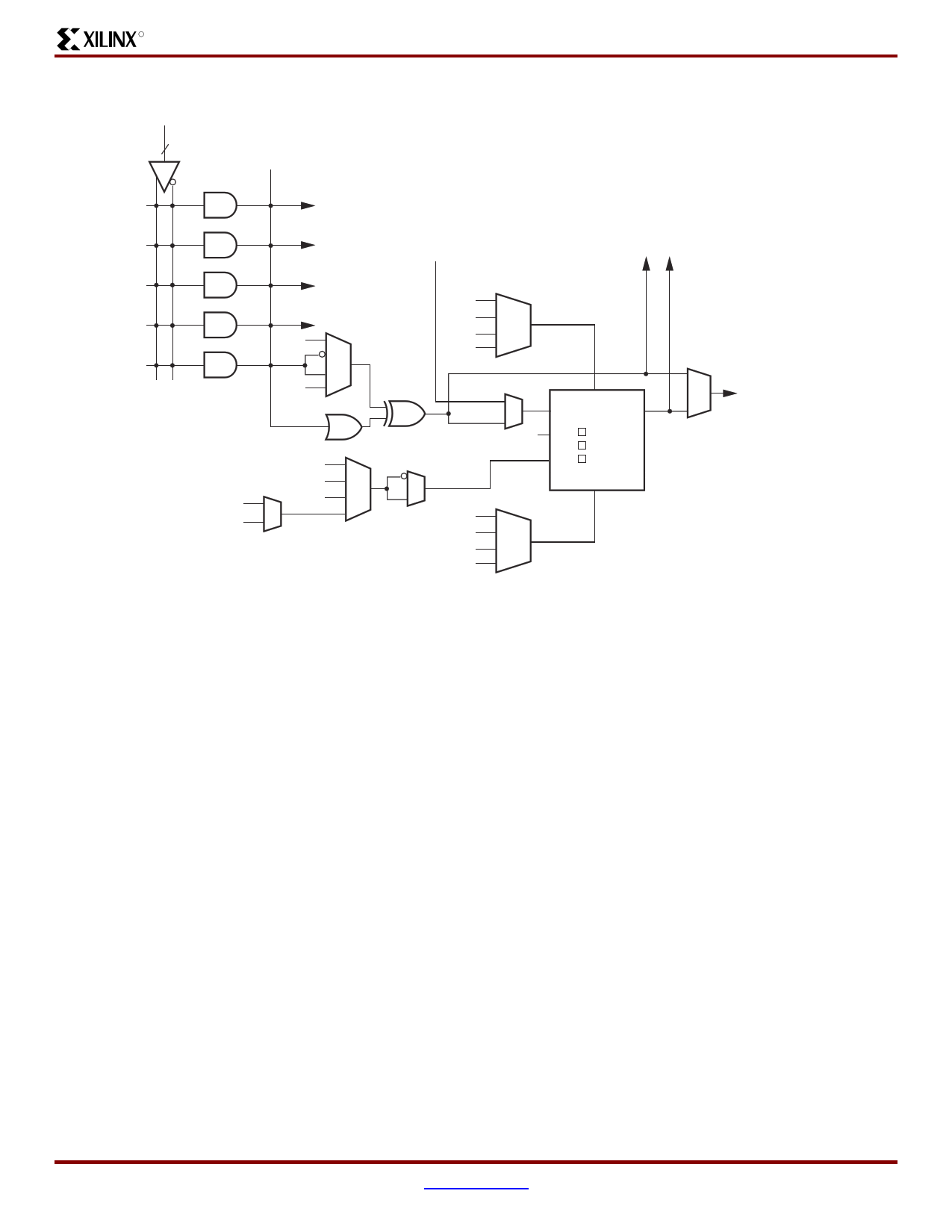

Figure 3: CoolRunner-II CPLD Macrocell

DS090_03_121201

When configured as a D-type flip-flop, each macrocell has

an optional clock enable signal permitting state hold while a

clock runs freely. Note that Control Terms (CT) are available

to be shared for key functions within the FB, and are gener-

ally used whenever the exact same logic function would be

repeatedly created at multiple macrocells. The CT product

terms are available for FB clocking (CTC), FB asynchro-

nous set (CTS), FB asynchronous reset (CTR), and FB out-

put enable (CTE).

Any macrocell flip-flop can be configured as an input regis-

ter or latch, which takes in the signal from the macrocell’s

I/O pin, and directly drives the AIM. The macrocell combina-

tional functionality is retained for use as a buried logic node

if needed. FToggle is the maximum clock frequency to which

a T flip-flop can reliably toggle.

Advanced Interconnect Matrix (AIM)

The Advanced Interconnect Matrix is a highly connected

low power rapid switch. The AIM is directed by the software

to deliver up to a set of 40 signals to each FB for the cre-

ation of logic. Results from all FB macrocells, as well as, all

pin inputs circulate back through the AIM for additional con-

nection available to all other FBs as dictated by the design

software. The AIM minimizes both propagation delay and

power as it makes attachments to the various FBs.

I/O Block

I/O blocks are primarily transceivers. However, each I/O is

either automatically compliant with standard voltage ranges

or can be programmed to become so.

In addition to voltage levels, each input can selectively

arrive through Schmitt-trigger inputs. This adds a small time

delay, but substantially reduces noise on that input pin.

Approximately 500 mV of hysteresis wil be added when

Schmitt-trigger inputs are selected. All LVCMOS inputs can

have hysteresis input. Hysteresis also allows easy genera-

tion of external clock circuits. The Schmitt-trigger path is

best seen in Figure 4.

Outputs can be directly driven, 3-stated or open-drain con-

figured. A choice of slow or fast slew rate output signal is

also available. Table 4 summarizes various supported volt-

age standards associated with specific part capacities. All

inputs and disabled outputs are voltage tolerant up to 3.3V.

The CoolRunner-II family supports SSTL2-1, SSTL3-1 and

HSTL-1 high-speed I/O standards in the 128-macrocell and

larger devices. Figure 4 details the I/O pin, where it is noted

that the inputs requiring comparison to an external refer-

ence voltage are available. These I/O standards all require

VREF pins for proper operation. The CoolRunner-II CPLD

allows any I/O pin to act as a VREF pin, granting the board

layout engineer extra freedom when laying out the

DS090 (v1.7) October 2, 2003

Preliminary Product Specification

www.xilinx.com

1-800-255-7778

5

5 Page

R CoolRunner-II CPLD Family

In System Programming

All CoolRunner-II CPLD parts are 1.8V in system program-

mable. This means they derive their programming voltage

and currents from the 1.8V VCC (internal supply voltage)

pins on the part. The VCCIO pins do not participate in this

operation, as they may assume another voltage ranging as

high as 3.3V down to 1.5V. A 1.8V VCC is required to prop-

erly operate the internal state machines and charge pumps

that reside within the CPLD to do the nonvolatile program-

ming operations. The JTAG interface buffers are powered

by a dedicated power pin, VCCAUX, which is independent of

all other supply pins. VCCAUX must be connected. Xilinx

software is provided to deliver the bit-stream to the CPLD

and drive the appropriate IEEE 1532 protocol. To that end,

there is a set of IEEE 1532 commands that are supported in

the CoolRunner-II CPLD parts. Programming times are less

than one second for 32 to 256 macrocell parts. Program-

ming times are less than four seconds for 384 and 512 mac-

rocell parts. Programming of CoolRunner-II CPLDs is only

guaranteed when operating in the commercial temperature

and voltage ranges as defined in the device-specific data

sheets.

On-The-Fly Reconfiguration (OTF)

Xilinx ISE 5.2i supports OTF for CoolRunner-II CPLDs. This

permits programming a new nonvolatile pattern into the part

while another pattern is currently in use. OTF has the same

voltage and temperature specifications as system program-

ming. During pattern transition I/O pins are in high imped-

ancewith weak pullup to VCCIO. Transition time typically

lasts between 50 and 100 µs, depending on density.

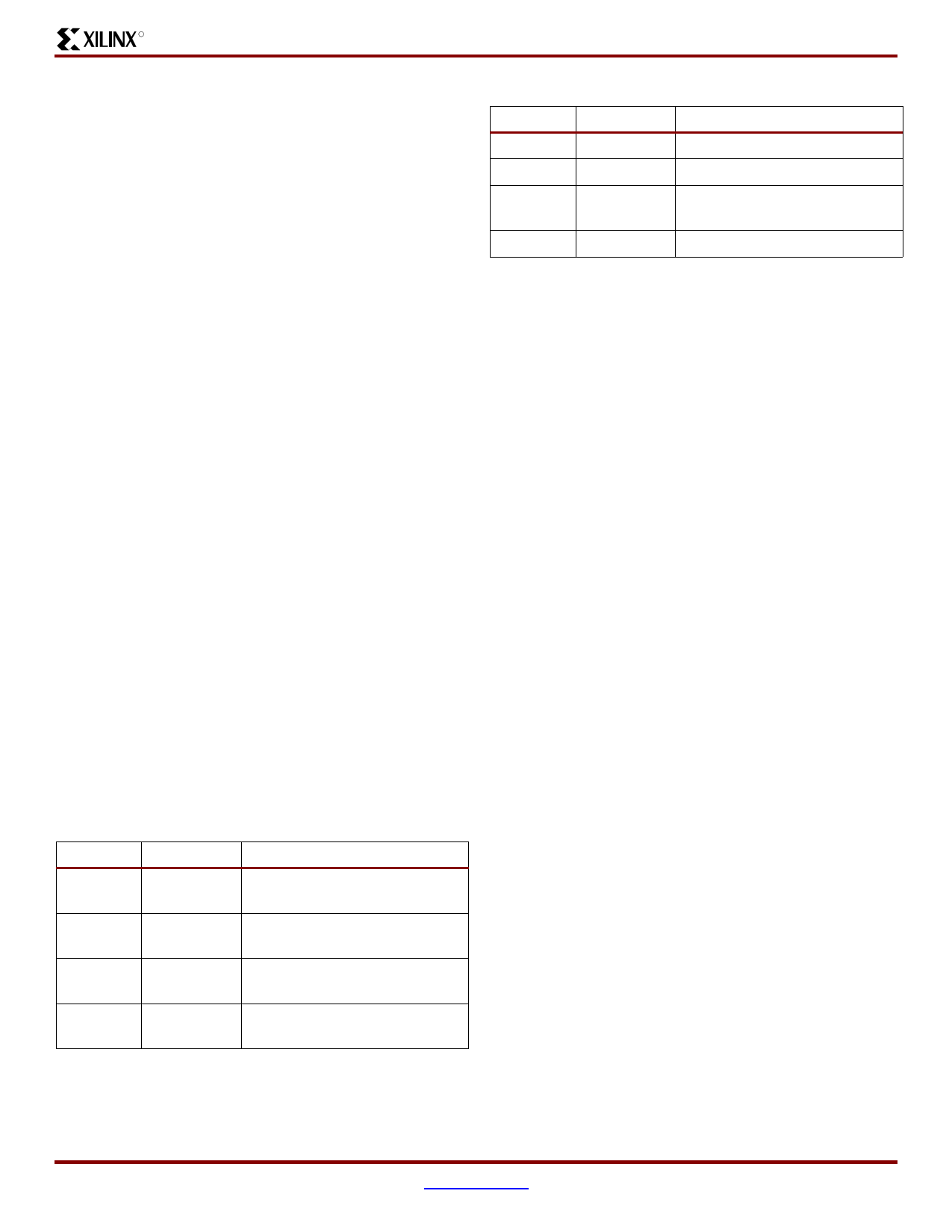

JTAG Instructions

Table 6 shows the commands available to users. These

same commands may be used by third party ATE products,

as well. The internal controllers can operate as fast as 66

MHz.

Table 6: JTAG Instructions

Code Instruction

Description

00000000 EXTEST Force boundary scan data onto

outputs

00000011 PRELOAD Latch macrocell data into

boundary scan cells

11111111 BYPASS Insert bypass register between

TDI and TDO

00000010 INTEST Force boundary scan data onto

inputs and feedbacks

Table 6: JTAG Instructions

Code Instruction

Description

00000001 IDCODE Read IDCODE

11111101 USERCODE Read USERCODE

11111100

HIGHZ

Force output into high

impedance state

11111010 CLAMP Latch present output state

Power-Up Characteristics

CoolRunner-II CPLD parts must operate under the

demands of both the high-speed and the portable market

places, therefore, they must support hot plugging for the

high-speed world and tolerate most any power sequence to

its various voltage pins. They must also not draw excessive

current during power-up initialization. To those ends, the

general behavior is summarized as follows:

1. I/O pins are disabled until the end of power-up.

2. As supply rises, configuration bits transfer from

nonvolatile memory to SRAM cells.

3. As power up completes, the outputs become as

configured (input, output, or I/O).

4. For specific configuration times and power up

requirements, see the device specific datasheet.

CoolRunner-II CPLD I/O pins are well behaved under all

operating conditions. During power-up, CoolRunner-II

devices employ internal circuitry which keeps the devices in

the quiescent state until the VCCINT supply voltage is at a

safe level (approximately 1.3V). In the quiescent state,

JTAG pins are disabled, and all device outputs are disabled

with the pins weakly pulled high, as shown in Table 7. When

the supply voltage reaches a safe level, all user registers

become initialized, and the device is immediately available

for operation, as shown in Figure 12. Best results are

obtained with a smooth VCC rise in less that 4 ms

If the device is in the erased state (before any user pattern

is programmed), the device outputs remain disabled with a

weak pull-up. The JTAG pins are enabled to allow the

device to be programmed at any time. All devices are

shipped in the erased state from the factory.

If the device is programmed, the device inputs and outputs

take on their configured states for normal operation. The

JTAG pins are enabled to allow device erasure or

boundary-scan tests at any time.

DS090 (v1.7) October 2, 2003

Preliminary Product Specification

www.xilinx.com

1-800-255-7778

11

11 Page | ||

| Páginas | Total 14 Páginas | |

| PDF Descargar | [ Datasheet XC2C64.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| XC2C64 | This lends power savings to High-end Communication equipment and speed to battery operated devices | Xilinx |

| XC2C64 | (XC2C32 - XC2C512) Coolrunner-ii CPLD Family | Xilinx |

| XC2C64A | CoolRunner-II CPLD | Xilinx |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |