|

|

PDF MAS3507D Data sheet ( Hoja de datos )

| Número de pieza | MAS3507D | |

| Descripción | Mpeg 1/2 Layer 2/3 Audio Decoder | |

| Fabricantes | Micronas Intermetall | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAS3507D (archivo pdf) en la parte inferior de esta página. Total 60 Páginas | ||

|

No Preview Available !

MICRONAS

PRELIMINARY DATA SHEET

MAS 3507D

MPEG 1/2 Layer 2/3

Audio Decoder

Edition March 16, 2000

6251-459-3PD

1 page

PRELIMINARY DATA SHEET

MAS 3507D

MPEG 1/2 Layer 2/3 Audio Decoder

Release Note: Revision bars indicate significant

changes to the previous edition.

This data sheet applies to MAS 3507D version G10

and following versions.

1. Introduction

The MAS 3507D is a single-chip MPEG layer 2/3 audio

decoder for use in audio broadcast or memory-based

playback applications. Due to embedded memories,

the embedded DC/DC up-converter, and the very low

power consumption, the MAS 3507D is ideally suited

for portable electronics.

In MPEG 1 (ISO 11172-3), three hierarchical layers of

compression have been standardized. The most

sophisticated and complex, layer 3, allows compres-

sion rates of approximately 12:1 for mono and stereo

signals while still maintaining CD audio quality. Layer 2

(widely used in DVB, ADR, and DAB) achieves a com-

pression of 8:1 providing CD quality.

In order to achieve better audio quality at low bit rates

(<64 kbit/s per audio channel), three additional sam-

pling frequencies are provided by MPEG 2

(ISO 13818-3). The MAS 3507D decodes both layer 2

and layer 3 bit streams as defined in MPEG 1 and 2.

The multichannel/multilingual capabilities defined by

MPEG 2 are not supported by the MAS 3507D. An

extension to the MPEG 2 layer 3 standard developed

by FhG Erlangen, Germany sometimes referenced as

MPEG 2.5, for extremely low bit rates at sampling fre-

quencies of 12, 11.025, or 8 kHz is also supported by

the MAS 3507D.

1.1. Features

– Serial asynchronous MPEG bit stream input (SDI)

– Parallel (PIO-DMA) Input

– Broadcast and multimedia operation mode

– Automatic locking to given data rate in broadcast

mode

– Data request triggered by ’demand signal’ in multi-

media mode

– Output audio data delivered (in various formats) via

an I2S bus (SDO)

– Digital volume / stereo channel mixer / Bass / Treble

– Output sampling clocks are generated and con-

trolled internally.

– Ancillary data provided via I2C interface

– Status information accessible via PIO pins or I2C

– “CRC Error” and “MPEG Frame Synchronization”

Indicators at Pins in serial input mode

– Power management for reduced power consumption

at lower sampling frequencies

– Low power dissipation (30 mW @ fs ≤ 12 kHz,

46 mW @ fs ≤ 24 kHz, 86 mW @ fs > 24 kHz @

2.7 V)

– Supply voltage range: 1.0 V to 3.6 V due to built-in

DC/DC converter (1-cell/2-cell battery operation)

– Adjustable power supply supervision

– Power-off function

– Additional functionality achievable via download

software (CELP voice Decoder, ADPCM encoder /

decoder)

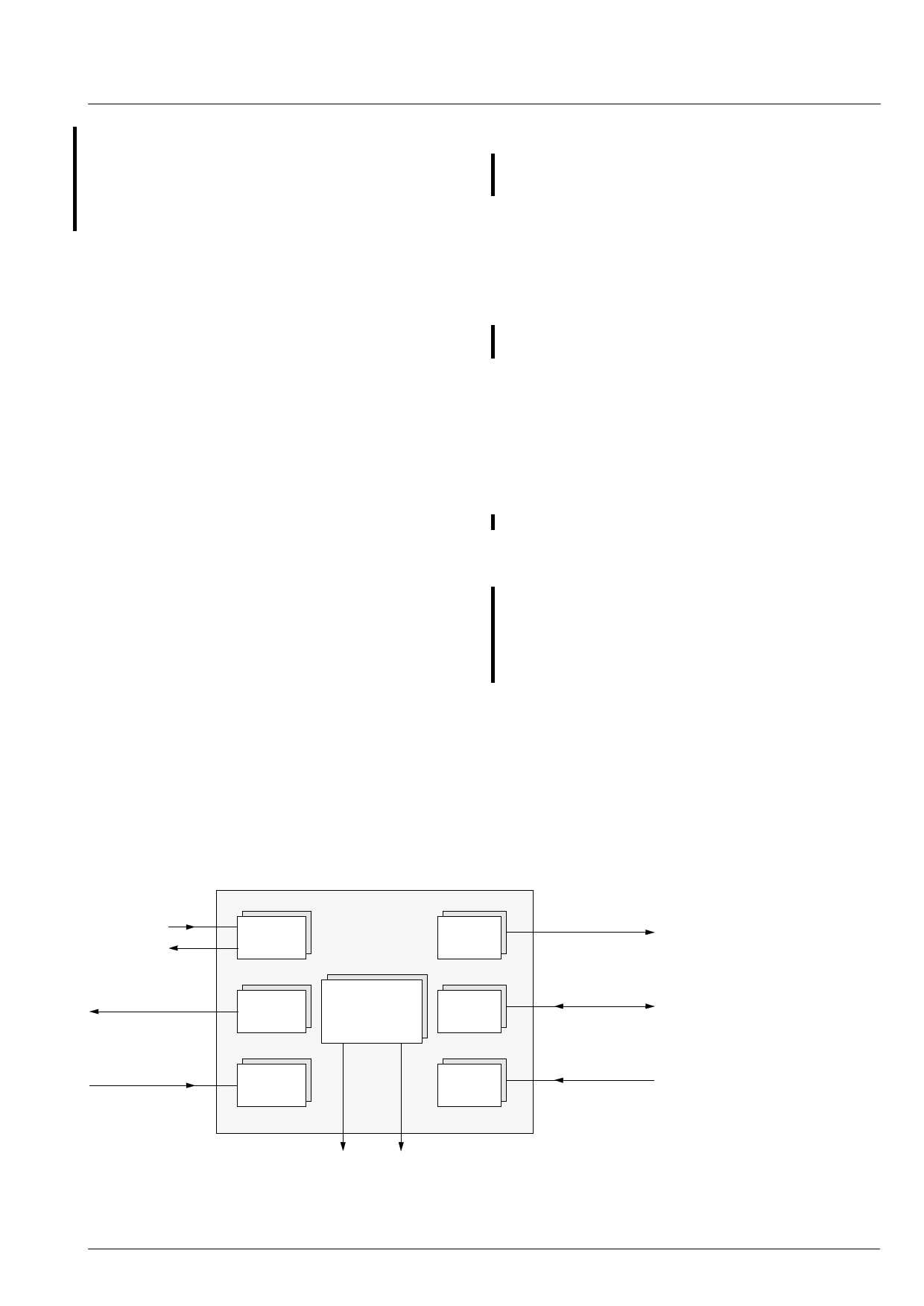

CLKI

CLKO

Clock

Synthesizer

MAS 3507D

DC/DC

Converter

decoded output

/3/

MPEG 1/2

audio bit stream

/2/

Serial Out

I2S

RISC DSP Core

Serial In

PIO

I2C

MPEG frame sync

Fig. 1–1: MAS 3507D block diagram

CRC error

Micronas

/3/

/8+5/

serial control

/2/

5

5 Page

PRELIMINARY DATA SHEET

MAS 3507D

2.7. Interfaces

The MAS 3507D uses an I2C control interface,

2 selectable serial input interfaces for MPEG bit

stream (SDI, SDI*) , a parallel I/O interface (PIO) for

MPEG- or ADPCM-data and a digital audio output

interface (SDO) for the decoded audio data (I2S or

similar). Additionally, the parallel I/O interface (PIO)

may be used for monitoring and mode selection tasks.

The PIO lines are defined by the internal firmware.

2.7.1. MPEG Bit Stream Interface (SDI)

The MPEG bit stream input interface uses the three

pins: SIC, SII, and SID. For MPEG decoding operation,

the SII pin must always be connected to VSS.

The serial interface has to be initialized before the

first use. Otherwise no output signal is produced.

After Power-up or a rising slope on Pin PORQ, write

the following I2C-command, while SIC is hold low:

W $3A 68 93 B0 00 02

(write $0020 into register $3B)

W $3A 68 00 01

(execute “RUN 1” command)

The MPEG input signal format is shown in Fig. 2–4.

The data values are latched with the falling edge of the

SIC signal.

The MPEG bit stream generated by an encoder is

unformatted. It will be formatted (e.g. 8 bit or 16 bit) by

storing on a media (Flash-RAM, Harddisk). The serial

data required from the MPEG bit stream interface must

be in the same bit order as produced by the encoder.

2.7.2. SDI* Selection

An alternative serial input (SDI*) is available. The alter-

native serial input can be selected by setting register

SI1M0 at address $4f (see Table 2–3).

Table 2–3: SDI* Selection via Register SI1M0,

$4f (write)

Value

0

2

Function

use SDI lines

use PI14...PI16 pins for

serial input (named SDI*)

Vh

SIC

Vl

Vh

SII

Vl

data valid

latch data at falling edge of clock

Vh

SID

Vl

Fig. 2–4: Schematic timing of the SDI (MPEG) input

Micronas

11

11 Page | ||

| Páginas | Total 60 Páginas | |

| PDF Descargar | [ Datasheet MAS3507D.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAS3507D | Mpeg 1/2 Layer 2/3 Audio Decoder | Micronas Intermetall |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |