|

|

PDF MAS3504D Data sheet ( Hoja de datos )

| Número de pieza | MAS3504D | |

| Descripción | G.729 Annex a Voice Codec | |

| Fabricantes | Micronas Intermetall | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAS3504D (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

MICRONAS

MAS 3504D

G.729 Annex A

Voice Codec

Edition Nov. 7, 2001

6251-522-1DS

MICRONAS

1 page

MAS 3504D

1.2. Application Overview

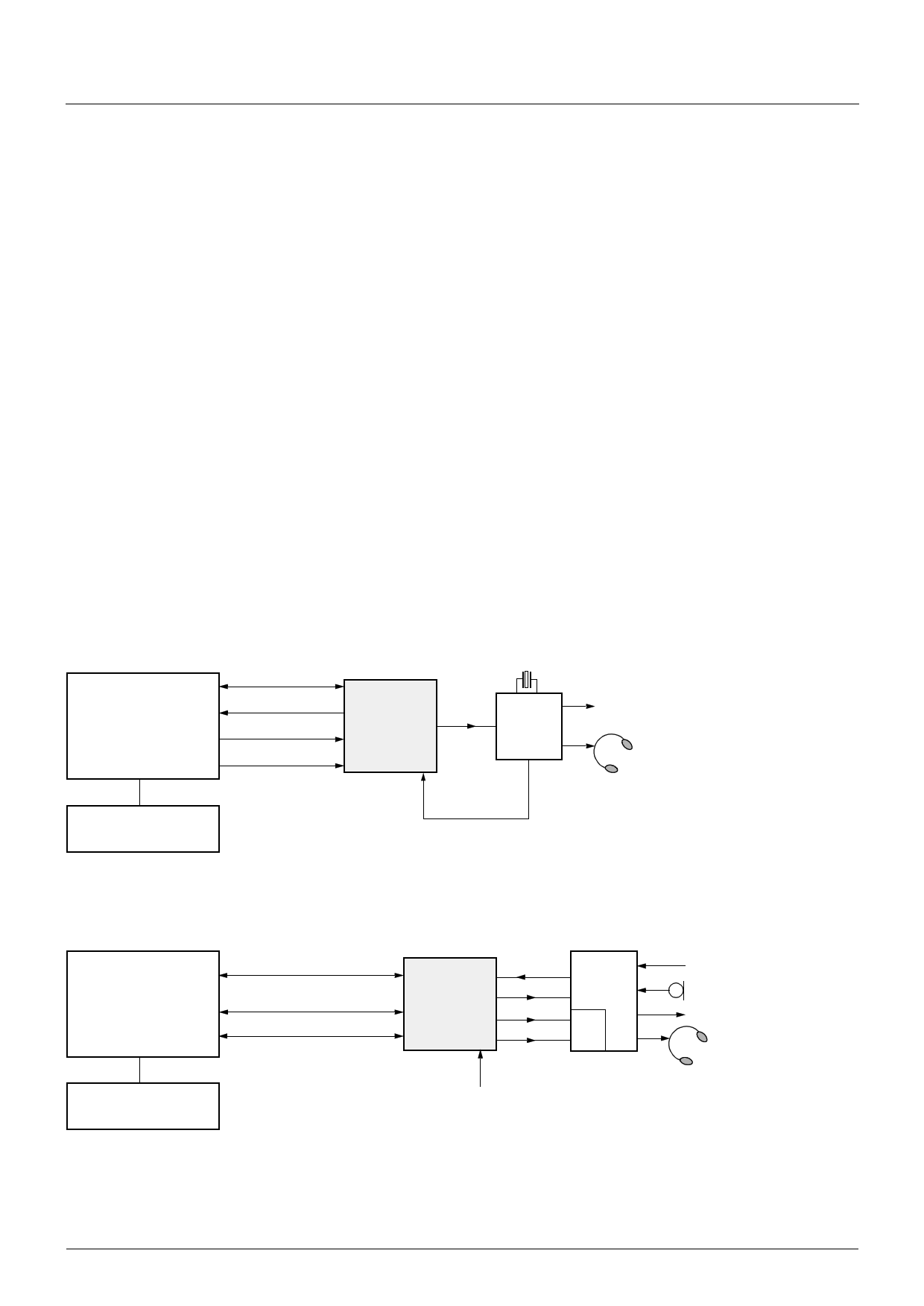

The MAS 3504D can be applied in two major environ-

ments: as standalone decoder or as encoder/decoder

combination. For decoding only mode, the DAC 3550A

fits perfectly to the requirements of the MAS 3504D. It

is a high-quality multi sample rate DAC (8 kHz..

50 kHz) with internal crystal oscillator, which is only

needed for generating the decoder Clock, and inte-

grated stereo headphone amplifier plus two stereo

inputs.

1.2.1. Decoder Mode

In a memory-based voice playback environment, the

decoding is started with a command from a controller.

Then the MAS 3504D continuously requests frames of

G.729 data every 10 ms via the parallel (PIO) inter-

face.

A delayed response of the host to the request signal

(max. 20 milliseconds) will be tolerated by the

MAS 3504D as long as the input buffer does not run

empty. A PC might use its DMA capabilities to transfer

the data in the background to the MAS 3504D without

interfering with its foreground processes.

The source of the bit stream may be a memory (e.g.

ROM, Flash) or PC peripherals, such as CD-ROM

drive, a hard disk or a floppy disk drive.

1.2.2. Encoder Mode

For encoding a support routine must be downloaded to

the MAS 3504D via I2C. After the encoder is started, it

begins to encode the incoming audio data and writes

the coded datastream to the parallel (PIO) interface.

A delayed response of the host to the data available

signal (max. 20 milliseconds) will be tolerated by the

MAS 3504D as long as the output buffer does not

overrun.

I2C 18.432 MHz

Host

(PC, Controller)

demand signal

I2S

demand clock MAS 3504D

DAC

3550A

G.729 bit stream

line out

ROM, CD-ROM,

RAM, Flash Mem. ..

CLKI

CLKOUT

Fig. 1–2: Block diagram of a MAS 3504D, decoding a stored bit stream in a decoding only application

Host

(PC, Controller)

I2C

Handshake signals

G.729 bit stream

ROM, CD-ROM,

RAM, Flash Mem. ..

data in

data out

MAS 3504D strobe

clock

I2S lines

CLKI

AD/DA

PLL

Fig. 1–3: Block diagram of a MAS 3504D in an encoding/decoding application

line in

Mic in

line out

Micronas

5

5 Page

MAS 3504D

2.6.5.1. Example 1:16 Bits/Sample (I2S Compatible Data Format)

A schematic timing diagram of the SDO interface in 16 bit/sample mode with delayed data by 1 clock cycle is shown

in Fig. 2–5.

Vh

SOC

Vl

Vh

SOD Vl

SOI Vh

Vl

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

left 16-bit audio sample

right 16-bit audio sample

Fig. 2–5: Schematic timing of the SDO interface in 16bit/sample mode

2.6.5.2. Example 2:32 Bit/Sample (Inverted SOI)

If the serial output generates 32 bits per audio sample, only the first 20 bits will carry valid audio data. The 12 trailing

bits are set to zero by default (see Fig. 2–6).

Vh

SOC

Vl

...

...

Vh

SOD

Vl

Vh

SOI Vl

31 30 29 28 27 26 25 ... 7 6 5 4 3 2 1 0 31 30 29 28 27 26 25 ... 7 6 5 4 3 2 1 0

left 32-bit audio sample

right 32-bit audio sample

Fig. 2–6: Schematic timing of the SDO interface in 32 bit/sample mode

Micronas

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet MAS3504D.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAS3504D | G.729 Annex a Voice Codec | Micronas Intermetall |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |