|

|

PDF DP8570A Data sheet ( Hoja de datos )

| Número de pieza | DP8570A | |

| Descripción | Timer Clock Peripheral (TCP) | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de DP8570A (archivo pdf) en la parte inferior de esta página. Total 26 Páginas | ||

|

No Preview Available !

May 1993

DP8570A Timer Clock Peripheral (TCP)

General Description

The DP8570A is intended for use in microprocessor based

systems where information is required for multi-tasking data

logging or general time of day date information This device

is implemented in low voltage silicon gate microCMOS tech-

nology to provide low standby power in battery back-up en-

vironments The circuit’s architecture is such that it looks

like a contiguous block of memory or I O ports The address

space is organized as 2 software selectable pages of 32

bytes This includes the Control Registers the Clock Coun-

ters the Alarm Compare RAM the Timers and their data

RAM and the Time Save RAM Any of the RAM locations

that are not being used for their intended purpose may be

used as general purpose CMOS RAM

Time and date are maintained from 1 100 of a second to

year and leap year in a BCD format 12 or 24 hour modes

Day of week day of month and day of year counters are

provided Time is controlled by an on-chip crystal oscillator

requiring only the addition of the crystal and two capacitors

The choice of crystal frequency is program selectable

Two independent multifunction 10 MHz 16-bit timers are

provided These timers operate in four modes Each has its

own prescaler and can select any of 8 possible clock inputs

Thus by programming the input clocks and the timer coun-

ter values a very wide range of timing durations can be

achieved The range is from about 400 ns (4 915 MHz oscil-

lator) to 65 535 seconds (18 hrs 12 min )

Power failure logic and control functions have been integrat-

ed on chip This logic is used by the TCP to issue a power fail

interrupt and lock out the mp interface The time power fails

may be logged into RAM automatically when VBB l VCC

Additionally two supply pins are provided When VBB l

VCC internal circuitry will automatically switch from the main

supply to the battery supply Status bits are provided to indi-

cate initial application of battery power system power and

low battery detect

(Continued)

Features

Y Full function real time clock calendar

12 24 hour mode timekeeping

Day of week and day of years counters

Four selectable oscillator frequencies

Parallel Resonant Oscillator

Y Two 16-bit timers

10 MHz external clock frequency

Programmable multi-function output

Flexible re-trigger facilities

Y Power fail features

Internal power supply switch to external battery

Power Supply Bus glitch protection

Automatic log of time into RAM at power failure

Y On-chip interrupt structure

Periodic alarm timer and power fail interrupts

Y Up to 44 bytes of CMOS RAM

Y INTR MFO T1 pins programmable High Low and push-

pull or open drain

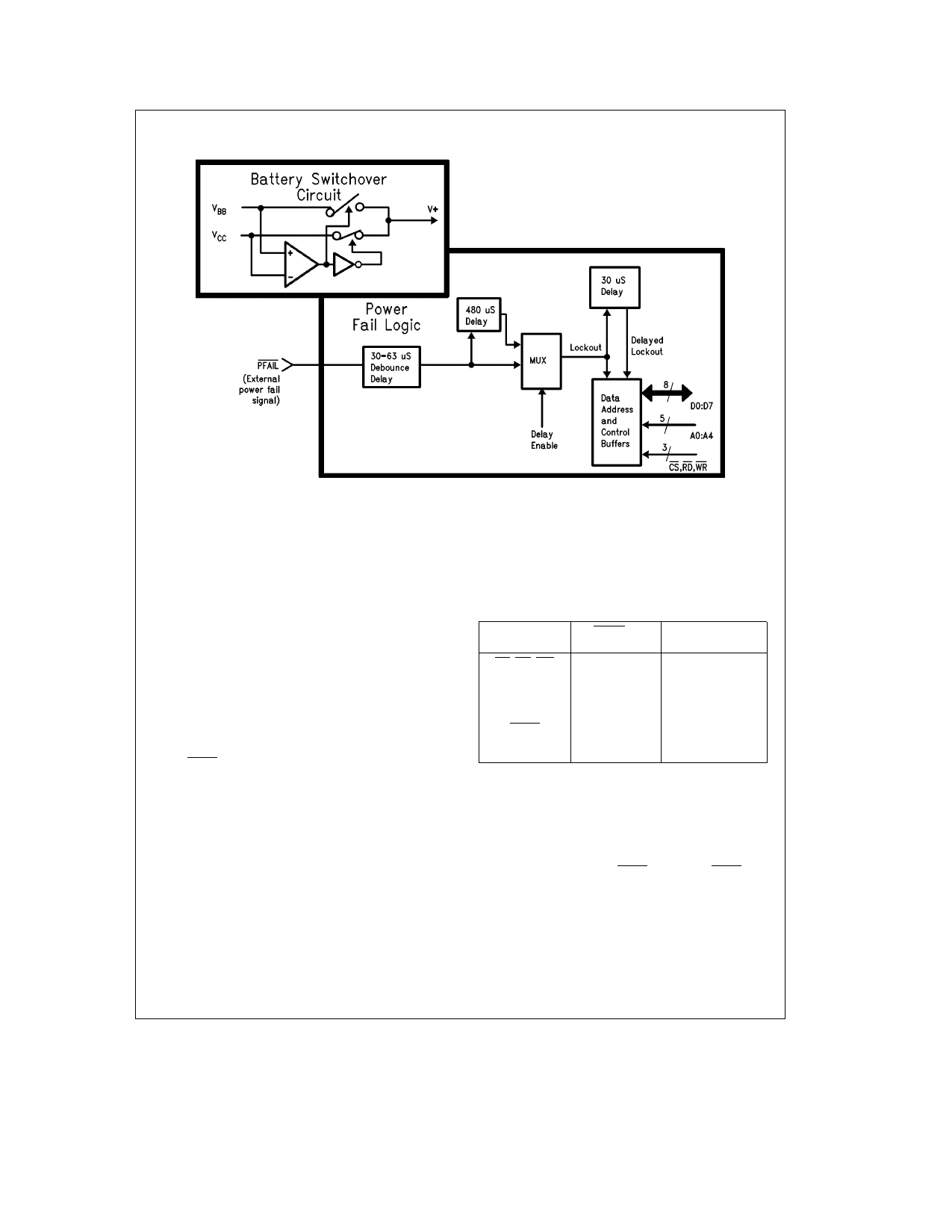

Block Diagram

TRI-STATE is a registered trademark of National Semiconductor Corporation

C1995 National Semiconductor Corporation TL F 8638

FIGURE 1

TL F 8638 – 1

RRD-B30M75 Printed in U S A

1 page

General Description (Continued)

The DP8570A’s interrupt structure provides four basic types

of interrupts Periodic Alarm Compare Timer and Power

Fail Interrupt mask and status registers enable the masking

and easy determination of each interrupt

One dedicated general purpose interrupt output is provided

A second interrupt output is available on the Multiple Func-

tion Output (MFO) pin Each of these may be selected to

generate an interrupt from any source Additionally the

MFO pin may be programmed to be either as oscillator out-

put or Timer 0’s output

Pin Description

CS RD WR (Inputs) These pins interface to mP control

lines The CS pin is an active low enable for the read and

write operations Read and Write pins are also active low

and enable reading or writing to the TCP All three pins are

disabled when power failure is detected However if a read

or write is in progress at this time it will be allowed to com-

plete its cycle

A0 – A4 (Inputs) These 5 pins are for register selection

They individually control which location is to be accessed

These inputs are disabled when power failure is detected

OSC IN (Input) OSC OUT (Output) These two pins are

used to connect the crystal to the internal parallel resonant

oscillator The oscillator is always running when power is

applied to VBB and VCC and the correct crystal select bits in

the Real Time Mode Register have been set

MFO (Output) The multi-function output can be used as a

second interrupt output for interrupting the mP This pin can

also provide an output for the oscillator or the internal Timer

0 The MFO output can be programmed active high or low

open drain or push-pull If in battery backed mode and a

pull-up resistor is attached it should be connected to a volt-

age no greater than VBB This pin is configured open drain

during battery operation (VBB l VCC)

INTR (Output) The interrupt output is used to interrupt the

processor when a timing event or power fail has occurred

and the respective interrupt has been enabled The INTR

output can be programmed active high or low push-pull or

open drain If in battery backed mode and a pull-up resistor

is attached it should be connected to a voltage no greater

than VBB This pin is configured open drain during battery

operation (VBB l VCC) The output is a DC voltage level To

clear the INTR write a 1 to the appropriate bit(s) in the Main

Status Register

D0 – D7 (Input Output) These 8 bidirectional pins connect

to the host mP’s data bus and are used to read from and

write to the TCP When the PFAIL pin goes low and a write

is not in progress these pins are at TRI-STATE

PFAIL (Input) In battery backed mode this pin can have a

digital signal applied to it via some external power detection

logic When PFAIL e logic 0 the TCP goes into a lockout

mode in a minimum of 30 ms or a maximum of 63 ms unless

lockout delay is programmed In the single power supply

mode this pin is not useable as an input and should be tied

to VCC Refer to section on Power Fail Functional Descrip-

tion

VBB (Battery Power Pin) This pin is connected to a back-

up power supply This power supply is switched to the inter-

nal circuitry when the VCC becomes lower than VBB Utiliz-

ing this pin eliminates the need for external logic to switch in

and out the back-up power supply If this feature is not to be

used then this pin must be tied to ground the TCP pro-

grammed for single power supply only and power applied to

the VCC pin

TCK G1 G0 (Inputs) T1 (Output) TCK is the clock input

to both timers when they have an external clock selected In

modes 0 1 and 2 G0 and G1 are active low enable inputs

for timers 0 and 1 respectively In mode 3 G0 and G1 are

positive edge triggers to the timers T1 is dedicated to the

timer 1 output The T1 output can be programmed active

high or low push-pull or open drain Timer 0 output is avail-

able through MFO pin if desired If in battery backed mode

and a pull-up resistor is attached to T1 it should be con-

nected to a voltage no greater than VBB The T1 pin is con-

figured open drain during battery operation (VBB l VCC)

VCC This is the main system power pin

GND This is the common ground power pin for both VBB

and VCC

Connection Diagrams

Dual-In-Line

Top View

Order Number DP8570AN

See NS Package Number N28B

Plastic Chip Carrier

TL F 8638 – 5

Top View

Order Number DP8570AV

See NS Package Number V28A

TL F 8638 – 6

5

5 Page

Functional Description (Continued)

FIGURE 6 System-Battery Switchover (Upper Left) Power Fail

and Lock-Out Circuits (Lower Right)

TL F 8638 – 8

The user may choose to have this power failed signal lock-

out the TCP’s data bus within 30 ms min 63 ms max or to

delay the lock-out to enable mP access after power failure is

detected This delay is enabled by setting the delay enable

bit in the Routing Register Also if the lock-out delay was

not enabled the TCP will disconnect itself from the bus with-

xin 30 ms min

63 ms max If chip select is low when a

power failure is detected a safety circuit will ensure that if a

read or write is held active continuously for greater than

30 ms after the power fail signal is asserted the lock-out will

be forced If a lock-out delay is enabled the DP8570A will

remain active for 480 ms after power fail is detected This

will enable the mP to perform last minute bookkeeping be-

fore total system collapse When the host CPU is finished

accessing the TCP it may force the bus lock-out before

480 ms has elapsed by resetting the delay enable bit

The battery switch over circuitry is completely independent

of the PFAIL pin A separate circuit compares VCC to the

VBB voltage As the main supply fails the TCP will continue

to operate from the VCC pin until VCC falls below the VBB

voltage At this time the battery supply is switched in VCC is

disconnected and the device is now in the standby mode If

indeterminate operation of the battery switch over circuit is

to be avoided then the voltage at the VCC pin must not be

allowed to equal the voltage at the VBB pin

After the generation of a lock-out signal and eventual

switch in of the battery supply the pins of the TCP will be

configured as shown in Table II Outputs that have a pull-up

resistor should be connected to a voltage no greater than

VBB

TABLE II Pin Isolation during a Power Failure

Pin

CS RD WR

A0 – A4

D0 – D7

Oscillator

TCK G0 G1

PFAIL

INTR MFO

T1

PFAIL e

Logic 0

Locked Out

Locked Out

Locked Out

Not Isolated

Not Isolated

Not Isolated

Not Isolated

Standby Mode

VBB l VCC

Locked Out

Locked Out

Locked Out

Not Isolated

Locked Out

Not Isolated

Open Drain

The Timer and Interrupt Power Fail Operation bits in the

Real-Time Mode Register determine whether or not the tim-

ers and interrupts will continue to function after a power fail

event

As power returns to the system the battery switch over cir-

cuit will switch back to VCC power as soon as it becomes

greater than the battery voltage The chip will remain in the

locked out state as long as PFAIL e 0 When PFAIL e 1

11

11 Page | ||

| Páginas | Total 26 Páginas | |

| PDF Descargar | [ Datasheet DP8570A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DP8570A | Timer Clock Peripheral (TCP) | National Semiconductor |

| DP8570A | DP8570A Timer Clock Peripheral (TCP) | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |