|

|

PDF UPD23C256112A Data sheet ( Hoja de datos )

| Número de pieza | UPD23C256112A | |

| Descripción | NAND INTERFACE 256M-BIT MASK-PROGRAMMABLE ROM | |

| Fabricantes | NEC | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de UPD23C256112A (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DATA SHEET

MOS INTEGRATED CIRCUIT

µ PD23C256112A

NAND INTERFACE

256M-BIT MASK-PROGRAMMABLE ROM

Description

The µPD23C256112A is a 256 Mbit NAND interface programmable mask read-only memory that operates with a

single power supply. The memory organization consists of (512 + 16 (Redundancy)) bytes x 32 pages x 2,048 blocks.

The µPD23C256112A is a serial type mask ROM in which addresses and commands are input and data output

serially via the I/O pins.

The µPD23C256112A is packed in 48-pin PLASTIC TSOP(I).

Features

• Word organization

(33,554,432 + 1,048,576Note) words by 8 bits

• Page size

(512 + 16Note) by 8 bits

• Block size

(16,384 + 512Note) by 8 bits

Note Underlined parts are redundancy.

Caution Redundancy is not programmable parts and is fixed to all FFH.

• Operation mode

READ mode (1), READ mode (2), READ mode (3), RESET, STATUS READ, ID READ

• Operating supply voltage : VCC = 3.3 ± 0.3 V

• Access Time

Memory cell array to starting address : 7 µs (MAX.)

Read cycle time

: 50 ns (MIN.)

/RE access time

: 35 ns (MAX.)

• Operating supply current

During read

: 30 mA (MAX.) (50 ns cycle operation)

During standby (CMOS) : 100 µA (MAX.)

Ordering Information

Part Number

µPD23C256112AGY-xxx-MJH

µPD23C256112AGY-xxx-MKH

(xxx : ROM code suffix No.)

Package

48-pin PLASTIC TSOP(I) (12x18) (Normal bent)

48-pin PLASTIC TSOP(I) (12x18) (Reverse bent)

The information in this document is subject to change without notice. Before using this document, please

confirm that this is the latest version.

Not all devices/types available in every country. Please check with local NEC representative for

availability and additional information.

Document No. M15902EJ2V0DS00 (2nd edition)

Date Published September 2002 NS CP (K)

Printed in Japan

The mark 5 shows major revised points.

©

2001

1 page

Block Diagram

I/O0

I/O1

I/O2

I/O3

I/O4

I/O5

I/O6

I/O7

/CE

CLE

ALE

/WE

/RE

Vcc

Vss

Status Register

ID Register

Command

Register

Address

Register

READ Contorol Circuit

READY/BUSY

Control Circuit

R, /B (Open-drain)

µPD23C256112A

Dara Register Circuit

Sense Amplifier

Y-Selector

Memory Cell Matrix

Data Sheet M15902EJ2V0DS

5

5 Page

µPD23C256112A

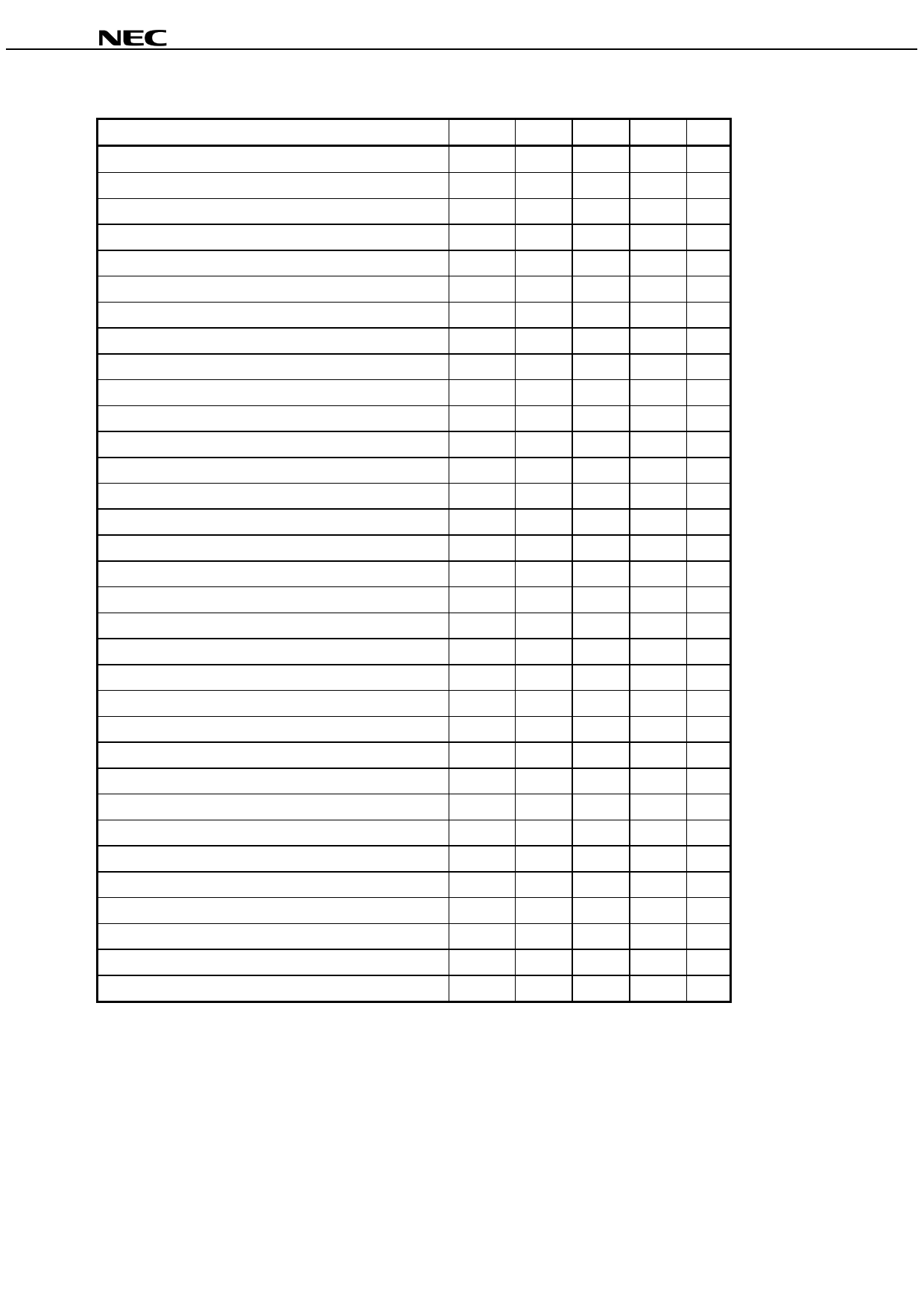

AC Characteristics (TA = 0 to 70°C, VCC = 3.3 ± 0.3 V)

Parameter

Symbol MIN TYP. MAX. Unit

CLE setup time

CLE hold time

/CE setup time

/CE hold time

Write pulse width

ALE setup time

ALE hold time

Data setup time

Data hold time

Write cycle time

/WE high hold time

Ready to /RE falling edge

Read pulse width

Read cycle time

/RE access time (serial data access)

/CE high hold time for last address in serial read cycle

/RE access time (ID read )

/RE high to output High-Z

/CE high to output High-Z

/RE high hold time

Output High-Z to /RE falling edge

/RE access time (status read)

/CE access time (status read)

/WE high to /CE low

/WE high to /RE low

ALE low to /RE low (ID read)

/CE low to /RE low (ID read)

Memory cell array to starting address

/WE high to Busy

ALE low to /RE low (read cycle)

/RE last clock rising edge to Busy (in sequential read)

/CE high to Ready (when interrupted by /CE in read mode)

Device reset time

tCLS

tCLH

tCS

tCH

tWP

tALS

tALH

tDS

tDH

tWC

tWH

tRR

tRP

tRC

tREA

tCEH

tREAID

tRHZ

tCHZ

tREH

tIR

tRSTO

tCSTO

tWHC

tWHR

tAR1

tCR

tR

tWB

tAR2

tRB

tCRYNote

tRST

0

10

0

10

25

0

10

20

10

50

15

20

35

50

100

10

15

0

30

30

100

100

50

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

35 ns

ns

35 ns

30 ns

20 ns

ns

ns

35 ns

45 ns

ns

ns

ns

ns

7 µs

200 ns

ns

200 ns

1 µs

6 µs

Note tCRY (time from /CE high to Ready) depends on the pull-up resister of the R, /B output pin.

Data Sheet M15902EJ2V0DS

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet UPD23C256112A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| UPD23C256112A | NAND INTERFACE 256M-BIT MASK-PROGRAMMABLE ROM | NEC |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |