|

|

PDF EPM1270 Data sheet ( Hoja de datos )

| Número de pieza | EPM1270 | |

| Descripción | (EPMxxxx) JTAG & In-System Programmability | |

| Fabricantes | Altera Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de EPM1270 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

Section I. MAX II Device

Family Data Sheet

This section provides designers with the data sheet specifications for

MAX® II devices. The chapters contain feature definitions of the internal

architecture, Joint Test Action Group (JTAG) and in-system

programmability (ISP) information, DC operating conditions, AC timing

parameters, and ordering information for MAX II devices.

This section includes the following chapters:

■ Chapter 1. Introduction

■ Chapter 2. MAX II Architecture

■ Chapter 3. JTAG & In-System Programmability

■ Chapter 4. Hot Socketing & Power-On Reset in MAX II Devices

■ Chapter 5. DC & Switching Characteristics

■ Chapter 6. Reference & Ordering Information

Altera Corporation

Section I–1

Preliminary

1 page

Introduction

1 For more information on equivalent macrocells, refer to the

MAX II Logic Element to Macrocell Conversion Methodology white

paper.

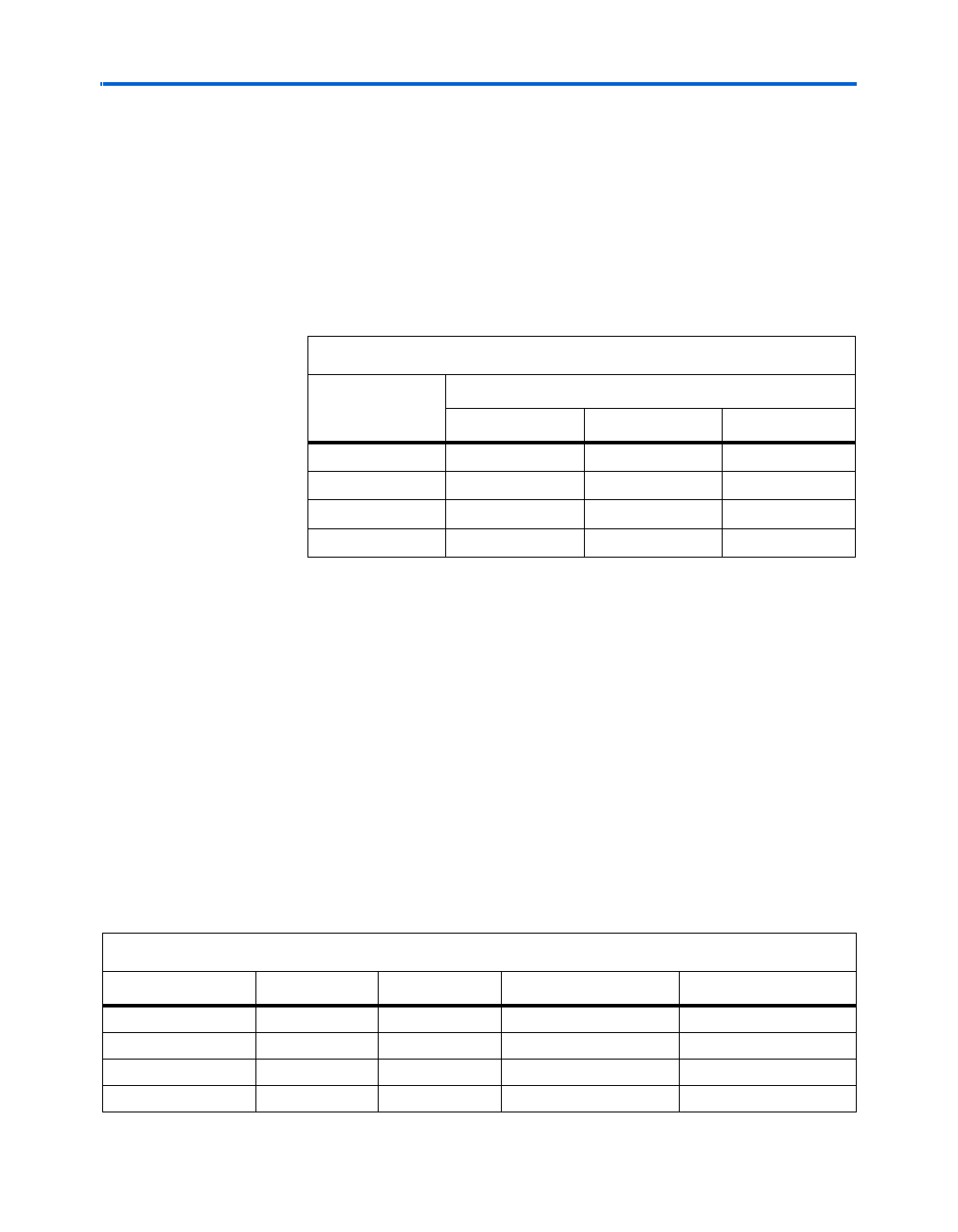

MAX II devices are available in three speed grades: -3, -4, -5 with -3 being

the fastest. These speed grades represent overall relative performance,

not any specific timing parameter. For propagation delay timing numbers

within each speed grade and density, see the chapter on DC & Switching

Characteristics. Table 1–2 shows MAX II device speed-grade offerings.

Table 1–2. MAX II Speed Grades

Device

EPM240

EPM570

EPM1270

EPM2210

-3

v

v

v

v

Speed Grade

-4

v

v

v

v

-5

v

v

v

v

MAX II devices are available in space-saving FineLine BGA® and thin

quad flat pack (TQFP) packages (see Tables 1–3 and 1–4). MAX II devices

support vertical migration within the same package (e.g., you can migrate

between the EPM570, EPM1270, and EPM2210 devices in the

256-pin FineLine BGA package). Vertical migration means that you can

migrate to devices whose dedicated pins and JTAG pins are the same and

power pins are subsets or supersets for a given package across device

densities. The largest density in any package has the highest number of

power pins; you must layout for the largest planned density in a package

to provide the necessary power pins for migration. For I/O pin migration

across densities, cross reference the available I/O pins using the device

pin-outs for all planned densities of a given package type to identify

which I/O pins can be migrated. The Quartus® II software can

automatically cross reference and place all pins for you when given a

device migration list.

Table 1–3. MAX II Packages & User I/O Pins

Device

EPM240

EPM570

EPM1270

EPM2210

100-Pin TQFP

80

76

144-Pin TQFP

116

116

256-Pin FineLine BGA 324-Pin FineLine BGA

160

212

204 272

Altera Corporation

December 2004

Core Version a.b.c variable

1–3

MAX II Device Handbook, Volume 1

5 Page

MAX II Architecture

within an LAB or adjacent LABs, allowing the use of local, LUT chain,

and register chain connections for performance and area efficiency.

Figure 2–3 shows the MAX II LAB.

Figure 2–3. MAX II LAB Structure

Row Interconnect

Fast I/O Connection

to IOE (1)

DirectLink

interconnect from

adjacent LAB

or IOE

DirectLink

interconnect to

adjacent LAB

or IOE

Logic Element

Note to Figure 2–3:

(1) Only from LABs adjacent to IOEs.

LE0

LE1

LE2

LE3

LE4

LE5

LE6

LE7

LE8

LE9

LAB

Local Interconnect

Column Interconnect

Fast I/O connection

to IOE (1)

DirectLink

interconnect from

adjacent LAB

or IOE

DirectLink

interconnect to

adjacent LAB

or IOE

LAB Interconnects

The LAB local interconnect can drive LEs within the same LAB. The LAB

local interconnect is driven by column and row interconnects and LE

outputs within the same LAB. Neighboring LABs, from the left and right

can also drive an LAB’s local interconnect through the DirectLink

connection. The DirectLink connection feature minimizes the use of row

and column interconnects, providing higher performance and flexibility.

Each LE can drive 30 other LEs through fast local and DirectLink

interconnects. Figure 2–4 shows the DirectLink connection.

Altera Corporation

December 2004

Core Version a.b.c variable

2–5

MAX II Device Handbook, Volume 1

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet EPM1270.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| EPM1270 | (EPMxxxx) JTAG & In-System Programmability | Altera Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |