|

|

PDF DS3254 Data sheet ( Hoja de datos )

| Número de pieza | DS3254 | |

| Descripción | (DS3251 - DS3254) Single / Dual / Triple / Quad DS3/E3/STS-1 LIUs | |

| Fabricantes | Maxim Integrated Products | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de DS3254 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

DS3251/DS3252/DS3253/DS3254

Single/Dual/Triple/Quad

DS3/E3/STS-1 LIUs

www.maxim-ic.com

GENERAL DESCRIPTION

The DS3251 (single), DS3252 (dual), DS3253

(triple), and DS3254 (quad) line interface units (LIUs)

perform the functions necessary for interfacing at the

physical layer to DS3, E3, or STS-1 lines. Each LIU

has independent receive and transmit paths and a

built-in jitter attenuator. An on-chip clock adapter

generates all line-rate clocks from a single input

clock. Control interface options include 8-bit parallel,

SPI, and hardware mode.

APPLICATIONS

SONET/SDH and PDH Multiplexers

Digital Cross-Connects

Access Concentrators

ATM and Frame Relay Equipment

Routers

PBXs

DSLAMs

CSU/DSUs

FUNCTIONAL DIAGRAM

LINE IN

DS3, E3,

OR STS-1

LINE OUT

DS3, E3,

OR STS-1

EACH LIU

RXP

RXN

CLK

DATA

Dallas

Semiconductor

DS325x

TXP

TXN

CLK

DATA

RECEIVE

CLOCK

AND DATA

CONTROL

STATUS

TRANSMIT

CLOCK

AND DATA

FEATURES

§ Pin-Compatible Family of Products

§ Each Port Independently Configurable

§ Receive Clock and Data Recovery for Up to 380

meters (DS3), 440 meters (E3), or 360 meters

(STS-1) of 75W Coaxial Cable

§ Standards-Compliant Transmit Waveshaping

§ Three Control Interface Options: 8-Bit Parallel,

SPI, and Hardware Mode

§ Built-In Jitter Attenuators can be Placed in Either

the Receive or Transmit Paths

§ Jitter Attenuators Have Provisionable Buffer

Depth: 16, 32, 64, or 128 Bits

§ Built-In Clock Adapter Generates All Line-Rate

Clocks from a Single Input Clock (DS3, E3,

STS-1, OC-3, 19.44MHz, 38.88MHz,

77.76MHz)

§ B3ZS/HDB3 Encoding and Decoding

§ Minimal External Components Required

§ Local and Remote Loopbacks

§ Low-Power 3.3V Operation (5V Tolerant I/O)

§ Industrial Temperature Range: -40°C to +85°C

§ Small Package: 144-Pin, 13mm x 13mm

Thermally Enhanced CSBGA

§ Drop-In Replacement for DS3151/52/53/54 LIUs

§ IEEE 1149.1 JTAG Support

Features continued on page 5.

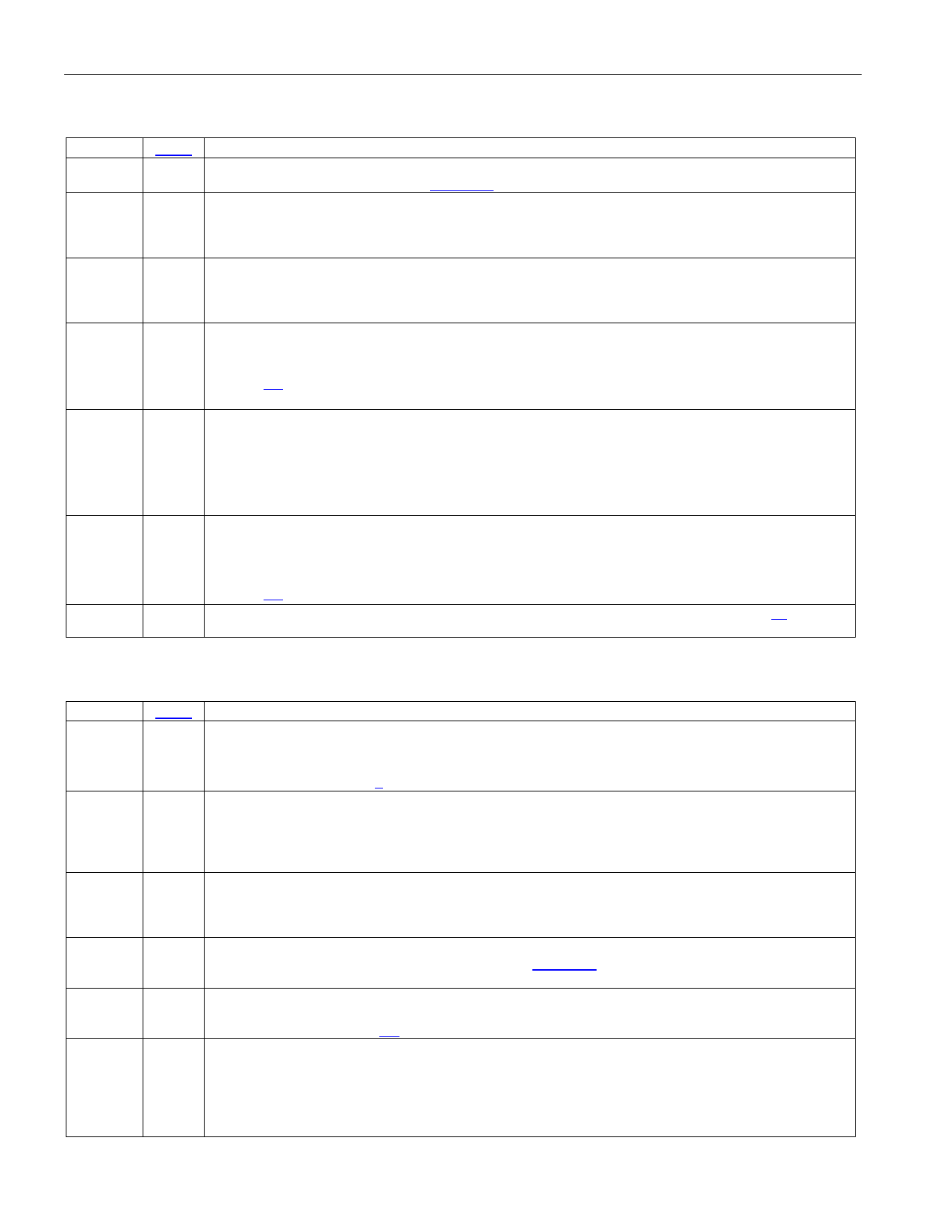

ORDERING INFORMATION

PART

LIU TEMP RANGE PIN-PACKAGE

DS3251

DS3251N

DS3252

DS3252N

DS3253

DS3253N

DS3254

DS3254N

1 0°C to +70°C 144 TE-CSBGA

1 -40°C to +85°C 144 TE-CSBGA

2 0°C to +70°C 144 TE-CSBGA

2 -40°C to +85°C 144 TE-CSBGA

3 0°C to +70°C 144 TE-CSBGA

3 -40°C to +85°C 144 TE-CSBGA

4 0°C to +70°C 144 TE-CSBGA

4 -40°C to +85°C 144 TE-CSBGA

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here: www.maxim-ic.com/errata.

1 of 71

REV: 061705

1 page

DS3251/DS3252/DS3253/DS3254

FEATURES (CONTINUED)

Receiver

§ AGC/equalizer block handles from 0 to 15dB of cable loss

§ Loss-of-lock (LOL) PLL status indication

§ Interfaces directly to a DSX monitor signal (~20dB flat loss) using built-in preamp

§ Digital and analog loss-of-signal (LOS) detectors (ANSI T1.231 and ITU G.775)

§ Optional B3ZS/HDB3 decoder

§ Line-code violation output pin and counter

§ Binary or bipolar framer interface

§ On-board 215 - 1 and 223 - 1 PRBS detector

§ Clock inversion for glueless interfacing

§ Tri-state clock and data outputs support protection switching applications

§ Per-channel power-down control

Transmitter

§ Binary or bipolar framer interface

§ Gapped clock capable up to 51.84MHz

§ Wide 50 ± 20% transmit clock duty cycle

§ Clock inversion for glueless interfacing

§ Optional B3ZS/HDB3 encoder

§ On-board 215 - 1 and 223 - 1 PRBS generator

§ Complete DS3 AIS generator (ANSI T1.107)

§ Unframed all-ones generator (E3 AIS)

§ Line build-out (LBO) control

§ Tri-state line driver outputs support protection switching applications

§ Per-channel power-down control

§ Output driver monitor

Jitter Attenuator

§ On-chip crystal-less jitter attenuator

§ Meets all applicable ANSI, ITU, ETSI and Telcordia jitter transfer and output jitter requirements

§ Can be placed in the transmit path, receive path or disabled

§ Selectable FIFO depth: 16, 32, 64 or 128 bits

§ Overflow and underflow status indications

Clock Adapter

§ Operates from a single DS3, E3, STS-1, 19.44 MHz, 38.88 MHz, or 77.76 MHz master clock

§ Synthesizes clock rates that are not provided externally

§ Use of common system timing frequencies such as 19.44 MHz eliminates the need for any local oscillators,

reduces cost and board space

§ Very small jitter gain and intrinsic jitter generation

§ Optionally provides synthesized clocks on output pins for use by neighboring components, such as framers or

mappers

Parallel CPU Interface

§ Multiplexed or nonmultiplexed 8-bit interface

§ Configurable for Intel mode (CS, WR, RD) or Motorola mode (CS, DS, R/W)

SPI CPU Interface

§ Operation up to 10 Mbit/s

§ Burst mode for multi-byte read and write accesses

§ Programmable clock polarity and phase

§ Half-duplex operation gives option to tie SDI and SDO together externally to reduce wire count

5 of 71

5 Page

DS3251/DS3252/DS3253/DS3254

Table 6-B. Receiver Pin Descriptions

Note: These pins are always active.

NAME

RXPn,

RXNn

RCLKn

RPOSn/

RDATn

RNEGn/

RLCVn

TYPE

I

O3

O3

O3

FUNCTION

Receiver Analog Inputs. These differential AMI inputs are coupled to the inbound 75W coaxial cable

through a 1:2 step-up transformer (Figure 2-1).

Receiver Clock. The recovered clock is output on the RCLK pin. Recovered data is output on the

RPOS/RDAT and RNEG/RLCV pins on the falling edge of RCLK (RCINV = 0) or the rising edge of

RCLK (RCINV = 1). During a loss of signal (RLOS = 0), the RCLK output signal is derived from the

LIU’s master clock.

Receiver Positive AMI/Receiver Data. When the receiver is configured to have a bipolar interface

(RBIN = 0), RPOS pulses high for each positive AMI pulse received. When the receiver is configured

to have a binary interface (RBIN = 1), RDAT outputs decoded binary data. RPOS/RDAT is updated

either on the falling edge of RCLK (RCINV = 0) or the rising edge of RCLK (RCINV = 1).

Receiver Negative AMI/Line-Code Violation. When the receiver is configured to have a bipolar

interface (RBIN = 0), RNEG pulses high for each negative AMI pulse received. When the receiver is

configured to have a binary interface (RBIN = 1), RLCV pulses high to flag code violations. See

Section 8.6 for further details on code violations. RNEG/RLCV is updated either on the falling edge of

RCLK (RCINV = 0) or the rising edge of RCLK (RCINV = 1).

RTSn

Receiver Tri-State Enable (Active Low). RTS tri-states the RPOS/RDAT, RNEG/RLCV, and RCLK

receiver outputs. This feature supports applications requiring LIU redundancy. Receiver outputs from

I

multiple LIUs can be wire-ORed together, eliminating the need for external switches or muxes. The

receiver continues to operate internally when RTS is low.

0 = tri-state the receiver outputs

1 = enable the receiver outputs

RLOSn

PRBSn

Receiver Loss of Signal (Active Low, Open Drain). RLOS is asserted upon detection of 175 ±75

consecutive zeros in the receive data stream. RLOS is deasserted when there are no excessive zero

O occurrences over a span of 175 ±75 clock periods. An excessive zero occurrence is defined as three

or more consecutive zeros in the DS3 and STS-1 modes or four or more zeros in the E3 mode. See

Section 8.5 for more information.

O

PRBS Detector Output. This signal reports the status of the PRBS detector. See Section 11 for

further details.

Table 6-C. Transmitter Pin Descriptions

Note: These pins are always active.

NAME TYPE

FUNCTION

TCLKn

TPOSn/

TDATn

TNEGn

TXPn,

TXNn

TDMn

TTSn

Transmitter Clock. A DS3 (44.736MHz ±20ppm), E3 (34.368MHz ±20ppm), or STS-1 (51.840MHz

I

±20ppm) clock should be applied at this signal. Data to be transmitted is clocked into the device at

TPOS/TDAT and TNEG either on the rising edge of TCLK (TCINV = 0) or the falling edge of TCLK

(TCINV = 1). See Section 9 for additional details.

Transmitter Positive AMI/Transmitter Data. When the transmitter is configured to have a bipolar

interface (TBIN = 0), a positive pulse is transmitted on the line when TPOS is high. When the

I transmitter is configured to have a binary interface (TBIN = 1), the data on TDAT is transmitted after

B3ZS or HDB3 encoding. TPOS/TDAT is sampled either on the rising edge of TCLK (TCINV = 0) or

on the falling edge of TCLK (TCINV = 1).

Transmitter Negative AMI. When the transmitter is configured to have a bipolar interface (TBIN = 0),

I

a negative pulse is transmitted on the line when TNEG is high. When the transmitter is configured to

have a binary interface (TBIN = 1), TNEG is ignored and should be wired either high or low. TNEG is

sampled either on the rising edge of TCLK (TCINV = 0) or on the falling edge of TCLK (TCINV = 1).

Transmitter Analog Outputs. These differential AMI outputs are coupled to the outbound 75W

O3 coaxial cable through a 2:1 step-down transformer (Figure 2-1). These outputs can be tri-stated using

the TTS pin or the TTS or TPS configuration bits.

Transmitter Driver Monitor (Active Low, Open Drain). TDM reports the status of the transmit driver

O monitor. When the monitor detects a faulty transmitter, TDM is driven low. TDM requires an external

pullup to VDD. See Section 9.6 for more information.

Transmitter Tri-State Enable (Active Low). TTS tri-states the transmitter outputs (TXP and TXN).

This feature supports applications requiring LIU redundancy. Transmitter outputs from multiple LIUs

I

can be wire-ORed together, eliminating external switches. The transmitter continues to operate

internally when TTS is active.

0 = tri-state the transmitter output driver

1 = enable the transmitter output driver

11 of 71

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet DS3254.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DS32506 | 6-/8-/12-Port DS3/E3/STS-1 LIU | Maxim Integrated Products |

| DS32508 | 6-/8-/12-Port DS3/E3/STS-1 LIU | Maxim Integrated Products |

| DS3251 | (DS3251 - DS3254) Single / Dual / Triple / Quad DS3/E3/STS-1 LIUs | Maxim Integrated Products |

| DS32512 | 6-/8-/12-Port DS3/E3/STS-1 LIU | Maxim Integrated Products |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |