|

|

PDF KMM53216000BK Data sheet ( Hoja de datos )

| Número de pieza | KMM53216000BK | |

| Descripción | 16MBx32 DRAM Simm Using 16MBx4 | |

| Fabricantes | Samsung Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de KMM53216000BK (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

DRAM MODULE

KMM53216000BK/BKG

KMM53216000BK/BKG Fast Page Mode

16M x 32 DRAM SIMM Using 16Mx4, 4K Refresh, 5V

GENERAL DESCRIPTION

The Samsung KMM53216000B is a 16Mx32bits Dynamic

RAM high density memory module. The Samsung

KMM53216000B consists of eight CMOS 16Mx4bits DRAMs

in SOJ packages mounted on a 72-pin glass-epoxy substrate.

A 0.1 or 0.22uF decoupling capacitor is mounted on the

printed circuit board for each DRAM. The KMM53216000B is

a Single In-line Memory Module with edge connections and is

intended for mounting into 72 pin edge connector sockets.

PERFORMANCE RANGE

Speed

-5

tRAC

50ns

tCAC

13ns

-6

60ns

15ns

tRC

90ns

110ns

tPC

35ns

40ns

FEATURES

• Part Identification

- KMM53216000BK(4K cycles/64ms Ref, SOJ, Solder)

- KMM53216000BKG(4K cycles/64ms Ref, SOJ, Gold)

• Fast Page Mode Operation

• CAS-before-RAS & Hidden Refresh capability

• RAS-only refresh capability

• TTL compatible inputs and outputs

• Single +5V±10% power supply

• JEDEC standard PDpin & pinout

• PCB : Height(1250mil), double sided component

PIN CONFIGURATIONS

Pin Symbol Pin Symbol

1 VSS 37 NC

2

DQ0

38

NC

3

DQ18

39

Vss

4

DQ1

40 CAS0

5 DQ19 41 CAS2

6

DQ2

42 CAS3

7 DQ20 43 CAS1

8

DQ3

44 RAS0

9

DQ21

45

NC

10 Vcc 46 NC

11 NC 47

W

12 A0 48 NC

13 A1 49 DQ9

14 A2 50 DQ27

15 A3 51 DQ10

16 A4 52 DQ28

17 A5 53 DQ11

18 A6 54 DQ29

19 A10 55 DQ12

20 DQ4 56 DQ30

21 DQ22 57 DQ13

22 DQ5 58 DQ31

23 DQ23 59

Vcc

24 DQ6 60 DQ32

25 DQ24 61 DQ14

26 DQ7 62 DQ33

27 DQ25 63 DQ15

28 A7 64 DQ34

29 A11 65 DQ16

30 Vcc 66 NC

31 A8 67 PD1

32 A9 68 PD2

33 NC 69 PD3

34 RAS2 70

PD4

35 NC 71 NC

36 NC 72 Vss

PIN NAMES

Pin Name

A0 - A11

DQ0-7, DQ9-16

DQ18-25, DQ27-34

Function

Address Inputs

Data In/Out

W

RAS0, RAS2

Read/Write Enable

Row Address Strobe

CAS0 - CAS3

PD1 -PD4

Vcc

Vss

Column Address Strobe

Presence Detect

Power(+5V)

Ground

NC No Connection

PRESENCE DETECT PINS (Optional)

Pin

PD1

PD2

PD3

PD4

50NS

Vss

NC

Vss

Vss

60NS

Vss

NC

NC

NC

SAMSUNG ELECTRONICS CO., LTD. reserves the right to

change products and specifications without notice.

1 page

DRAM MODULE

KMM53216000BK/BKG

AC CHARACTERISTICS (0°C≤TA≤70°C, VCC=5.0V±10%. See notes 1,2.)

Test condition : Vih/Vil=2.4/0.8V, Voh/Vol=2.4/0.4V, output loading CL=100pF

Parameter

Fast page mode cycle time

CAS precharge time(Fast page cycle)

RAS pulse width(Fast page cycle)

W to RAS precharge time(C-B-R refresh)

W to RAS hold time(C-B-R refresh)

Symbol

tPC

tCP

tRASP

tWRP

tWRH

-5

Min Max

35

10

50 200K

10

10

-6

Min Max

40

10

60 200K

10

10

Unit

ns

ns

ns

ns

ns

Note

NOTES

1. An initial pause of 200us is required after power-up followed

by any 8 RAS-only or CAS-before-RAS refresh cycles before

proper device operation is achieved.

6. This parameter defines the time at which the output achieves

the open circuit condition and is not referenced to VOH or

VOL.

2. Input voltage levels are Vih/Vil. VIH(min) and VIL(max) are ref-

erence levels for measuring timing of input signals. Transi-

tion times are measured between VIH(min) and VIL(max) and

are assumed to be 5ns for all inputs.

3. Measured with a load equivalent to 2 TTL loads and 100pF.

4. Operation within the tRCD(max) limit insures that tRAC(max)

can be met. tRCD(max) is specified as a reference point only.

If tRCD is greater than the specified tRCD(max) limit, then

access time is controlled exclusively by tCAC.

5. Assumes that tRCD≥tRCD(max).

7. tWCS is non-restrictive operating parameter. It is included in

the data sheet as electrical characteristics only. If

tWCS≥tWCS(min), the cycle is an early write cycle and the

data out pin will remain high impedance for the duration of

the cycle.

8. Either tRCH or tRRH must be satisfied for a read cycle.

9. These parameters are referenced to the CAS leading edge in

early write cycles.

10. Operation within the tRAD(max) limit insures that tRAC(max)

can be met. tRAD(max) is specified as reference point only. If

tRAD is greater than the specified tRAD(max) limit, then

access time is controlled by tAA.

5 Page

DRAM MODULE

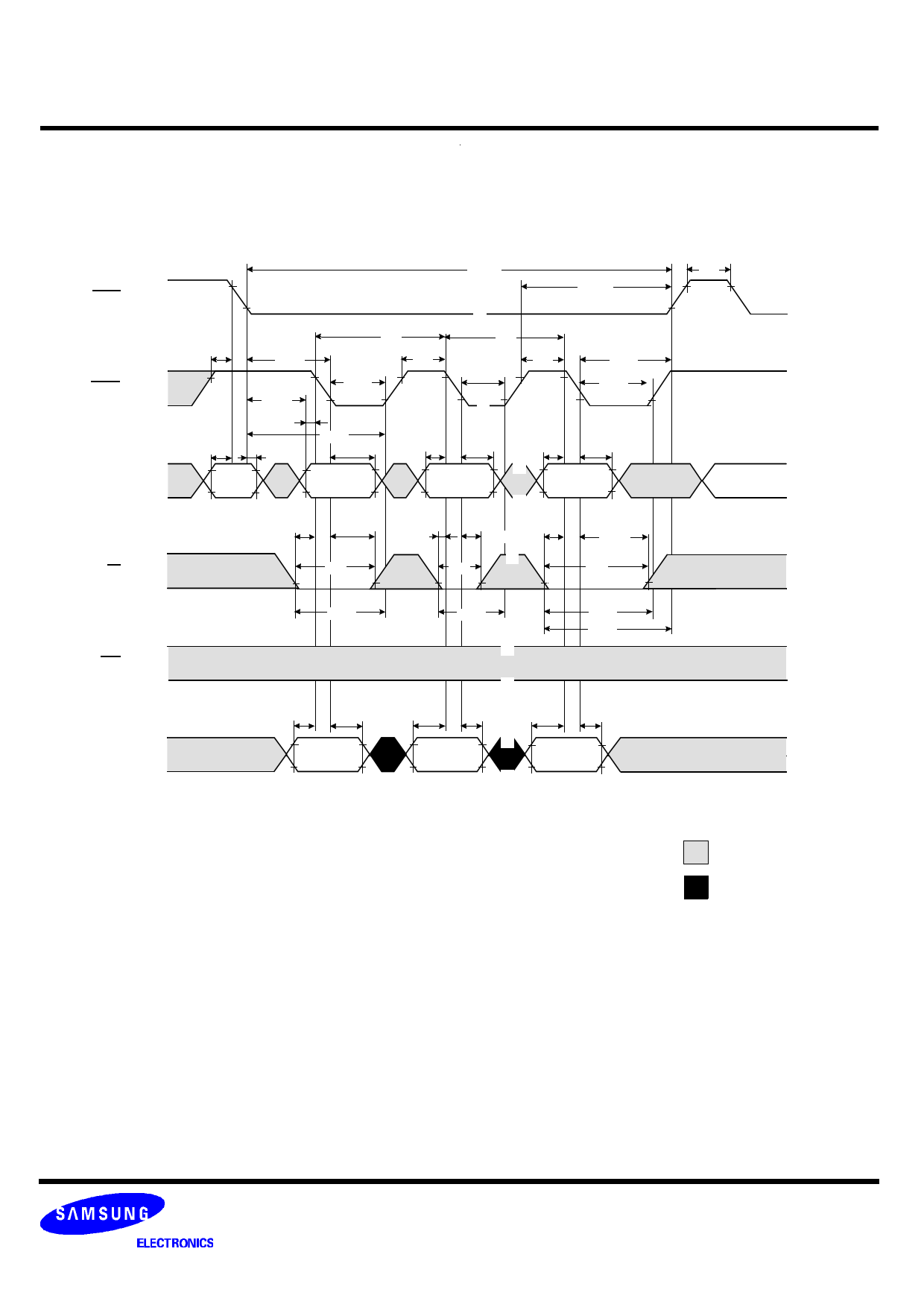

FAST PAGE WRITE CYCLE ( EARLY WRITE )

NOTE : DOUT = OPEN

KMM53216000BK/BKG

VIH -

RAS

VIL -

VIH -

CAS

VIL -

VIH -

A

VIL -

VIH -

W

VIL -

VIH -

OE

VIL -

VIH -

DQ

VIL -

tRASP

tRHCP

¡ó

tCRP

tASR

tRCD

tRAD

tASC

tRAH

tPC

tCAS

tCSH

tCAH

ROW

ADDR

COLUMN

ADDRESS

tPC

tCP tCP

tCAS

¡ó

tRSH

tCAS

tASC tCAH

COLUMN

ADDRESS

tASC tCAH

¡ó

COLUMN

¡ó ADDRESS

tWCS

tWCH

tWP

tWCS

tWCH tWCS

¡ó

tWP

tWCH

tWP

tCWL

tDS tDH

VALID

DATA-IN

tCWL

¡ó

tCWL

tRWL

¡ó

tDS tDH

VALID

DATA-IN

¡ó

¡ó

tDS tDH

VALID

DATA-IN

tRP

Don′t care

Undefined

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet KMM53216000BK.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| KMM53216000BK | 16MBx32 DRAM Simm Using 16MBx4 | Samsung Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |