|

|

PDF ICS91309 Data sheet ( Hoja de datos )

| Número de pieza | ICS91309 | |

| Descripción | High performance Communication Buffer | |

| Fabricantes | Integrated Circuit Systems | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de ICS91309 (archivo pdf) en la parte inferior de esta página. Total 9 Páginas | ||

|

No Preview Available !

Integrated

Circuit

Systems, Inc.

ICS91309

High Performance Communication Buffer

General Description

The ICS91309 is a high performance, low skew, low jitter

zero delay buffer. It uses a phase lock loop (PLL)

technology to align, in both phase and frequency, the REF

input with the CLKOUT signal. It is designed to distribute

high speed clocks in communication systems operating

at speeds from 10 to 133 MHz.

The ICS91309 provides synchronization between the

input and output. The synchronization is established via

CLKOUT feed back to the input of the PLL. Since the skew

between the input and output is less than +/- 350 pS, the

part acts as a zero delay buffer.

ICS91309 has two banks of four outputs controlled by two

address lines. Depending on the selected address line,

bank B or both banks can be put in a tri-state mode. In this

mode, the PLL is still running and only the output buffers

are put in a high impedance mode. The test mode shuts

off the PLL and connects the input directly to the output

buffers (see table below for functionality).

ICS91309 comes in a 16-pin 150 mil SOIC, SSOP or

4.40mm TSSOP package. In the absence of REF input,

the device will enter a powerdown mode. In this mode, the

PLL is turned off and the output buffers are pulled low.

Power down mode provides the lowest power consumption

for a standby condition.

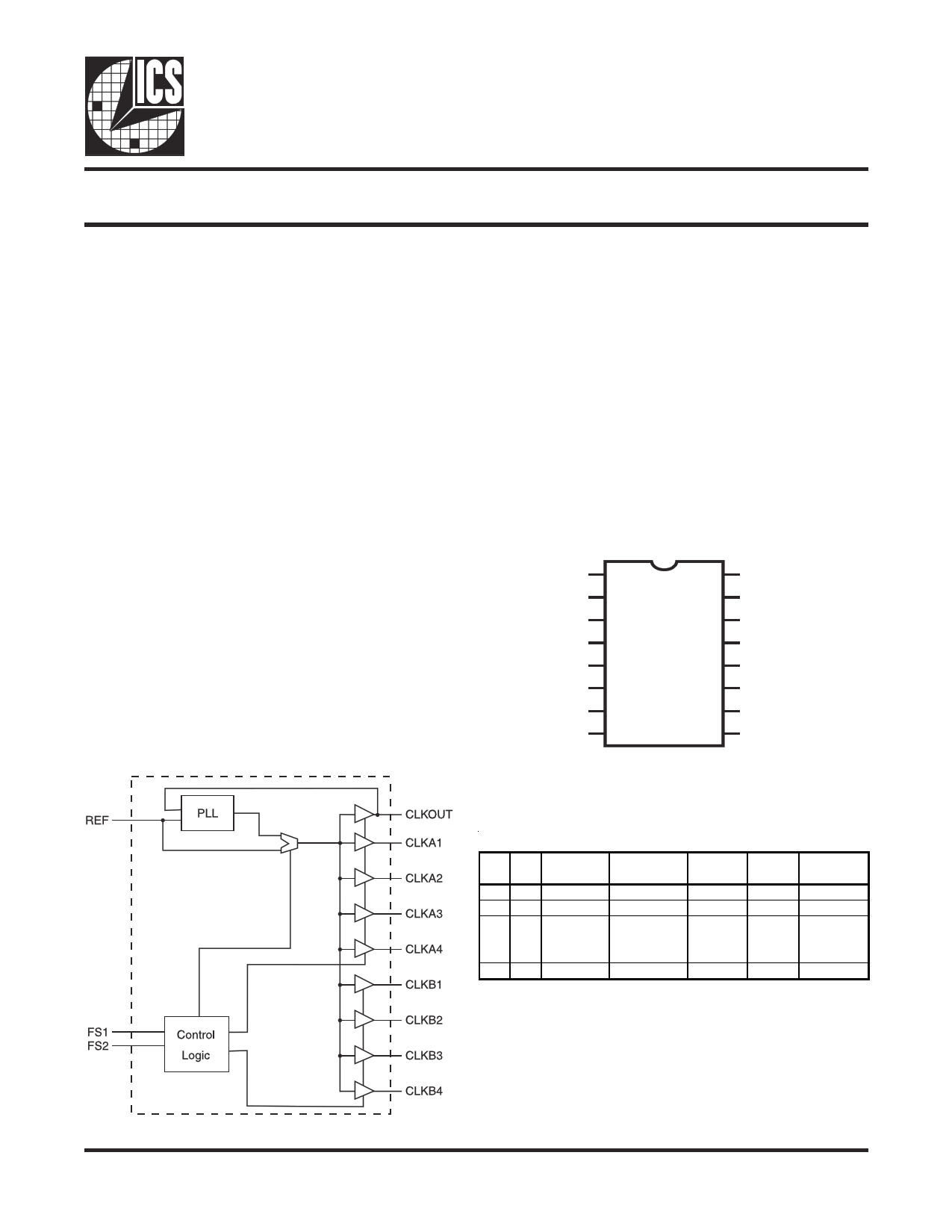

Block Diagram

Features

• Zero input - output delay

• Frequency range 10 - 133 MHz (3.3V)

• 5V tolerant input REF

• High loop filter bandwidth ideal for Spread Spectrum

applications.

• Less than 125 ps cycle to cycle Jitter

• Skew controlled outputs

• Available in 16 pin, 150 mil SSOP, SOIC & 4.40mm

TSSOP packages

• Skew: Group-to-Group: <215 ps

• Skew within Group: <100 ps

• Commercial temperature range: 0°C to +70°C

Pin Configuration

REF

CLKA1

CLKA2

VDD

GND

CLKB1

CLKB2

FS2

1

2

3

4

5

6

7

8

16 CLKOUT

15 CLKA4

14 CLKA3

13 VDD

12 GND

11 CLKB4

10 CLKB3

9 FS1

16 pin SSOP, SOIC & TSSOP

Functionality

FS2 FS1 CLKA(1:4)

CLKB(1:4)

CLKOUT

Ouput

Source

PLL

Shutdown

0 0 Tristate Tristate Driven PLL

N

0 1 Driven

Tristate Driven PLL

1

0

PLL

Bypass

Mode

PLL Bypass

Mode

PLL

Bypass

Mode

REF

1 1 Driven

Driven

Driven PLL

N

Y

N

0093G—02/11/04

1 page

ICS91309

Output to Output Skew

The skew between CLKOUT and the CLKA/B outputs is not dynamically adjusted by the PLL. Since CLKOUT is one

of the inputs to the PLL, zero phase difference is maintained from REF to CLKOUT. If all outputs are equally loaded,

zero phase difference will maintained from REF to all outputs.

If applications requiring zero output-output skew, all the outputs must equally loaded.

If the CLKA/B outputs are less loaded than CLKOUT, CLKA/B outputs will lead it; and if the CLKA/B is more loaded

than CLKOUT, CLKA/B will lag the CLKOUT.

Since the CLKOUT and the CLKA/B outputs are identical, they all start at the same time, but different loads cause them

to have different rise times and different times crossing the measurement thresholds.

REF input and

all outputs

loaded Equally

REF input and CLKA/B

outputs loaded equally, with

CLKOUT loaded More.

REF input and CLKA/B

outputs loaded equally, with

CLKOUT loaded Less.

0093G—02/11/04

Timing diagrams with different loading configurations

5

5 Page | ||

| Páginas | Total 9 Páginas | |

| PDF Descargar | [ Datasheet ICS91309.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| ICS91305 | High Performance Communication Buffer | Integrated Circuit Systems |

| ICS91305I | High Performance Communication Buffer | Integrated Circuit Systems |

| ICS91309 | High performance Communication Buffer | Integrated Circuit Systems |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |