|

|

PDF DA82562EZ Data sheet ( Hoja de datos )

| Número de pieza | DA82562EZ | |

| Descripción | 10/100 Mbps Platform LAN Connect | |

| Fabricantes | Intel | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de DA82562EZ (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

82562EZ 10/100 Mbps Platform LAN

Connect (PLC)

Networking Silicon

Datasheet

Product Features

■ IEEE 802.3 10BASE-T/100BASE-TX

compliant physical layer interface

■ IEEE 802.3u Auto-Negotiation support

■ Digital Adaptive Equalization control

■ Link status interrupt capability

■ XOR tree mode support

■ 3-port LED support (speed, link and

activity)

■ 10BASE-T auto-polarity correction

■ LAN Connect interface

■ 82540EM layout compatible

■ Diagnostic loopback mode

■ 1:1 transmit transformer ratio support

■ Low power (less than 300 mW in active

transmit mode)

■ Reduced power in “unplugged mode” (less

than 50 mW)

■ Automatic detection of “unplugged mode”

■ 3.3 V device

■ Thin BGA 15mm2 package

■ 82562EX with Alert on LAN support

available

■ Lead-freea 196-pin Ball Grid Array (BGA).

(Devices that are lead-free are marked with

a circled “e1” and have the product code:

LUxxxxxx.)

a.This device is lead-free. That is, lead has not been intentionally added, but lead may still exist as an impurity

at <1000 ppm. The Material Declaration Data Sheet, which includes lead impurity levels and the concentration

of other Restriction on Hazardous Substances (RoHS)-banned materials, is available at:

ftp://download.intel.com/design/packtech/material_content_IC_Package.pdf#pagemode=bookmark

In addition, this device has been tested and conforms to the same parametric specifications as previous versions

of the device.

For more information regarding lead-free products from Intel Corporation, contact your Intel Field Sales repre-

sentative.

Revision 1.5

January 2005

1 page

Networking Silicon — 82562EZ

Contents

1.0 Introduction......................................................................................................................... 1

1.1 Overview ............................................................................................................... 1

1.2 Scope .................................................................................................................... 1

1.3 Features ................................................................................................................ 1

1.4 Reference Documents...........................................................................................2

2.0 82562EZ Architectural Overview........................................................................................ 3

3.0 82562EZ Signal Descriptions ............................................................................................. 5

3.1 Signal Type Definitions ......................................................................................... 5

3.2 Twisted Pair Ethernet (TPE) Pins ......................................................................... 5

3.3 External Bias Pins ................................................................................................ 5

3.4 Clock Pins ............................................................................................................ 6

3.5 Platform LAN Connect Interface Pins.................................................................... 6

3.6 LED Pins ..............................................................................................................7

3.7 Miscellaneous Control Pins .................................................................................. 7

3.8 Power and Ground Connections .......................................................................... 8

4.0 Physical Layer Interface Functionality................................................................................ 9

4.1 100BASE-TX Mode ............................................................................................... 9

4.1.1 100BASE-TX Transmit Blocks .................................................................9

4.1.2 100BASE-TX Receive Blocks ................................................................11

4.2 10BASE-T Mode .................................................................................................12

4.2.1 10BASE-T Transmit Blocks ....................................................................12

4.2.2 10BASE-T Receive Blocks .....................................................................12

4.3 Analog References..............................................................................................13

4.4 Dynamic Reduced Power & Auto Plugging Detection.........................................14

4.4.1 Auto Plugging Detection.........................................................................14

4.4.2 Dynamic Reduced Power.......................................................................14

4.4.3 Configuration ..........................................................................................14

4.5 Reset ...................................................................................................................15

4.6 LAN Connect Interface ........................................................................................15

4.6.1 LAN Connect Clock ................................................................................15

4.6.2 LAN Connect Reset................................................................................15

4.7 LED Functionality ...............................................................................................15

5.0 Platform LAN Connect Registers .....................................................................................17

5.1 Medium Dependent Interface Registers 0 through 7...........................................17

5.1.1 Register 0: Control Register Bit Definitions ...........................................17

5.1.2 Register 1: Status Register Bit Definitions ............................................18

5.1.3 Register 2: PHY Identifier Register Bit Definitions ................................19

5.1.4 Register 3: PHY Identifier Register Bit Definitions ................................19

5.1.5 Register 4: Auto-Negotiation Advertisement Register Bit Definitions ....19

5.1.6 Register 5: Auto-Negotiation

Link Partner Ability Register Bit Definitions ...........................................20

5.1.7 Register 6: Auto-Negotiation Expansion Register Bit Definitions ..........20

5.2 Medium Dependent Interface Registers 8 through 15.........................................20

Datasheet

v

5 Page

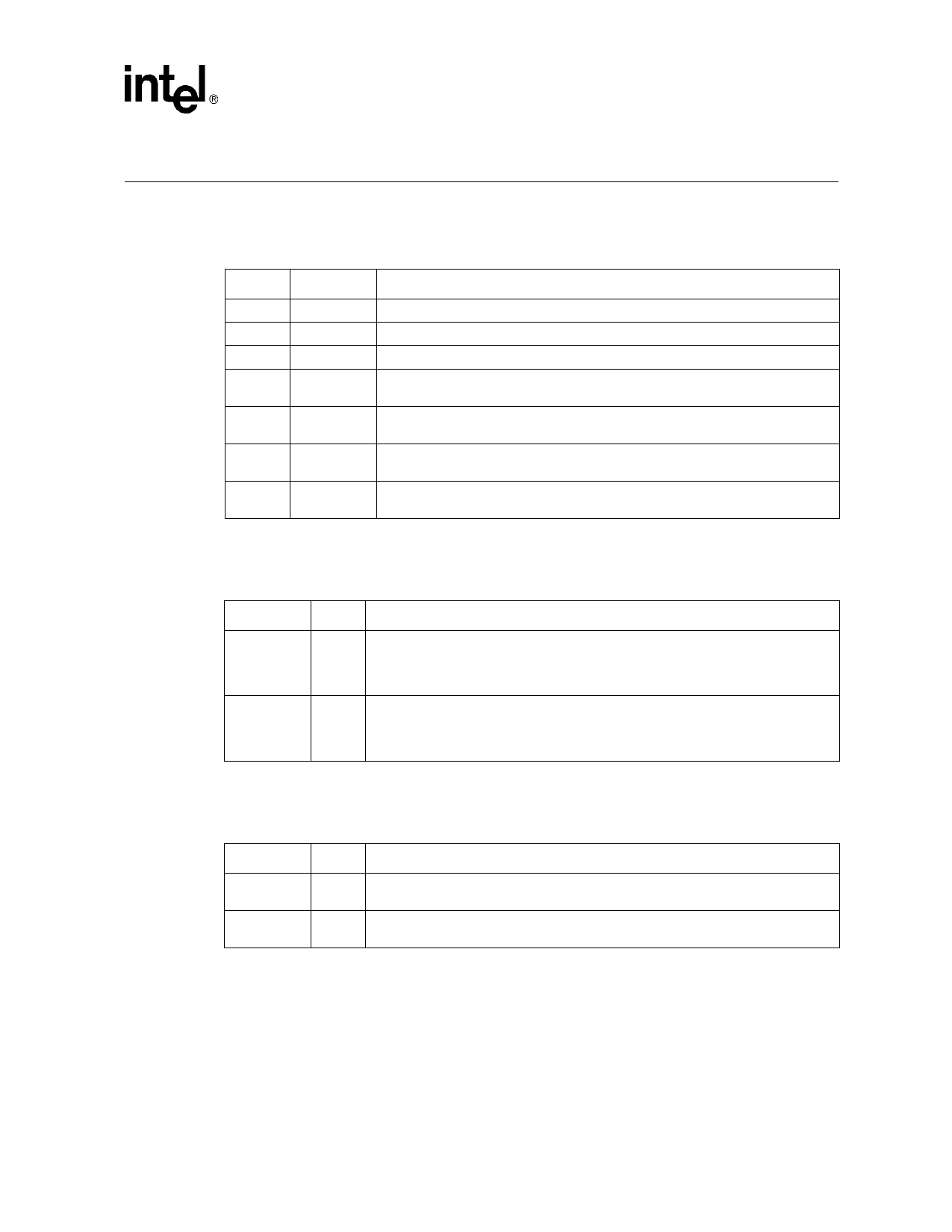

3.0

3.1

3.2

3.3

Networking Silicon — 82562EZ

82562EZ Signal Descriptions

Signal Type Definitions

Type

I

O

I/O

MLT

B

DPS

APS

Name

Description

Input

Input pin to the 82562EZ.

Output

Output pin from the 82562EZ.

Input/Output Multiplexed input and output pin to and from the 82562EZ.

Multi-level

analog I/O

Multi-level analog pin used for input and output.

Bias

Bias pin used for ground connection through a resistor or an external voltage

reference.

Digital Power

Supply

Digital power or ground pin for the 82562EZ.

Analog Power

Supply

Analog power or ground pin for the 82562EZ.

Twisted Pair Ethernet (TPE) Pins

Pin Name

TDP

TDN

RDP

RDN

Type

MLT

MLT

Description

Transmit Differential Pair. The transmit differential pair sends serial bit streams to

the unshielded twisted pair (UTP) cable. The differential pair is a two-level signal in

10BASE-T (Manchester) mode and a three-level signal in 100BASE-TX mode (MLT-

3). These signals directly interface with the isolation transformer.

Receive Differential Pair. The receive differential pair receive the serial bit stream

from an unshielded twisted pair (UTP) cable. The differential pair is a two-level signal

in 10BASE-T mode (Manchester) or a three-level signal in 100BASE-TX mode (MLT-

3). These signals directly interface with an isolation transformer.

External Bias Pins

Pin Name Type

Description

RBIAS100 B

RBIAS10

B

Reference Bias Resistor (100 Mbps). This pin should be connected to a pull-down

resistor.a

Reference Bias Resistor (10 Mbps). This pin should be connected to a pull-down

resistor.a

a. Based on some board designs, RBIAS100 and RBIAS10 values may need to be increased/decreased to compensate for high/

low MDI transmit amplitude. See the 82562EZ(EX)/82551ER(IT) & 82541ER Combined Footprint LOM Design Guide for more

information.

Datasheet

5

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet DA82562EZ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| DA82562ET | 10/100 Mbps Platform LAN Connect | Intel |

| DA82562EX | 10/100 Mbps Platform LAN Connect | Intel |

| DA82562EZ | 10/100 Mbps Platform LAN Connect | Intel |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |