|

|

PDF 29C516E Data sheet ( Hoja de datos )

| Número de pieza | 29C516E | |

| Descripción | 16 Bit Flow Through EDAC Error Detection And Correction unit | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de 29C516E (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

16–Bit Flow–Through EDAC

Error Detection And Correction unit

29C516E

1. Introduction

The 29C516E Atmel EDAC is a very low power

flow–through 16–bit Error Detection And Correction unit

(EDAC) with two user data buses. The EDAC is used in

a high integrity system for monitoring and correction of

data values coming from the memory space. During a

processor write cycle, at each memory location (16–bit

width), EDAC calculated checkword (6 or 8–bit width) is

added. When performing a read operation from memory,

the 29C516E verifies the entire checkword and data

combination. It detects and can correct 100% of all the

single–bit errors and it detects all double–bit errors.

When the 29C516E uses 6–checkbit, it can detect any

error on any single 4–bit memory chip. The 8–check–bit

option gives the additional capability to detect all errors

on any single 8–bit memory chip. All the errors are

signaled to the master system (via 2 error Flags) in order

to allow the processor to make the required action.

The 29C516E operates in two possible modes: corrected

or detected mode. In the corrected mode, the single–bit in

error is complemented (corrected). Then, the available

entire data is placed on the output port and the Correctable

Error Flag is set. In case of double–bit errors (or more),

the corrupted data is placed on the output port and the

Uncorrectable Error Flag is set. Note that when there is

more than two errors, then some bit patterns may appear

as possible correctable errors. Therefore, if the

environment produces this type of error, the EDAC must

be used in detect and provide no automatic correction.

Data and syndrome analysis must be done.

The 29C516E acts as a data buffer for µP–memory

interfacing. A flow–through EDAC is placed in the data

bus path, between the processor and the memory to be

protected. This component is able to serve two different

users of one memory space. So, it forms the interface

between the 22/24–bit (16+6/16+8) memory data bus and

the two 16–bit processor data busses with a high drive

capability (–12.8 mA). The two data ports can be used to

create a dual port bus in front of memory space. The

User–1(2) can transfer data from/to the memory or

from/to the User–2(1), by–passing the memory. During

read or write memory cycles processed by the User–1(2),

the User–2(1) have the possibility to listen the

transferred data.

2. Features

D Very Low Power CMOS

D 16–Bit operation with 6 or 8 Check Bits

D Fast Error Detection : 31 ns (max.)

D Fast Error Correction : 32 ns (max.)

D Corrects all Single–Bit Errors

D Detects all Double–Bit Errors

D Detects some Multi–Bit Errors

D Detects Chip Errors (x1, x4 & x8 RAM Format)

D Correctable and Uncorrectable Error Flags

D Two User Data Buses

D User to User Transfer and Listening operation

D High Drive Capability on Buses : –12.8 mA

D TTL Compatible

D Single 5V ±10% Power Supply

D 100 Pin Multilayer Quad Flat Pack

(Flat leaded or L leaded).

Atmel Corporation

Rev. D (09 Dec. 97)

1

1 page

29C516E

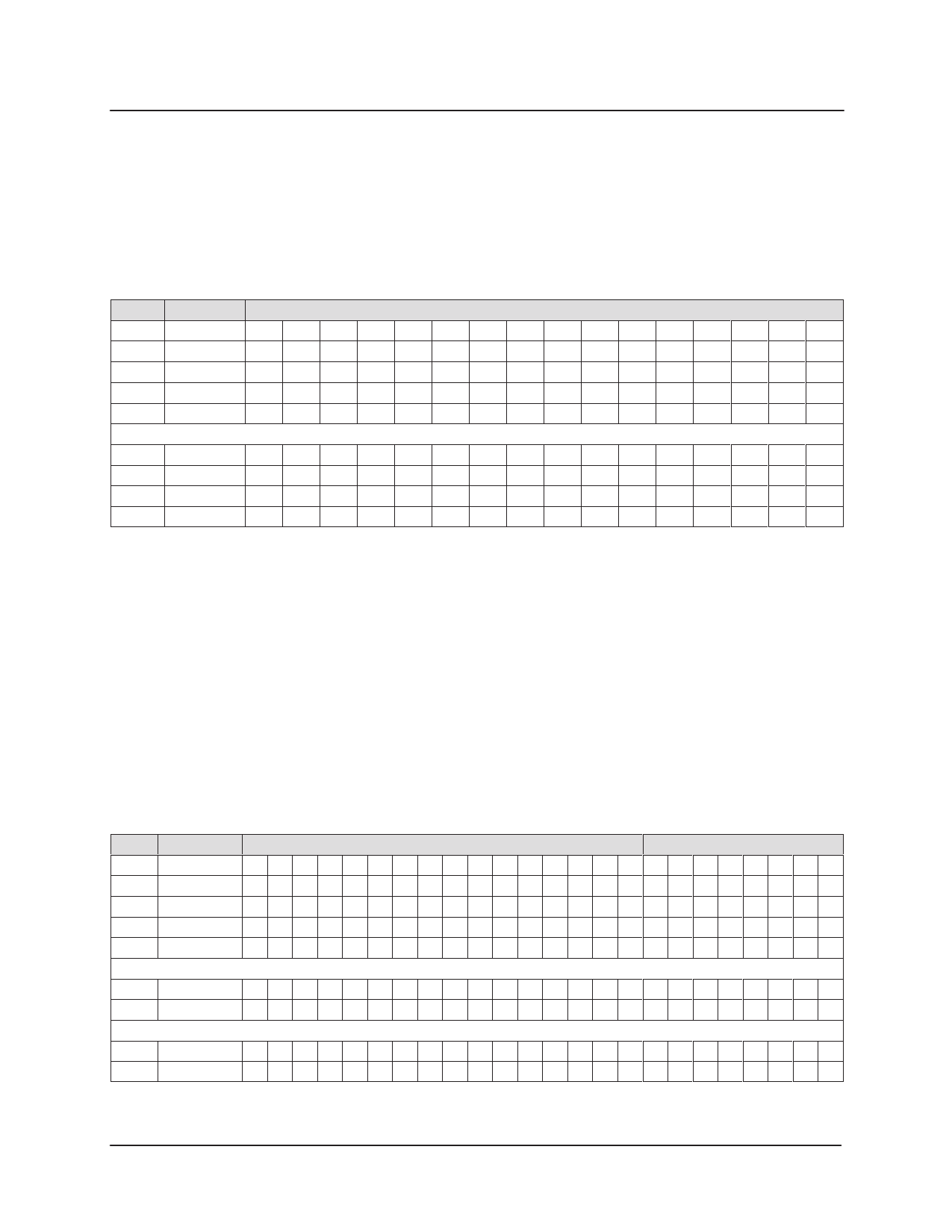

4. Check–Bit Generation

The Check–bit Generator produces 8 check–bits

(whatever N22 value) from the incoming User Data Word

UxD[0..15] according the Table 2.

Example: to create check–bit 0, bit 13, 12, 8, 7, 6, 5, 4 and

0 of the Data Word are XORed together.

If memory devices 8–bit wide are used, 24 bits

(MD[0..15] & MC[0..7]) are stored to give error

detection. But if memory devices 1–bit or 4–bit wide are

used, 22 bits (MD[0..15] & MC[0..5]) are stored to give

error detection.

Table 2: Check Bit Generation (indicates a bit of UxD bus used in the XOR/NXOR)

MC[..]

PARITY

UxD[..]

15 14 13 12 11 10

9

8

7

6

5

4

3

2

1

0

0 Even(XOR)

xx

xxxxx

x

1 Even(XOR)

x

xxxx x x

x

2 Odd(NXOR) x x x

x xxxx

3 Odd(NXOR)

xx

x

xxxxx

4

Even(XOR)

x

xxxxx

x

x

5

Even(XOR)

x

x

x

x

x

xx

x

6 Even(XOR)

xx

xx

xx

xx

7 Odd(NXOR) x

xxx

x xxx

5. Syndrome Generation

The syndrome Generator produces 8 syndrome–bits

(whatever N22 value) from the incoming Memory Data

Word MD[0..15] and the associated Check–bits MC[0..7]

(or MC[0..5]) according the Table 3.

Syndrome–bit SY[x] is the XOR of the generated

Check–bit MC[x] with the generation of Chek–bit on

MD[..].

Example: to create syndrome–bit 3, first the bit 14,

13, 10, 4, 3, 2, 1 and 0 of the Data Word

(MD[14,13,10,4,3,2,1,0]) are NXORed. Then, the result

is XORed with the associated Check–bit (MC[3]) of the

Check–byte read in the same time as Data Word is

checked.

If the memory uses x8 devices, then the bits should be

physically divided as follows: MC[0..7], MD[0..7] and

MD[8..15] . For x4 organization, the bits should be

divided MC[0..2]+MC[6], MC[3..5]+MC[7], MD[0..3],

MD[4..7], MD[8..11] and MD[12..15].

Table 3: Syndrome Bit Generation (indicates a bit of MD and MC buses used in the XOR/NXOR)

SY[..]

0

1

2

3

PARITY

MD[..]

MC[..]

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 7 5 4 3 6 2 1 0

EVEN(XOR)

xx

xxxxx

x

x

EVEN(XOR)

x

xxxx x x

x

x

ODD(NXOR) x x x

x xxxx

x

ODD(NXOR)

xx

x

xxxxx

x

4 EVEN(XOR) x

xxxxx

x

5 EVEN(XOR) x x x x x

xx

x

x

x

x

6 EVEN(XOR)

7 ODD(NXOR) x

xx

xxx

xx

xx

xx

x xxx

x

x

Rev. D (09 Dec. 97)

5

5 Page

29C516E

9.3. User to User Transfer

The TRANS pin is driven at a low level to select this

mode. The external arbiter drives the U2/U1 pin and

Table 10:

dispatches the unidirectional commands RD/WRx,

MEMx and ENx.

Function

0 1 x x x UD1[0..15] = UD2[0..15]

11x

UD1[0..15] = H.Z

xxx

x0

00

0 1 x x x UD2[0..15] = UD1[0..15]

01x

UD2[0..15] = H.Z

xxx

x0

0 1 UD2[0..15] = UD1[0..15]

1 1 x UD2[0..15] = Η.Ζ

01xxx

x0

0 1 UD1[0..15] = UD2[0..15]

0 1 x UD1[0..15] = H.Z

x0

x : don’t care

CERR and NCERR are not valid

CORRECT and SYNCHK are not active

Rev. D (09 Dec. 97)

11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet 29C516E.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| 29C516E | 16 Bit Flow Through EDAC Error Detection And Correction unit | ATMEL Corporation |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |