|

|

PDF SAA1101 Data sheet ( Hoja de datos )

| Número de pieza | SAA1101 | |

| Descripción | Universal sync generator USG | |

| Fabricantes | Philips | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de SAA1101 (archivo pdf) en la parte inferior de esta página. Total 18 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

DATA SHEET

SAA1101

Universal sync generator (USG)

Product specification

File under Integrated Circuits, IC02

January 1990

1 page

Philips Semiconductors

Universal sync generator (USG)

Product specification

SAA1101

Lock modes

The USG offers four lock modes:

• Lock from the subcarrier

• Slow sync. lock, external Href

• Slow sync. lock, internal Href

• Fast sync. lock, internal Href

LOCK FROM SUBCARRIER

Lock from subcarrier to the line frequency for the above

mentioned TV systems is given below; the horizontal

frequency (fH) = 15.625 kHz for 625 line systems and

15.734264 kHz for 525 line systems.

subcarrier input is, in this case, used as an external

input for the horizontal reference, see Fig.3(d).

SELECTION OF LOCK MODE

Lock mode is selected using the inputs LM0 and LM1 as

illustrated in the Table below.

LM0

0

0

1

1

LM1

0

1

0

1

SELECTION

lock to subcarrier

slow sync. lock external Href

slow sync. lock internal Href

fast sync. lock internal Href

SECAM (1 and 2)

PALN

NTSC (1 and 2)

PALM

PAL B/G

282fH

229.2516fH

227.5fH

227.25fH

283.7516fH

These relationships are obtained by the use of a phase

locked loop and the internal programmed divider chain,

see Fig.3(a).

LOCK TO AN EXTERNAL SIGNAL SOURCE

The following methods can be used to lock to an external

signal source:

1. Sync. lock slow; the line frequency is locked to an

external signal. The line and frame information are

extracted from the external sync. signal and used

separately in the lock system. The line information is

used in a phase-locked loop where external and

internal line frequencies are compared by the same

phase detector as is used for the subcarrier lock. The

external frame information is compared with the

internal frame in a slow lock system; mismatch of

internal and external frames will result in the addition

or suppression of one line depending on the direction

of the fault. The maximum lock time for frame lock is

6.25 s, see Fig.3(b).

2. Sync. lock fast. A fast lock of frames is possible with a

frame reset which is extracted out of the incoming

external sync. signal, see Fig.3(c).

3. Sync. lock with external reference. Lock of an external

sync. signal to the line frequency with an external line

reference to make possible a shifted lock. The

January 1990

5

5 Page

CS

1st half

picture

CS

2nd half

picture

NTSC 1

(2)

CB

1st half

picture

2nd half

CB picture

VD

NTSC 1 + 2

(2)

BK

1st half

picture

BK

2nd half

picture

BK

1st half

picture

PAL−M

BK

2nd half

picture

BK

3rd half

picture

BK

4th half

picture

NTSC 2

(2)

CB

1st half

picture

CB

2nd half

picture

start half picture

tWCB

6H

9H

11H(1)

21H + tWCB

19H + tWCB

MGH197

(1) H = 1 horizontal scan.

(2) NTSC mode reset; the fourth half picture is identical to the second half picture for NTSC.

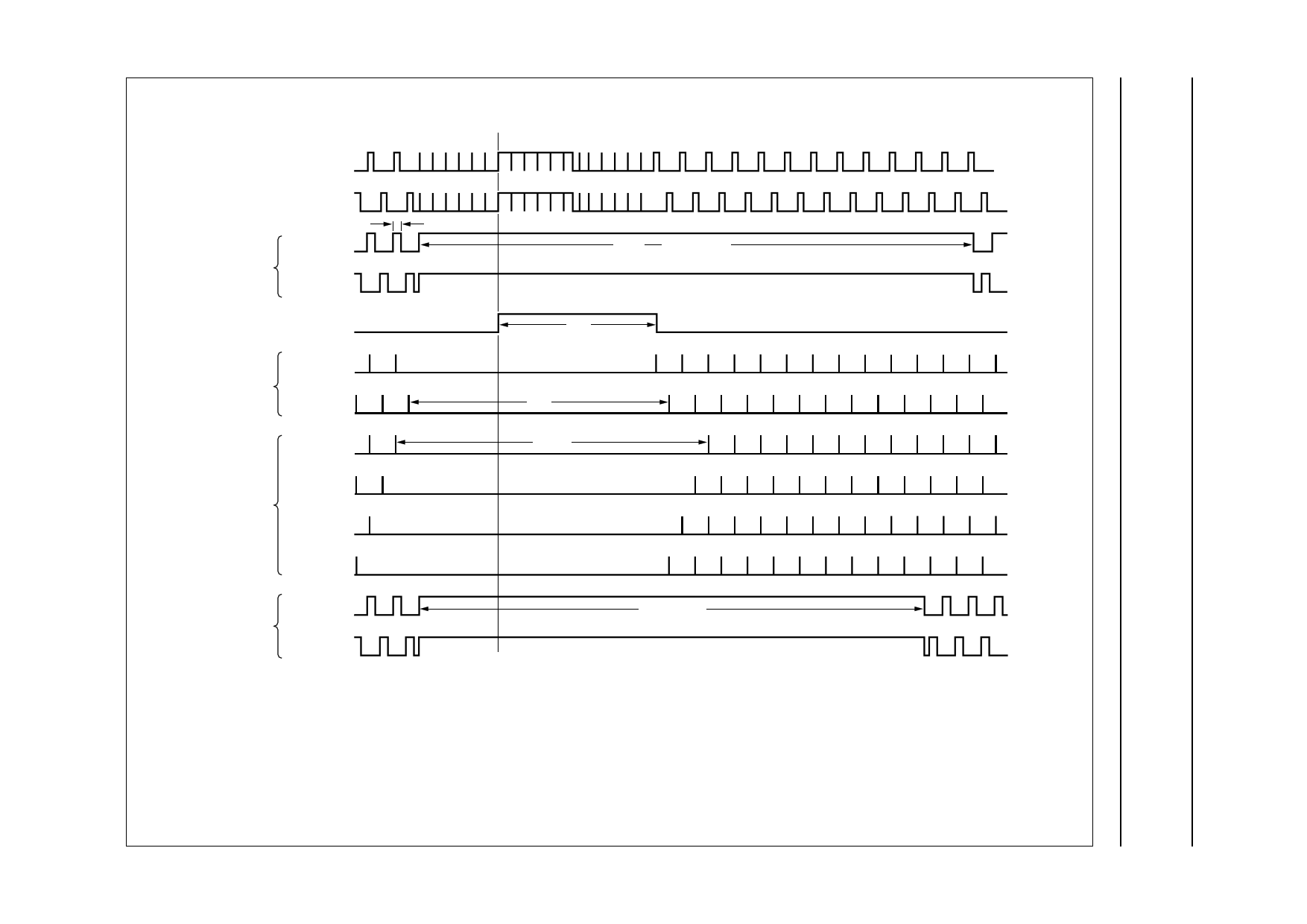

Fig.6 Typical output waveforms for NTSC and PAL-M. In the 524-line mode the output waveforms are identical to the first half picture of NTSC

and are not interlaced.

11 Page | ||

| Páginas | Total 18 Páginas | |

| PDF Descargar | [ Datasheet SAA1101.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SAA1101 | Universal sync generator USG | Philips |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |