|

|

PDF SA1630BE Data sheet ( Hoja de datos )

| Número de pieza | SA1630BE | |

| Descripción | IF quadrature transceiver | |

| Fabricantes | Philips | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de SA1630BE (archivo pdf) en la parte inferior de esta página. Total 22 Páginas | ||

|

No Preview Available !

INTEGRATED CIRCUITS

SA1630

IF quadrature transceiver

Product specification

IC17 Data Handbook

Philips

Semiconductors

1998 Jul 21

1 page

Philips Semiconductors

IF quadrature transceiver

Product specification

SA1630

ABSOLUTE MAXIMUM RATINGS

SYMBOL

PARAMETER

VCCXX

VIN

∆VG

PD

TJMAX

PMAX

TSTG

Supply voltages

Voltage applied to any other pin

Any GND pin to any other GND pin

Power dissipation, TA = 25°C (still air)

Maximum operating junction temperature

Maximum power input/output

Storage temperature range

RATING

-0.3 to +6.0

-0.3 to VCCXX+0.3

0

300

150

+20

–65 to +150

UNITS

V

V

V

mW

°C

dBm

°C

RECOMMENDED OPERATING CONDITIONS

SYMBOL

PARAMETER

VCCXXXX

VCCCP

TA

Supply voltages:

Charge pump supply voltage

Operating ambient temperature range

RATING

2.7 to 3.6

2.7 to 3.6

-40 to +85

UNITS

V

V

°C

NOTES:

1. There are no ESD protection diodes between pins 42, 43 and VCC to allow higher AC peak voltage. The ESD protection level has thus been

reduced. Proper ESD handling precautions should be followed.

MODE CONTROL

NO: PLL_ON

10

21

31

41

51

’0’ – LOGIC LOW

’1’ – LOGIC HIGH

’X’ – DON’T CARE

RX_ON

X

0

1

1

0

TX_ON

X

1

1

0

0

STATE DESCRIPTION

SLEEP mode

Synthesizer ON, Rx STDBY, Tx OFF

Synthesizer ON, Rx STDBY, Tx ON

Synthesizer ON, Rx ON, Tx OFF

Synthesizer ON, Rx OFF, Tx ON

MODE

SLEEP

WAIT

TRANSMIT

RECEIVE

TRANSMIT

2.5V REF

Off

Off

On

Off

Off

1. Sleep mode (PLL OFF, Rx OFF, Tx OFF)

In this mode everything is switched off except the 3–wire digital bus.

As long as the digital supply is still on, the programmed values are

active and the 3–wire bus will continue to be programmable.

2. Wait Mode (Tx Off, Rx Standby)

PLL is on. Receiver is in the reduced current standby mode and the

transmitter is completely switched off. This mode maybe useful if the

PLL is to be kept on and is waiting for a quick turn–on to either

transmit or receive modes, especially when Rx outputs are AC

coupled.

3. Transmit mode (Rx standby)

The PLL and transmitter are on. The receive section is in a reduced

current mode wherein most of the Rx circuitry is powered down

except for the bias and baseband circuits needed to hold the

baseband output voltages in the active state. This mode is useful if

the Rx baseband outputs are AC coupled via a large capacitor and

the application demands quick turn–on for the Rx, from Tx.

4. Receive Mode (Tx Off)

The Transmitter is completely shut–off. The PLL and receiver

sections are operating.

5. Transmit Mode (Rx OFF)

PLL and Transmit sections are on. However, the Receiver is

completely shut–down. This mode is useful if the Rx baseband

outputs are DC coupled to the external world.

1998 Jul 21

5

5 Page

Philips Semiconductors

IF quadrature transceiver

Product specification

SA1630

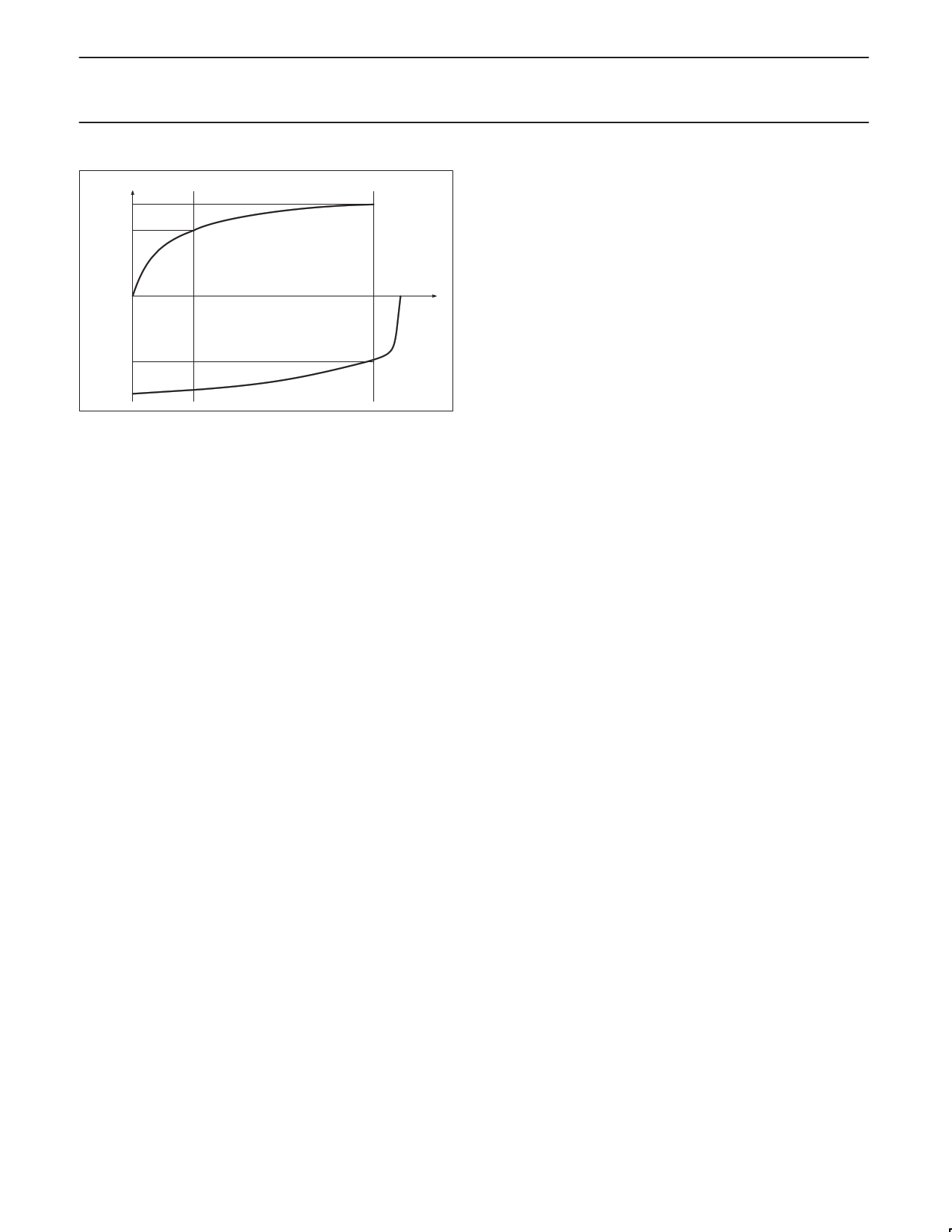

CURRENT

I2

I1

V1

VOLTAGE

V2

I2

I1 SR00526

Figure 3. Relative Output Current Variation

APPLICATION DESCRIPTION

General

The 1630 performs the IF modulator and demodulator functionality

for high–speed wireless data transceivers. The design is optimized

for IEEE 802.11 wireless LAN using 11 chips/symbol Direct

Sequence Spread Spectrum.

Transmitter

The IF quadrature transmitter baseband modulator input is driven

differentially by the D/A converters in the DSP chip. The baseband

signals are DC coupled for fast turn–on and turn–off and for

constant carrier testing. The typical common–mode input voltage is

VCC/2.

The open collector outputs of the mixers are biased by two

inductors, which are part of an LC tank. The LC tank matches the

output impedance of the mixers to the input impedance of the

upconverter chip (or any filter in between) and suppresses IF

harmonics.

An optional 2.5V reference is available during mode (3) and (5), the

transmit mode with Rx in standby. This reference can be enabled or

disabled via the 3 wire bus (in this mode). This voltage is provided

for use by an external current DAC if needed.

Receiver

The receiver part of the SA1630 consists of an IF Variable gain

amplifier, a quadrature demodulator and a pair of baseband

amplifiers. The IF amplifier has its gain controlled by the DSP chip.

This ensures linear operation of the receiver chain over a wide

dynamic range of input signals. Linear operation is essential for

resolving echo’s due to multipath reception.

The digital controlled AGC is meant for fast level training for the

receiver.

The high gain receiver, which is distributed between the IF and

baseband part facilitates interfacing with the RF front–end chip,

which normally have moderate gains (up to 20 dB), and SAW IF

filters, which mostly have considerable loss (up to 8 dB) without

external amplifiers.

The baseband amplifiers have a high drive capability (1 Vpp into

1kΩ, 15 pF for VCC = 3V) that facilitates direct interfacing to the A/D

converter without active external elements.

The baseband amplifiers can interface directly to the Track/Hold

switch/capacitor combination with capacitance values up to 15 pF.

When sampled at 22MHz the output can settle to within 1/4 LSB

when swinging 1V p–p.

The chip has a unique mode in which the Rx is on standby while the

Tx is ON. In this mode the Rx Baseband circuits are idling at

reduced currents and all Rx I/O outputs retain their DC bias

unchanged from their values when the Rx was fully ON. This mode

is very essential if ac coupling through a large capacitor, such as,

10nF is used. From this mode the chip can quickly be switched to

the Rx ON mode (Tx OFF) without worrying about

charging/discharging the large AC coupling capacitor.

The VGA can be programmed in 2 ways: 1) Directly programming

external control pins. 2) programming over the serial 3–wire bus.

The former method can switch gain in less than 200 ns.

The Rx baseband section also incorporates simple low pass active

filters of the Sallen key type. The Rx bandwidth is mainly set by

these filters. The function of these filters is twofold: 1) attenuate high

frequency signals from the Rx mixers. 2) act as anti–aliasing filters

for any A to D converters following this chip.

IF synthesizer

The SA1630 has an integrated synthesizer that uses an external

VCO operating on twice the IF frequency. It is internally divided by 2

for obtaining quadrature signals. The divided VCO signal is not

externally available. This minimizes the LO feedthrough to the IF

input port and hence minimizes output dc glitches when the IF gain

is switched.

The PLL reference clock is derived from the 22 MHz DSP clock. The

available divider ratios facilitate both 1 and 2 MHz phase

comparison frequency from a 22 MHz and an optional 44 MHz clock

respectively. In essence the reference divider will have

programmable dividers ratios of 8, 11, 22 and 44.

The VCO shall be fed from a stabilized supply. Such a stabilized

supply is necessary in order to prevent oscillator jitters due to Rx/Tx

switching. The effect of oscillator jitters is further minimized when

using a high PLL loop bandwidth, which on its turn requires a high

phase comparison frequency (1 MHz, preferably 2 MHz).

If the IF Synthesizer is not used, the CLKIN pins should be

terminated to ac ground.

Serial Programming Input

The serial input is a 3–wire input (CLOCK, STROBE, DATA) to

program the counter ratios, charge pump current, status– and

DC–offset register, mode select and test register. The programming

data is structured into two 21–bit words; each word includes 4 chip

address bits and 1 subaddress bit. Figure 2 shows the timing

diagram of the serial input. When the STROBE = L, the clock driver

is enabled and on the positive edges of the CLOCK the signal on

DATA input is clocked into a shift register. When the STROBE = H,

the clock is disabled and the data in the shift register remains stable.

Depending on the value of the subaddress bit the data is latched

into different working registers. Table 3 shows the contents of each

word.

Default States

Upon power up (VCCDIG is applied) a reset signal is generated,

which sets all registers to a default state. The logic level at the

1998 Jul 21

11

11 Page | ||

| Páginas | Total 22 Páginas | |

| PDF Descargar | [ Datasheet SA1630BE.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SA1630BE | IF quadrature transceiver | Philips |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |