|

|

PDF MAX1446EHJ Data sheet ( Hoja de datos )

| Número de pieza | MAX1446EHJ | |

| Descripción | 10-Bit / 60Msps / 3.0V / Low-Power ADC with Internal Reference | |

| Fabricantes | Maxim Integrated | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX1446EHJ (archivo pdf) en la parte inferior de esta página. Total 16 Páginas | ||

|

No Preview Available !

19-1729; Rev 1; 7/03

EVAALVUAAILTAIOBNLEKIT

10-Bit, 60Msps, 3.0V, Low-Power

ADC with Internal Reference

General Description

The MAX1446 10-bit, 3V analog-to-digital converter

(ADC) features a fully differential input, a pipelined 10-

stage ADC architecture with digital error correction and

wideband track and hold (T/H) incorporating a fully dif-

ferential signal path. This ADC is optimized for low-

power, high dynamic performance applications in

imaging and digital communications. The MAX1446

operates from a single 2.7V to 3.6V supply, consuming

only 90mW while delivering a 59.5dB signal-to-noise

ratio (SNR) at a 20MHz input frequency. The fully differ-

ential input stage has a 400MHz, -3dB bandwidth and

may be operated with single-ended inputs. In addition

to low operating power, the MAX1446 features a 5µA

power-down mode for idle periods.

An internal 2.048V precision bandgap reference is used

to set the ADC full-scale range. A flexible reference

structure allows the user to supply a buffered, direct or

externally derived reference for applications requiring

increased accuracy or a different input voltage range.

Lower and higher speed, pin-compatible versions of

the MAX1446 are also available. Refer to the MAX1444

data sheet for a 40Msps version and the MAX1448 data

sheet for a 80Msps version.

The MAX1446 has parallel, offset binary, three-state

outputs that can be operated from 1.7V to 3.3V to allow

flexible interfacing. The device is available in a 5x5mm,

32-pin TQFP package and is specified over the extended

industrial (-40°C to +85°C) temperature range.

Features

o Single 3.0V Operation

o Excellent Dynamic Performance

59.5dB SNR at fIN = 20MHz

73dB SFDR at fIN = 20MHz

o Low Power:

30mA (Normal Operation)

5µA (Shutdown Mode)

o Fully Differential Analog Input

o Wide 2Vp-p Differential Input Voltage Range

o 400MHz -3dB Input Bandwidth

o On-Chip 2.048V Precision Bandgap Reference

o CMOS-Compatible Three-State Outputs

o 32-Pin TQFP Package

PART

MAX1446EHJ

Ordering Information

TEMP RANGE

-40°C to +85°C

PIN-PACKAGE

32 TQFP

Functional Diagram

________________________Applications

Ultrasound Imaging

CCD Imaging

Baseband and IF Digitization

Digital Set-Top Boxes

Video Digitizing Applications

CLK

IN+

T/H

IN-

PD REF

CONTROL

PIPELINE ADC

REF SYSTEM +

BIAS

MAX1446

VDD

GND

D

E

C

10

OUTPUT

DRIVERS

D9–D0

OVDD

OGND

REFOUT REFIN REFP COM REFN

OE

________________________________________________________________ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

1 page

10-Bit, 60Msps, 3.0V, Low-Power

ADC with Internal Reference

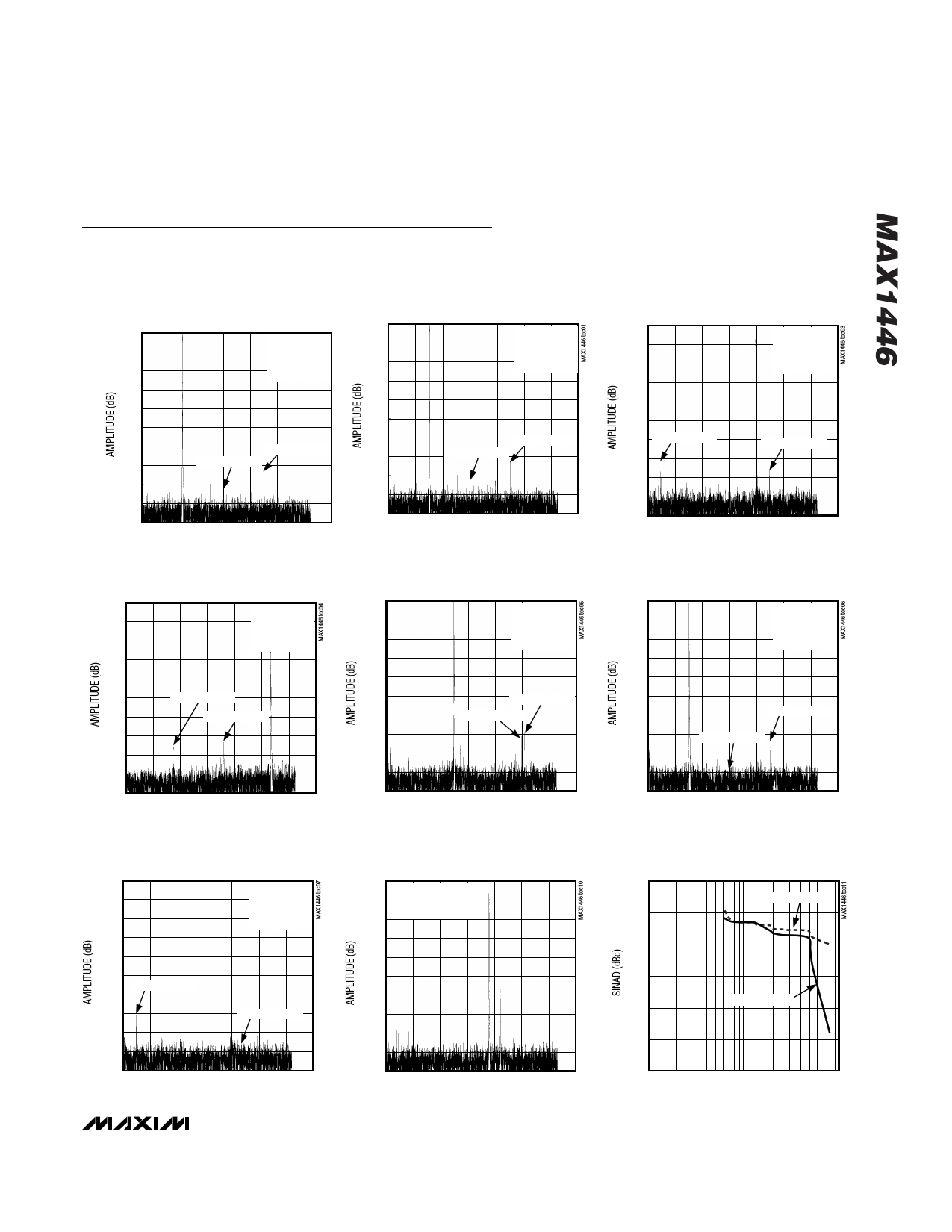

Typical Operating Characteristics

(VDD = 3.0V, OVDD = 2.7V, internal reference, differential input at -0.5dBFS, fCLK = 62.35MHz, CL ≈ 10pF, TA = +25°C,

unless otherwise noted.)

FFT PLOT

fIN = 7.5MHz, 8192-POINT FFT,

DIFFERENTIAL INPUT

0 SFDR = 72.2dB

-10 SNR = 60.1dB

THD = -71.5dB

-20 SINAD = 59.8dB

-30

-40

-50

-60 3RD HARMONIC

-70 2ND HARMONIC

-80

-90

-100

0

5 10 15 20 25 30

ANALOG INPUT FREQUENCY (MHz)

FFT PLOT

(fIN = 26.8MHz, 8192-POINT FFT,

DIFFERENTIAL INPUT)

0 SINAD = 59.0dB

-10 SNR = 59.4dB

THD = -70.5dBc

-20 SFDR = 72.9dBc

-30

35

-40

-50 2ND HARMONIC

-60 3RD HARMONIC

-70

-80

-90

-100

0

5 10 15 20 25 30 35

ANALOG INPUT FREQUENCY (MHz)

FFT PLOT

(fIN = 20MHz, 8192-POINT FFT,

SINGLE-ENDED INPUT)

0 SINAD = 59.2dB

-10 SNR = 59.5dB

THD = -70.7dBc

-20 SFDR = 71.1dBc

-30

-40

-50

3RD HARMONIC

-60

-70 2ND HARMONIC

-80

-90

-100

0

5 10 15 20 25 30 35

ANALOG INPUT FREQUENCY (MHz)

FFT PLOT

(fIN = 7.5MHz, 8192-POINT FFT,

DIFFERENTIAL INPUT)

0 SFDR = 72.2dBc

-10 SNR = 60.1dB

THD = -71.5dBc

-20 SINAD = 59.8dB

-30

-40

-50

-60 3RD HARMONIC

-70 2ND HARMONIC

-80

-90

-100

0

0

-10

-20

-30

5 10 15 20 25 30 35

ANALOG INPUT FREQUENCY (MHz)

FFT PLOT

(fIN = 50MHz, 8192-POINT FFT,

DIFFERENTIAL INPUT)

SFDR = 70dBc

SNR = 59.1dB

THD = -67.1dBc

SINAD = 58.5dB

-40

-50 3RD HARMONIC

-60 2ND HARMONIC

-70

-80

-90

-100

0

5 10 15 20 25 30 35

ANALOG INPUT FREQUENCY (MHz)

TWO-TONE INTERMODULATION

(8192-POINT IMD,

DIFFERENTIAL INPUT)

0 f1 = 19MHz AT -6.5dBFS

-10 f2 = 21MHz AT -6.5dBFS

3RD IMD = -76dBc

-20

-30

-40

-50

-60

-70

-80

-90

-100

0

5 10 15 20 25 30 35

ANALOG INPUT FREQUENCY (MHz)

FFT PLOT

(fIN = 20MHz, 8192-POINT FFT,

DIFFERENTIAL INPUT)

0 SINAD = 59.3dB

-10 SNR = 59.6dB

THD = -70.7dBc

-20 SFDR = 72.2dBc

-30

-40

-50

-60 3RD HARMONIC

-70

2ND HARMONIC

-80

-90

-100

0

0

-10

-20

-30

5 10 15 20 25 30 35

ANALOG INPUT FREQUENCY (MHz)

FFT PLOT

(fIN = 7.5MHz, 8192-POINT FFT,

SINGLE-ENDED INPUT)

SINAD = 59.5dB

SNR = 59.7dB

THD = -73.0dBc

SFDR = 73.6dBc

-40

-50

-60 3RD HARMONIC

-70 2ND HARMONIC

-80

-90

-100

0

5 10 15 20 25 30 35

ANALOG INPUT FREQUENCY (MHz)

SPURIOUS-FREE DYNAMIC RANGE

vs. ANALOG INPUT FREQUENCY

80

DIFFERENTIAL

75

70

65

SINGLE ENDED

60

55

50

1

10

ANALOG INPUT FREQUENCY (MHz)

100

_______________________________________________________________________________________ 5

5 Page

10-Bit, 60Msps, 3.0V, Low-Power

ADC with Internal Reference

The MAX1446 provides three modes of reference oper-

ation:

• Internal reference mode

• Buffered external reference mode

• Unbuffered external reference mode

In internal reference mode, the internal reference out-

put (REFOUT) can be tied to the REFIN pin through a

resistor (e.g., 10kΩ) or resistor-divider if an application

requires a reduced full-scale range. For stability pur-

poses, it is recommended to bypass REFIN with a

>10nF capacitor to GND.

In buffered external reference mode, the reference volt-

age levels can be adjusted externally by applying a

stable and accurate voltage at REFIN. In this mode,

REFOUT may be left open or connected to REFIN

through a >10kΩ resistor.

In unbuffered external reference mode, REFIN is con-

nected to GND, thereby deactivating the on-chip

buffers of REFP, COM, and REFN. With their buffers

shut down, these pins become high impedance and

can be driven by external reference sources.

Clock Input (CLK)

The MAX1446 CLK input accepts CMOS-compatible

clock signals. Since the interstage conversion of the

device depends on the repeatability of the rising and

falling edges of the external clock, use a clock with low

jitter and fast rise and fall times (<2ns). In particular,

sampling occurs on the falling edge of the clock signal,

mandating this edge to provide lowest possible jitter.

Any significant aperture jitter would limit the SNR per-

formance of the ADC as follows:

SNR = 20log (1 / 2πfINtAJ)

where fIN represents the analog input frequency, and

tAJ is the time of the aperture jitter.

Clock jitter is especially critical for undersampling

applications. The clock input should always be consid-

ered as an analog input and routed away from any ana-

log input or other digital signal lines.

The MAX1446 clock input operates with a voltage

threshold set to VDD/2. Clock inputs with a duty cycle

other than 50% must meet the specifications for high

and low periods as stated in the Electrical Character-

istics. See Figures 3a, 3b, 4a, and 4b for the relation-

ship between spurious-free dynamic range (SFDR),

signal-to-noise ratio (SNR), total harmonic distortion

(THD), or signal-to-noise plus distortion (SINAD) versus

duty cycle.

Output Enable (OE), Power-Down (PD),

and Output Data (D0–D9)

All data outputs, D0 (LSB) through D9 (MSB), are

TTL/CMOS-logic compatible. There is a 5.5 clock-cycle

latency between any particular sample and its valid

output data. The output coding is straight offset binary

(Table 1). With OE and PD (power-down) high, the digi-

tal output enters a high-impedance state. If OE is held

low with PD high, the outputs are latched at the last

value prior to the power-down.

The capacitive load on the digital outputs D0–D9

should be kept as low as possible (<15pF) to avoid

large digital currents that could feed back into the ana-

log portion of the MAX1446, degrading its dynamic per-

formance. The use of buffers on the ADC’s digital

outputs can further isolate the digital outputs from

heavy capacitive loads.

To further improve the dynamic performance of the

MAX1446 small series resistors (e.g. 100Ω) may be

added to the digital output paths, close to the ADC.

Figure 5 displays the timing relationship between out-

put enable and data output valid, as well as power-

down/wake-up and data output valid.

System Timing Requirements

Figure 6 shows the relationship between the clock

input, analog input, and data output. The MAX1446

samples at the falling edge of the input clock. Output

data is valid on the rising edge of the input clock. The

output data has an internal latency of 5.5 clock cycles.

Table 1. MAX1446 Output Code for Differential Inputs

DIFFERENTIAL INPUT VOLTAGE*

VREF × 511/512

VREF × 510/512

VREF × 1/512

0

- VREF × 1/512

- VREF × 511/512

- VREF × 512/512

DIFFERENTIAL INPUT

+Full Scale -1LSB

+Full Scale -2LSB

+1LSB

Bipolar Zero

-1LSB

Negative Full Scale + 1LSB

Negative Full Scale

STRAIGHT OFFSET BINARY

11 1111 1111

11 1111 1110

10 0000 0001

10 0000 0000

01 1111 1111

00 0000 0001

00 0000 0000

*VREFIN = VREFP = VREFN

______________________________________________________________________________________ 11

11 Page | ||

| Páginas | Total 16 Páginas | |

| PDF Descargar | [ Datasheet MAX1446EHJ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX1446EHJ | 10-Bit / 60Msps / 3.0V / Low-Power ADC with Internal Reference | Maxim Integrated |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |