|

|

PDF M378T3354BG Data sheet ( Hoja de datos )

| Número de pieza | M378T3354BG | |

| Descripción | DDR2 Unbuffered SDRAM MODULE | |

| Fabricantes | Samsung | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de M378T3354BG (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

256MB,512MB,1GB Unbuffered DIMMs

DDR2 SDRAM

DDR2 Unbuffered SDRAM MODULE

240pin Unbuffered Module based on 512Mb B-die

64/72-bit Non-ECC/ECC

Revision 1.2

January 2005

Rev. 1.2 Jan. 2005

1 page

256MB,512MB,1GB Unbuffered DIMMs

DDR2 SDRAM

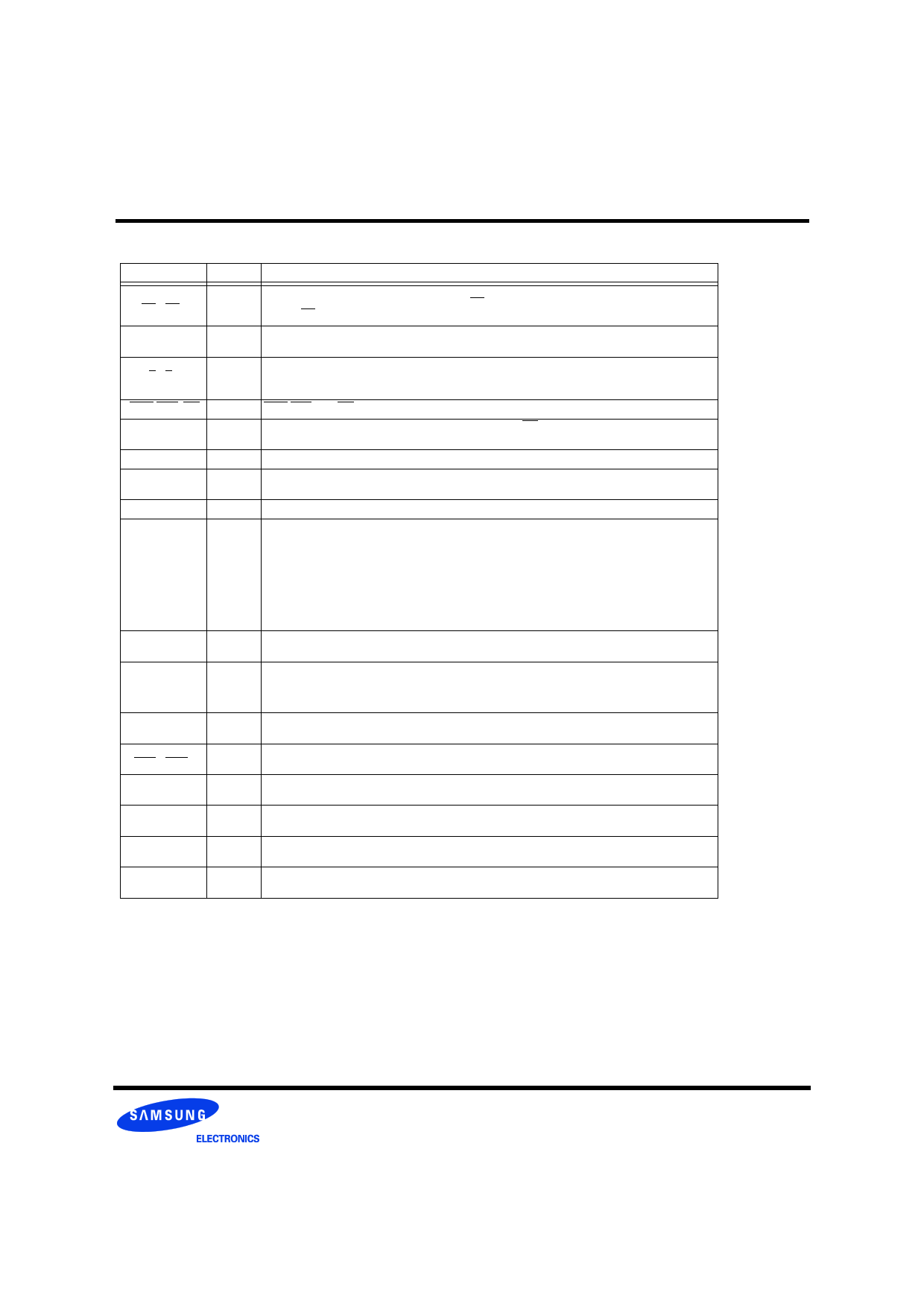

Input/Output Functional Description

Symbol

CK0-CK2

CK0-CK2

CKE0-CKE1

S0-S1

RAS, CAS, WE

ODT0-ODT1

VREF

VDDQ

BA0-BA1

A0-A13

DQ0-DQ63

CB0-CB7

DM0-DM8

VDD,VSS

DQS0-DQS8

DQS0-DQS8

SA0-SA2

SDA

SCL

VDD SPD

Type

Input

Input

Input

Input

Input

Supply

Supply

Input

Function

CK and CK are differential clock inputs. All the SDRAM addr/cntl inputs are sampled on the crossing

of positive edge of CK and negative edge of CK. Output (read) data is reference to the crossing of

CK and CK (Both directions of crossing)

Activates the SDRAM CK signal when high and deactivates the CK Signal When low. By deactivat-

ing the clocks, CKE low initiates the Powe Down mode, or the Self-Refresh mode

Enables the associated SDRAM command decoder when low and disables the command decoder

when high. When the command decoder is disbled, new command are ignored but previous opera-

tions continue. This signal provides for external rank selection on systems with multiple ranks

RAS, CAS, and WE (ALONG WITH CS) define the command being entered.

When high, termination resistance is enabled for all DQ, DQ and DM pins, assuming the function is

enabled in the Extended Mode Register Set (EMRS).

Reference voltage for SSTL 18 inputs.

Power supply for the DDR II SDRAM output buffers to provide improved noise immunity. For all cur-

rent DDR2 unbuffered DIMM designs, VDDQ shares the same power plane as VDD pins.

Selects which SDRAM BANK of four is activated.

During a Bank Activate command cycle, Address input defines the row address (RA0-RA13)

Input

During a Read or Write command cycle, Address input defines the colum address, In addition to the

column address, AP is used to invoke autoprecharge operation at the end of the burst read or write

cycle. If AP is high, autoprecharge is selected and BA0, BA1 defines the bank to be precharged. If

AP is low, autoprecharge is disbled. During a precharge command cycle, AP is used in conjunction

with BA0, BA1 to control which bank(s) to precharge. If AP is high, all banks will be precharged

regardless of the state of BA0, BA1. If AP is low, BA0, BA1are used to define which bank to pre-

charge.

In/Out Data and Check Bit Input/Output pins.

Input

Supply

In/Out

Input

In/Out

Input

Supply

DM is an input mask signal for write data. Input data is masked when DM is sampled High coincident

with that input data during a write access. DM is sampled on both edges of DQS. Although DM pins

are input only, the DM loading matches the DQ and DQS loading.

Power and ground for DDR2 SDRAM input buffers, and core logic. VDD and VDDQ pins are tied to

VDD/VDDQ planes on these modules.

Data strobe for input and output data. For Rawcards using x16 orginized DRAMs DQ0-7 connect to

the LDQS pin of the DRAMs and DQ8-17 connect to the UDQS pin of the DRAM

These signals and tied at the system planar to either VSS or VDD to configure the serial SPD EER-

POM address range.

This bidirectional pin is used to transfer data into or out of the SPD EEPROM. A resistor must be

connected from the SDA bus line to VDD to act as a pullup on the system board.

This signal is used to clock data into and out of the SPD EEPROM. A resistor may be connected

from the SCL bus time to VDD to act as a pullup onthe system board.

Power supply for SPD EEPROM. This supply is separate from the VDD/VDDQ power plane.

EEPROM supply is operable from 1.7V to 3.6V.

Rev. 1.2 Jan. 2005

5 Page

256MB,512MB,1GB Unbuffered DIMMs

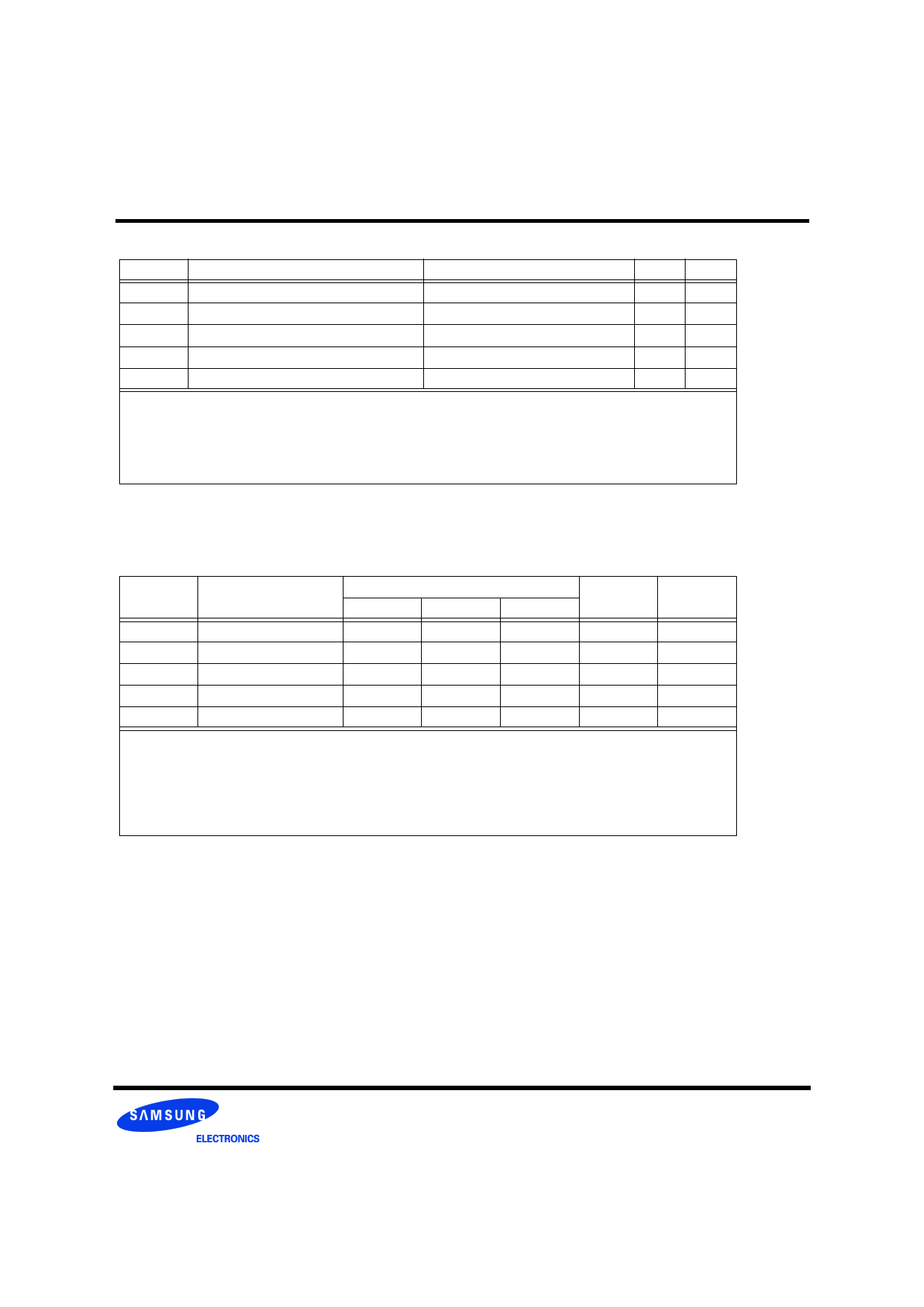

Absolute Maximum DC Ratings

DDR2 SDRAM

Symbol

VDD

VDDQ

VDDL

VIN, VOUT

TSTG

Parameter

Voltage on VDD pin relative to Vss

Voltage on VDDQ pin relative to Vss

Voltage on VDDL pin relative to Vss

Voltage on any pin relative to Vss

Storage Temperature

Rating

- 1.0 V ~ 2.3 V

- 0.5 V ~ 2.3 V

- 0.5 V ~ 2.3 V

- 0.5 V ~ 2.3 V

-55 to +100

Units

V

V

V

V

°C

Notes

1

1

1

1

1, 2

1. Stresses greater than those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. This is a

stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational

sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reli-

ability.

2. Storage Temperature is the case surface temperature on the center/top side of the DRAM. For the measurement conditions, please

refer to JESD51-2 standard.

AC & DC Operating Conditions

Recommended DC Operating Conditions (SSTL - 1.8)

Symbol

Parameter

VDD

VDDL

VDDQ

VREF

VTT

Supply Voltage

Supply Voltage for DLL

Supply Voltage for Output

Input Reference Voltage

Termination Voltage

Min.

1.7

1.7

1.7

0.49*VDDQ

VREF-0.04

Rating

Typ.

1.8

1.8

1.8

0.50*VDDQ

VREF

Max.

1.9

1.9

1.9

0.51*VDDQ

VREF+0.04

Units

V

V

V

mV

V

Notes

4

4

1,2

3

There is no specific device VDD supply voltage requirement for SSTL-1.8 compliance. However under all conditions VDDQ must

be less than or equal to VDD.

1. The value of VREF may be selected by the user to provide optimum noise margin in the system. Typically the value of VREF is

expected to be about 0.5 x VDDQ of the transmitting device and VREF is expected to track variations in VDDQ.

2. Peak to peak AC noise on VREF may not exceed +/-2% VREF(DC).

3. VTT of transmitting device must track VREF of receiving device.

4. AC parameters are measured with VDD, VDDQ and VDDDL tied together.

Rev. 1.2 Jan. 2005

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet M378T3354BG.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| M378T3354BG | DDR2 Unbuffered SDRAM MODULE | Samsung |

| M378T3354BG0-CC | DDR2 Unbuffered SDRAM MODULE | Samsung |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |